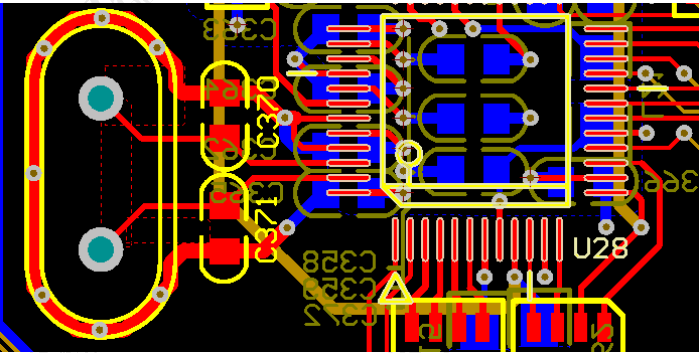

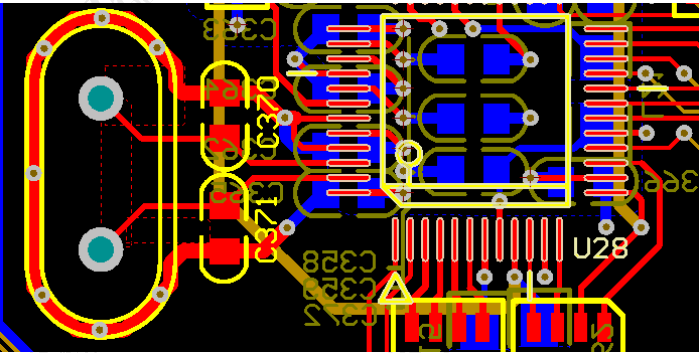

布局要求:

1、布局整体紧凑,一般放置在主控的同一侧,靠近主控IC。

2、布局是尽量使电容分支要短(目的:减小寄生电容,)

3、晶振电路一般采用π型滤波形式,放置在晶振的前面。

布线要求:

1)走线采取类差分走线;

2)晶体走线需加粗处理:8-12mil,晶振按照普通单端阻抗线走线即可;

3)对信号采取包地处理,每隔50mil放置一个屏蔽地过孔。

4)晶体晶振本体下方所有层原则上不准许走线,特别是关键信号线。(晶体晶振为干扰源)。

5)不准许出现stub线头,防止天线效应,出现额外的干扰。

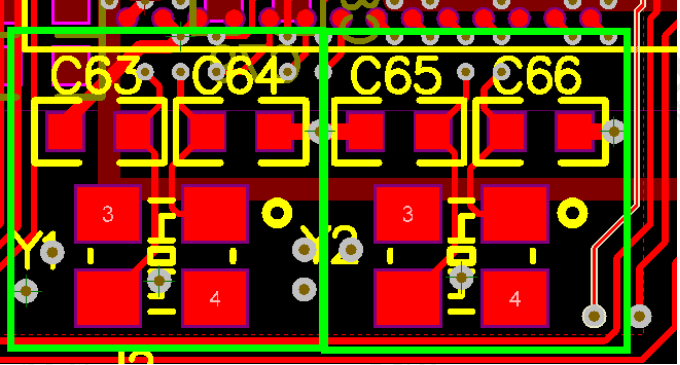

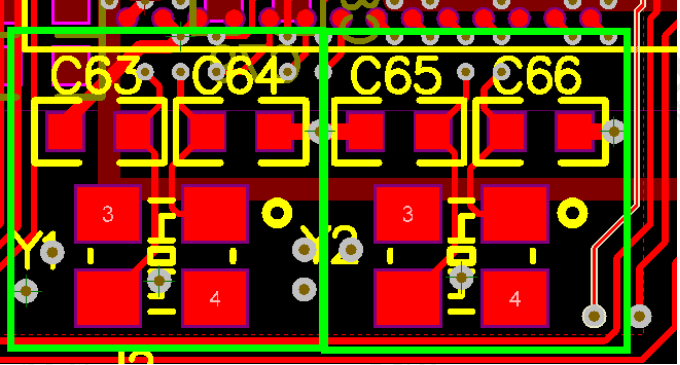

布局要求:

1、布局整体紧凑,一般放置在主控的同一侧,靠近主控IC。

2、布局是尽量使电容分支要短(目的:减小寄生电容,)

3、晶振电路一般采用π型滤波形式,放置在晶振的前面。

布线要求:

1)走线采取类差分走线;

2)晶体走线需加粗处理:8-12mil,晶振按照普通单端阻抗线走线即可;

3)对信号采取包地处理,每隔50mil放置一个屏蔽地过孔。

4)晶体晶振本体下方所有层原则上不准许走线,特别是关键信号线。(晶体晶振为干扰源)。

5)不准许出现stub线头,防止天线效应,出现额外的干扰。