答:PCB设计中有一些信号组需要进行等长处理,以保证组内信号时序要求。

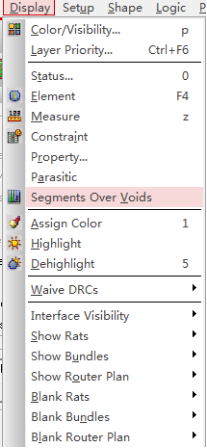

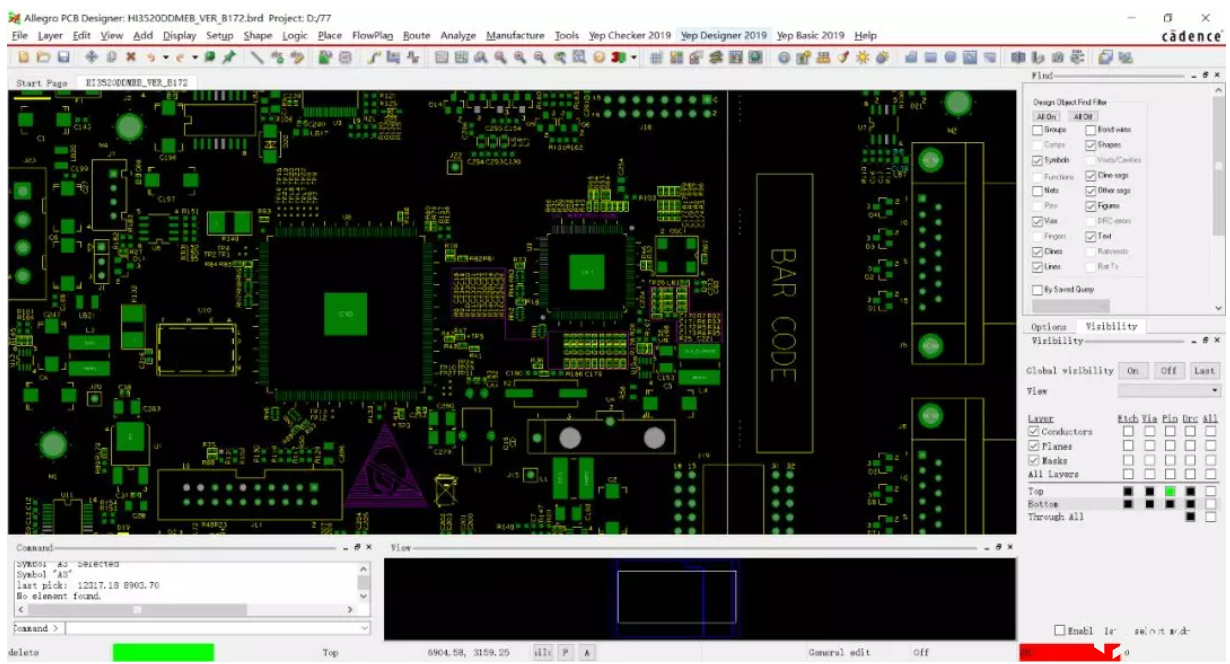

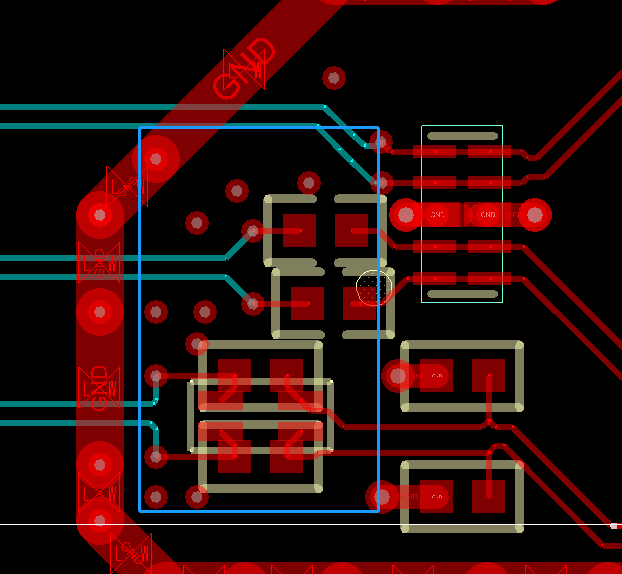

第一步,点击Setup-Constraints-Constraint Manager选项,调出规则管理器,如图6-269所示;

图6-269 调出规则管理器

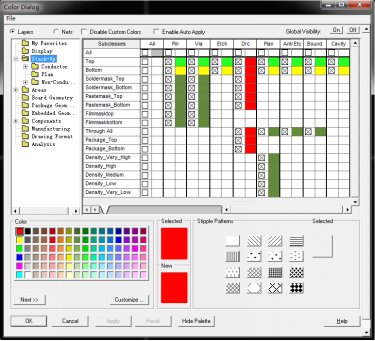

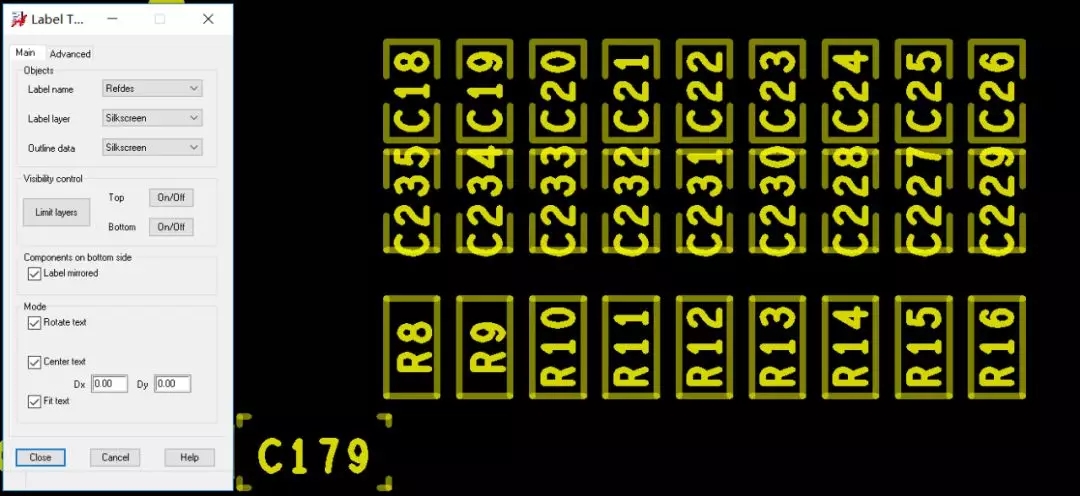

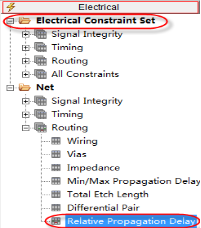

第二步,在弹出的界面上,打开Electrical-Net-Routing-Relative Propagation Delay,如图6-270所示;

图6-270 调用电气规则管理器

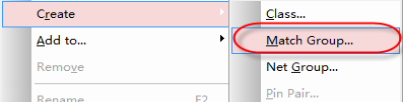

第三步,在右侧选择需要做等长的信号线,按Shift或者Ctrl可以进行多选。选好后右击,选择Create-Match Group,建立走线长度匹配组,如图6-271所示;

图6-271 建立匹配组

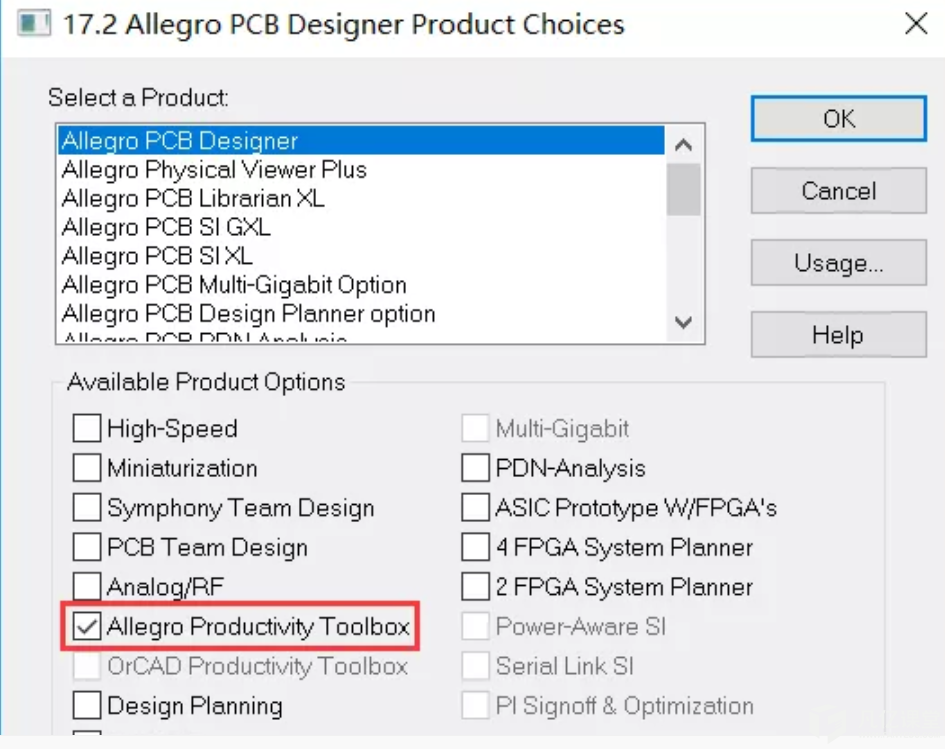

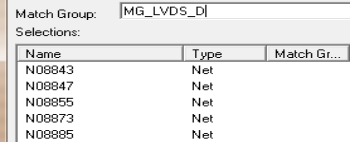

第四步,在弹出的对话框中输入匹配组的名称,然后点击OK退出,如图6-272所示;

图6-272 匹配组命名图示

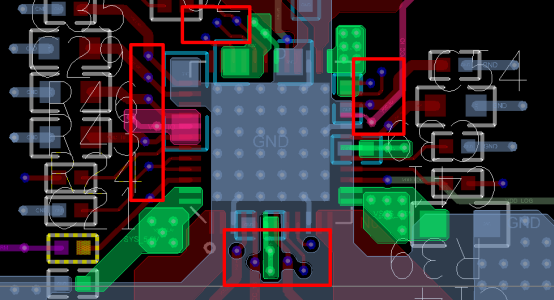

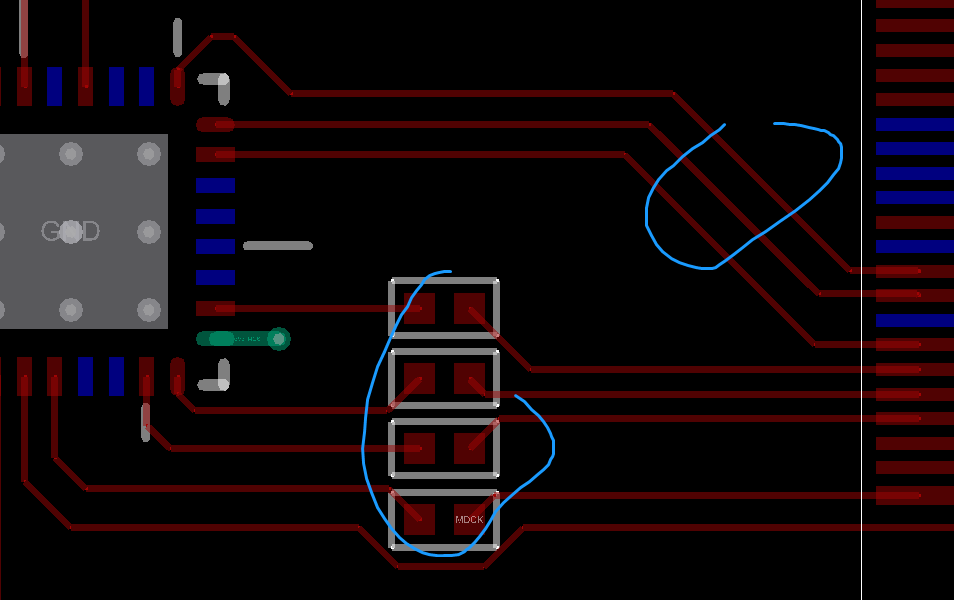

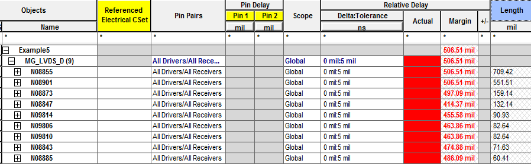

第五步,建立好匹配组后,选择相应的组右击,然后点击Analyze选项,分析匹配组内的信号长度,长度值会在Length这一栏显示出来,如图6-273所示;

图6-273 分析信号长度

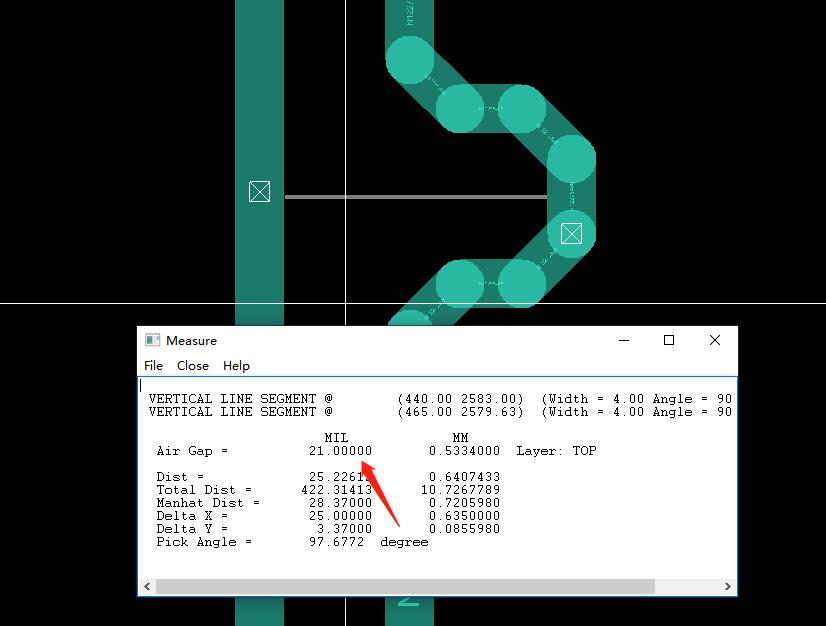

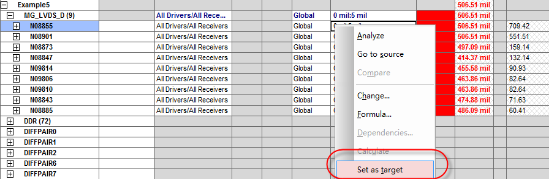

第六步,分析完成后,设置好相应的等长误差(如0mil到5mil),然后找到长度值最长信号,右击选择Set as target,将最长的信号值设置为目标信号,如图6-274所示;

图6-274 设置目标信号

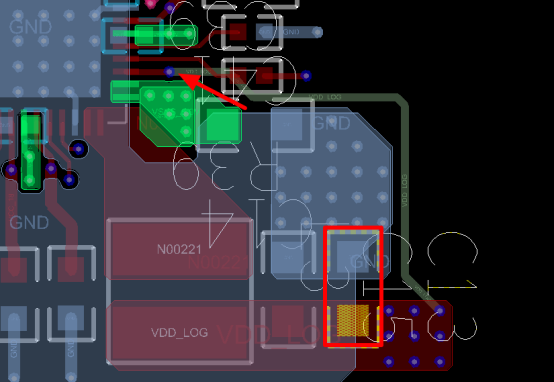

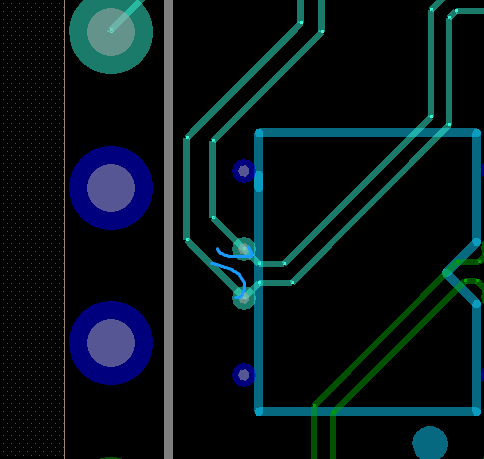

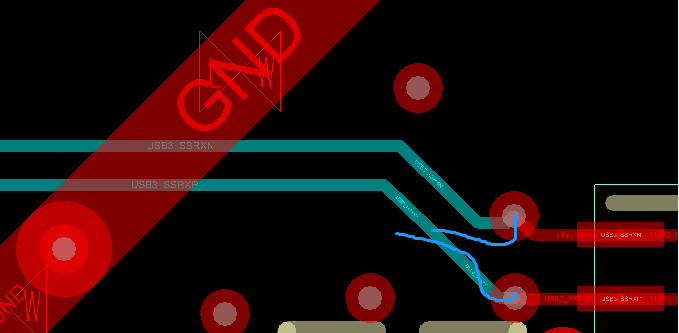

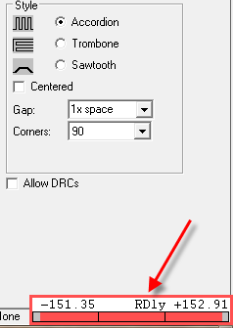

第七步,设置好以后,关闭规则管理器,在PCB设计界面中执行Route-Delay Tune选项,在Options选项卡中设置好蛇形走线的类型、间距、角度等参数,即可开始蛇形等长处理,处理的时候右下角在RDly长度显示,如果长度在设置的匹配组范围内,即为绿色显示,如图6-275所示。

图6-275 蛇形走线进度条显示效果

扫码关注

扫码关注