FPGA内部逻辑信号调试技术

随着芯片技术的迅速发展,可编程逻辑器件的功能日趋强大。FPGA作为可编程逻辑器件中的一种类型,其能实现的逻辑电路的复杂程度更是难以想象。当FPGA的对外输入输出逻辑功能与工程师的设计预期不一致时,需要通过FPGA内部逻辑信号调试来定位逻辑代码的问题所在。因此需要一种技术可以让工程师方便有效地采集到FPGA内部逻辑信号。本文分析两种FPGA内部逻辑信号调试技术的特点,并且介绍了一种FPGA内部逻辑信号调试技术的具体实现方法。该技术相比于现有的其它调试技术,效率更高,通用性更强。

1、现有FPGA内部逻辑信号调试技术分析

在实际调试时 主要使用以下两种方式来采集FPGA内部逻辑信号进行调试。

1.1JTAG方式

此方式的原理是将逻辑分析内核嵌入到FPGA设计中调试时使用专用的软件和JTAG工具,通过FPGA芯片的JTAG端口

进行调试配置和信号采集。一般由FPGA芯片的原厂提供整体技术方案包括逻辑分析内核IP、JTAG工具和调试软件相应的技术有Altera的SignalTap、Xilinx的ChipScope等特点是使用方便上手门槛低。但是缺点是不通用,不同的芯片的厂家提供不同风格的解决方案。如果同一款产品使用了不同厂家的FPGA芯片,调试的风格则完全不同。另外,逻辑分析内核也会占用FPGA资源。当FPGA资源比较紧张时使用此类技术会受限制。

1.2信号引出方式

此方式的原理是将FPGA内部逻辑信号引出到FPGA的IO引脚上,然后使用逻辑分析仪采集相应的信号。特点是通用性和可移植性,并且占用非常少的FPGA资源。本文描述的调试技术属于该技术类型。

2、技术特点

在实际调试时,工程师通过采集和分析FPGA内部逻辑信号从而寻找出逻辑代码中缺陷。调试不同的功能模块时工程师可能需要采集不同的逻辑代码信号由于FPGA的IO引脚数量有限,所以无法将所有需要采集的逻辑信号都引出到FPGA的IO引脚上。本调试技术通过一个多路复用器实现了调试信号的可配置化切换,从而解决了以上问题并且显著地提高了调试效率。此外,本调试技术在实际应用时非常方便、便捷,在各种FPGA芯片上的兼容性也非常好。

3、实现原理

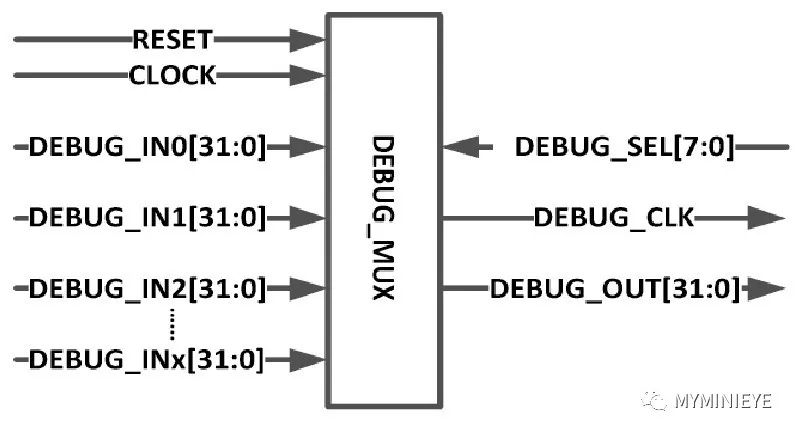

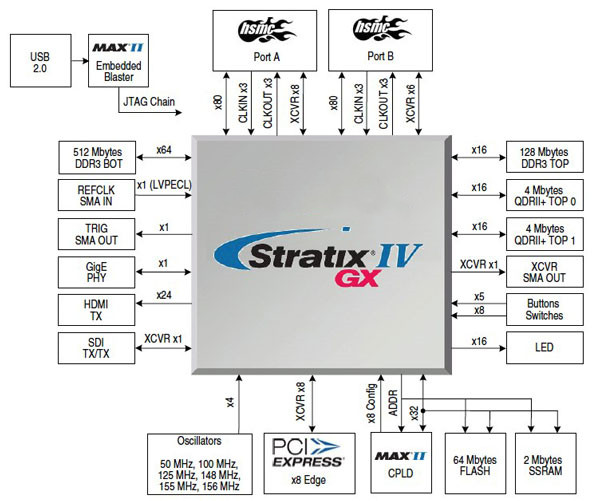

下文使用VHDL硬件描述语言实现了信号引出方式的FPGA内部逻辑信号调试技术。图1为内部逻辑信号多路复用器DEBUG_MUX组件。

上图中RESET为复位信号输入。CLOCK为时钟信号输入。

DEBUG_INx[31:0]为多组信号输入,每组最多支持32个信号。

DEBUG_SEL[7:0]为信号组选择输入最多支持256组信号的切换。

DEBUG_OUT[31:0]为信号输出最多,支持32个信号。DEBUG_CLK为时钟输出。

使用DEBUG_MUX组件时FPGA内部逻辑信号以分组的方式连接到DEBUG_INx[31:0],外部选择信号通过FPGA的输入IO引脚连接到DEBUG_SEL[7:0] 。DEBUG_OUT[31:0]和DEBUG_CLK

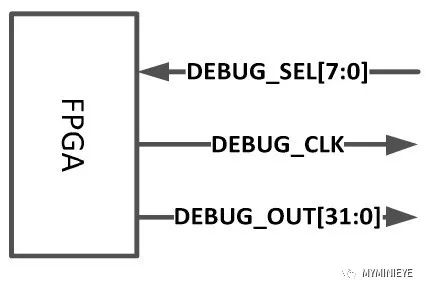

连接到FPGA的输出IO引脚。最终对外的逻辑信号调试接口如图2所示。

图2中DEBUG_SEL[7:0]为选择信号输入 DEBUG_OUT[31:0]为逻辑信号输出 DEBUG_CLK为同步时钟输出。调试时工程师通过DEBUG_SEL[7:0]选择需要采样的逻辑信号组然后将逻辑分析仪其连接至DEBUG_OUT[31:0]和DEBUG_CLK进行逻辑信号采样。

★ 烧脑步骤★

4、逻辑代码具体实现

4.1DEBUG_MUX组件定义

ENTITY DEBUG_MUX IS PORT(

RESET : IN STD_ULOGIC;

CLOCK : IN STD_ULOGIC;

DEBUG_IN0 : IN STD_ULOGIC_VECTOR(31 DOWNTO 0);

DEBUG_IN1 : IN STD_ULOGIC_VECTOR(31 DOWNTO 0);

DEBUG_CLK : OUT STD_ULOGIC;

DEBUG_OUT : OUT STD_ULOGIC_VECTOR(31 DOWNTO 0);

DEBUG-SEL:INSTD-ULOGIC-VECTOR(7 DOWNTO 0)

END ENTITY;

ARCHITECTURE RTL OF DEBUG_MUX IS

BEGIN

DEBUG-CLK<=CLOCK;

MUX-MAIN:PROCESS(CLOCK, RESET) IS

BEGIN

IF RESET = '1'THEN

DEBUG-OUT<=(OTHERS =>'0');

ELSIF RISING-EDGE(CLOCK) THEN

IF DEBUG-SEL= X″00″ THEN

DEBUG-OUT<= DEBUG-IN0;

ELSIF DEBUG_SEL = X″01″ THEN

DEBUG-OUT<= DEBUG-IN1;

ELSE

DEBUG-OUT<=(OTHERS =>'0');

END IF;

END IF;

END PROCESS;

END ARCHITECTURE;

以上代码实现DEBUG_MUX组件对外端口RESET为复位

输入CLOCK为时钟输入DEBUG_SEL7:0 为信号选择输入

DEBUG_IN031:0 DEBUG_IN131:0 为调试逻辑信号输入

DEBUG_OUT31:0为调试逻辑信号输出DEBUG_CLK为调试

逻辑信号时钟输出当前代码实现两组调试逻辑信号输入实际应

用时可以根据调试需求进行扩展该组件根据DEBUG_SEL7:0

选择相应的调试逻辑信号在DEBUG_OUT31:0输出

4.2DEBUG_MUX组件应用

ENTITY TOP IS

PORT(RESET : IN STD_ULOGIC;

CLOCK : IN STD_ULOGIC;

DEBUG_CLK : OUT STD_ULOGIC;

DEBUG_OUT:OUT STD_ULOGIC_VECTOR(31 DOWNTO 0);

DEBUG_SEL : IN STD_ULOGIC_VECTOR(7 DOWNTO 0)

);

END ENTITY;

ARCHITECTURE RTL OF TOP IS

SIGNAL DEBUG_SIGNAL0 : STD_ULOGIC_VECTOR (31

DOWNTO 0);

SIGNAL DEBUG_SIGNAL1 : STD_ULOGIC_VECTOR (31

DOWNTO 0);

BEGIN

MUX : ENTITY WORK.DEBUG_MUX

PORT MAP(

RESET => RESET,

CLOCK => CLOCK,

DEBUG_IN0 => DEBUG_SIGNAL0,

DEBUG_IN1 => DEBUG_SIGNAL1,

DEBUG_CLK => DEBUG_CLK,

DEBUG_OUT => DEBUG_OUT,

DEBUG_SEL => DEBUG_SEL

);

END ARCHITECTURE;

以上代码调用先前定义的DEBUG_MUX组件从而实现顶

层模块TOP模块的端口信号将绑定至FPGA的IO 引脚 调试

时通过设置DEBUG_SEL[7:0] 输入相应的内部逻辑信号将在

DEBUG_OUT[31:0]输出。

★ 结束语★

本调试技术将需要采集的逻辑信号以分组的方式连接至多路复用器,然后通过设置多路复用器的信号组选择信号,以选择相应的内部逻辑信号输出本调试技术兼容各种FPGA型号,并且占用的逻辑资源非常低使用的IO引脚也非常少。在实际调试应用时工程师通过使用本调试技术可以快速、便捷地采集需要的逻辑信号可以明显提高调试效率。

扫码关注

扫码关注

![电子设计:离散傅里叶变换的物理意义[学以致用系列课程之数字信号处理]](https://api.fanyedu.com/uploads/image/ba/1715f5e9182ec584b4489bd5c5f4dd.png)

![电子设计:频域采样定理及FFT算法[学以致用系列课程之数字信号处理]](https://api.fanyedu.com/uploads/image/5e/e20549b95077812a27c92ed71009cb.png)