根据IPC及中国企业需求,高速PCB工程师能力分三级,分别是初级、中级、高级工程师。那么这三种工程师技能如何升级进阶?

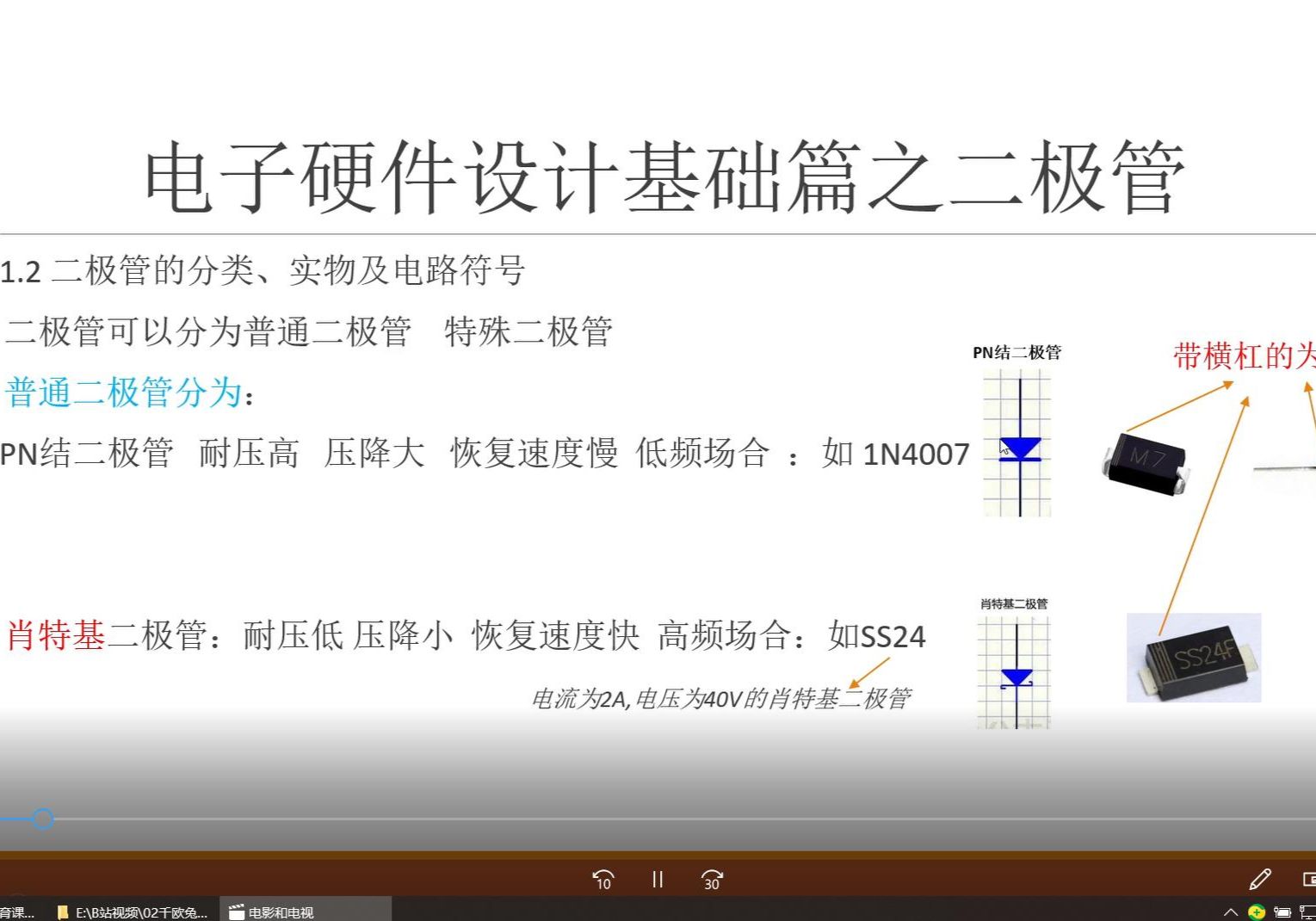

1、初级工程师(入门级)

①基础布线:

4-6层板设计,线宽/间距≥4/4mil(FR4板材),阻抗控制50Ω±10%。

掌握DDR3基础布线(T型拓扑,线长公差±50mil)。

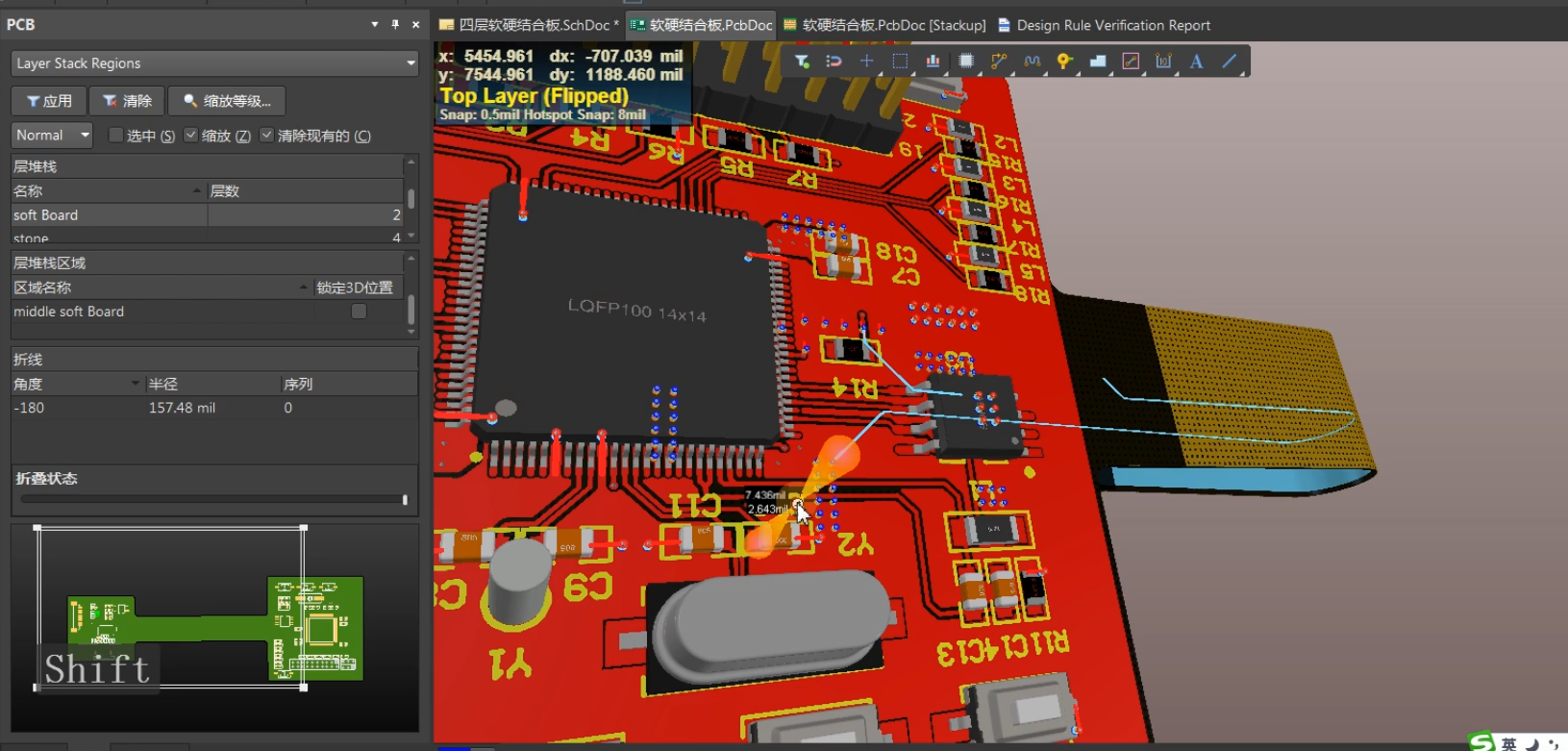

②工具链:

熟练使用Allegro/Cadence或Altium Designer完成基础布局布线。

使用Cam350检查Gerber文件,规避开短路风险。

认证推荐:IPC CID(初级认证)。

2、中级工程师(高速设计攻坚)

①高速信号设计:

DDR4/5布线(线长匹配±5mil,间距≥3倍线宽,阻抗50Ω±5%)。

PCIe 4.0/5.0差分对(85Ω±5%,过孔反焊盘优化)。

②仿真验证:

使用HyperLynx/Sigrity完成眼图仿真(眼高≥240mV,眼宽≥0.7UI)。

电源完整性分析(PDN目标阻抗≤0.1Ω@100MHz)。

认证推荐:IPC CID+(高速设计专项)。

3、高级工程师(系统级专家)

①复杂系统设计:

16层以上服务器主板,支持0.4mm pitch BGA扇出(盲埋孔+树脂塞孔)。

多板系统协同(如FPGA+GPU异构计算板)。

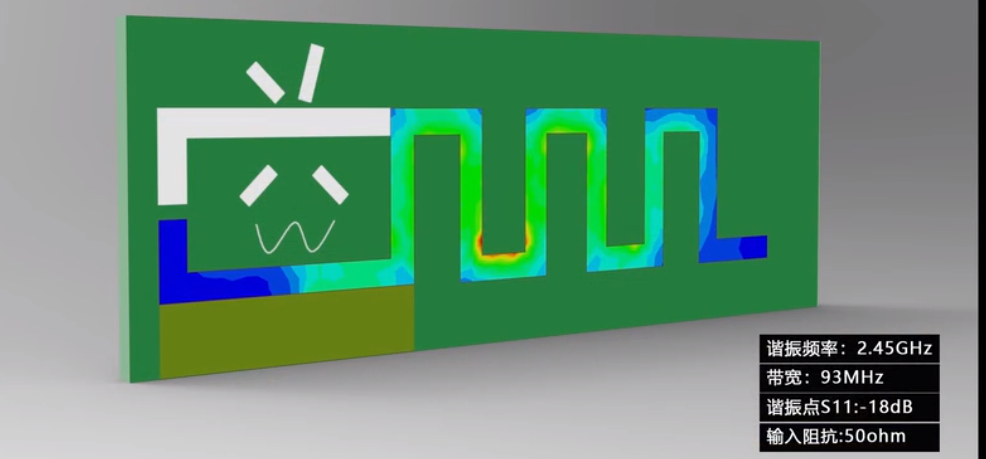

②高频与射频设计:

25G/100G光模块(Megtron 6板材,损耗角正切≤0.002@10GHz)。

毫米波天线馈线(共面波导CPW,阻抗50Ω±3%)。

认证推荐:IPC CES(认证设计专家)。

4、未来趋势及准备

①技术趋势

3D-IC设计:通过Allegro 3D Canvas实现芯片-封装-板级协同。

AI辅助设计:Cadence Cerebrus优化布线策略(效率提升30%)。

②核心竞争力公式

2025竞争力=40%高速设计+30%仿真能力+20%国产替代+10%自动化

结论:

高速PCB工程师的终极目标是从“画线工”升级为“系统问题解决者”。每年至少主导1个跨领域项目(如5G基站→车规ECU),并掌握国产替代与AI工具,才能避免被低端内卷淘汰。

本文凡亿企业培训原创文章,转载请注明来源!

扫码关注

扫码关注