简介

随着芯片设计日趋复杂,片上网络(NoC)已成为实现异构计算组件之间高效数据通信的重要组成部分。然而,向 3D 芯片设计的过渡和基于芯片的架构的兴起为 NoC 技术带来了新的挑战和机遇。本文将引导您了解三维空间中 NoC 的演变情况,介绍关键注意事项和新兴方法。

NoC 日益重要

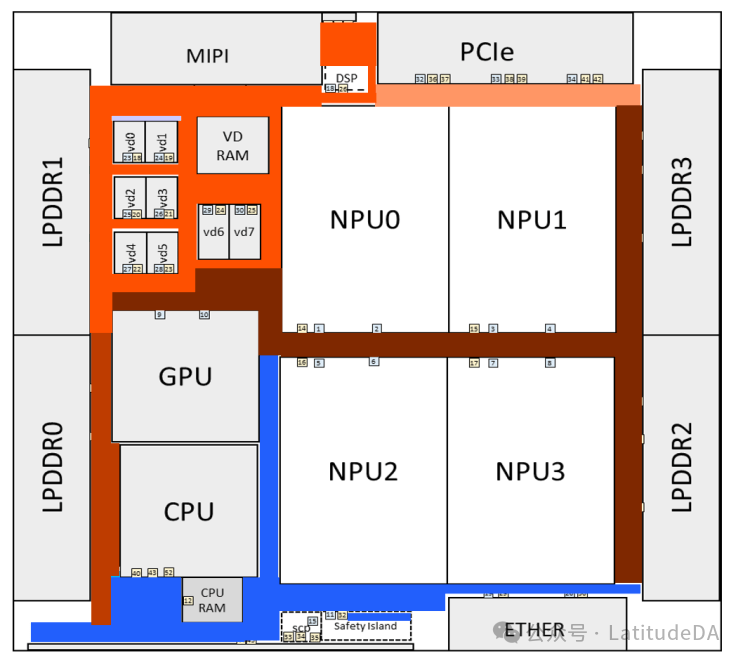

NoC 是现代复杂芯片设计的主干,可促进各种处理单元、存储器和外设之间的数据传输。与传统的基于总线的互连相比,NoC 具有多种优势,包括更高的可扩展性、更低的通信延迟以及对异构集成的更好支持。

随着芯片复杂性的不断提高,设计中集成了越来越多的处理内核、内存和专用加速器,NoC 的作用变得越来越重要。NoC 为设计人员提供了在芯片上路由数据的结构化高效方法,从而使他们能够管理复杂性。

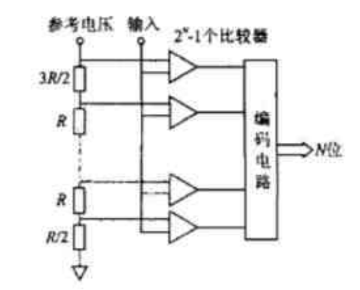

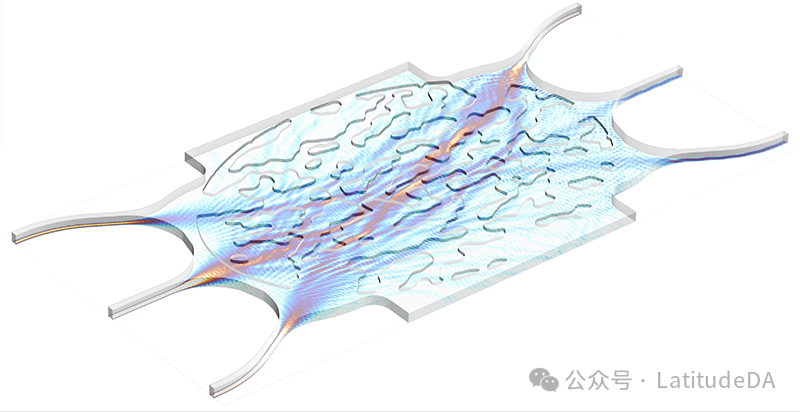

图 1:分而治之,显示使用相干和非相干 NoC IP 连接的不同区块。来源:Arteris

图 1:分而治之,显示使用相干和非相干 NoC IP 连接的不同区块。来源:Arteris

向 3D 芯片设计过渡

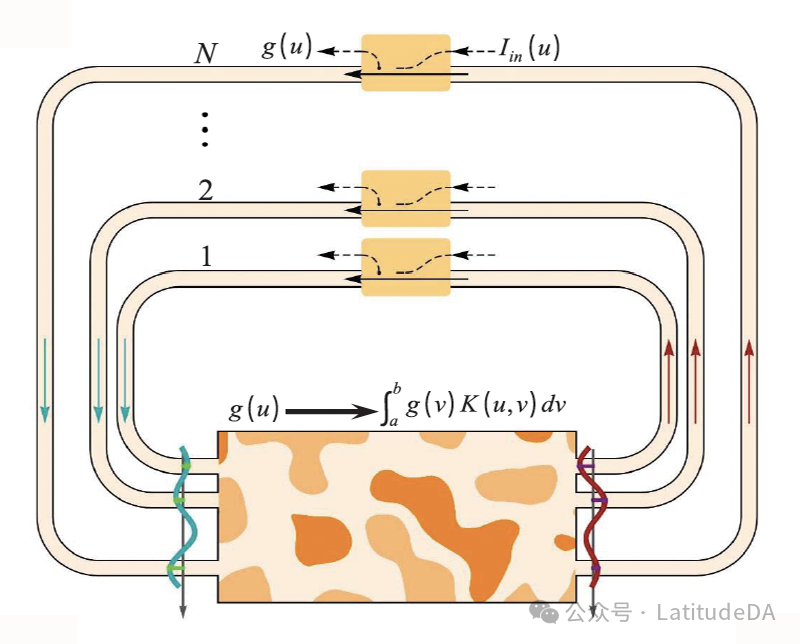

三维芯片设计是多个芯片垂直堆叠在一起的设计,为 NoC 架构带来了新的挑战和机遇。在三维设计中,芯片的垂直集成可显著缩短通信距离和延迟,但同时也需要重新考虑 NoC 拓扑和协议,以充分利用三维结构的优势。

三维芯片设计中 NoC 的主要考虑因素包括:

1.分层设计:三维设计通常需要采用分层 NoC 方法,为芯片内和芯片间通信分别设计不同的 NoC。这样可以更好地管理复杂性和安全性。

2.垂直通信: NoC 必须无缝处理垂直芯片间的通信,确保低延迟和高带宽数据传输。

3.功耗和散热挑战: 3D 设计密度的增加会导致功耗和散热挑战的增加,NoC 设计必须解决这些问题。

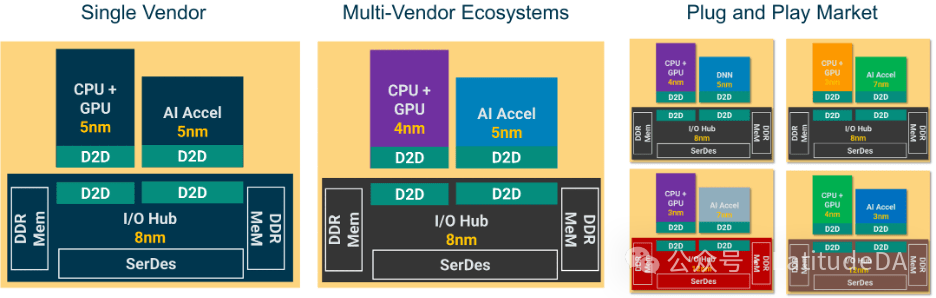

4.标准化和互操作性: 为芯片间通信协议(如 UCIe)制定标准对于实现即插即用的芯片生态系统很重要。

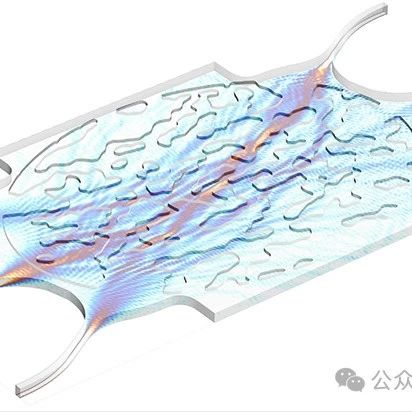

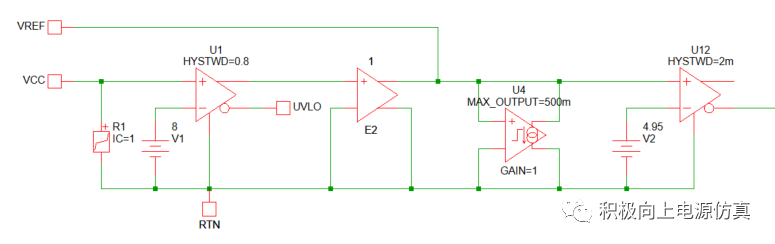

图 2:芯片组Chiplet使用场景。来源:Blue Cheetah新兴方法和趋势

图 2:芯片组Chiplet使用场景。来源:Blue Cheetah新兴方法和趋势

随着行业向 3D 芯片设计过渡,以及基于芯片组架构的重要性不断增加,出现了几种方法和趋势:

1.灵活的可编程 NoC: NoC 正变得越来越灵活和可编程,允许设计人员定制拓扑结构、路由算法和服务质量 (QoS) 策略,以满足其设计的特定要求。

2.光互连: 目前正在探索在 NoC 中使用光互连,以解决与电气互连相关的日益增长的带宽需求和功耗挑战。

3.异构 NoC 拓扑: 设计人员正在尝试采用混合 NoC 拓扑,将不同的通信模式(如分组交换和电路交换网络)结合起来,以优化特定用例。

4.安全性和可靠性: 随着 NoC 成为系统的关键部分,越来越重视集成安全功能和提高 NoC 架构的整体可靠性。

5.芯片生态系统和标准化: 基于芯片的设计的兴起推动了对标准化接口、协议和验证框架的需求,从而促进了芯片生态系统的蓬勃发展。

结论

三维芯片设计中 NoC 的发展是复杂且快速变化的领域。通过了解关键考虑因素、新兴趋势和最佳实践,可以驾驭这种不断变化的格局,开发出高效、可扩展和可靠的 NoC 架构,以支持现代芯片设计日益增长的复杂性。随着不断突破集成和性能的极限,NoC 在支持下一代计算系统方面的作用只会变得更加关键。

扫码关注

扫码关注