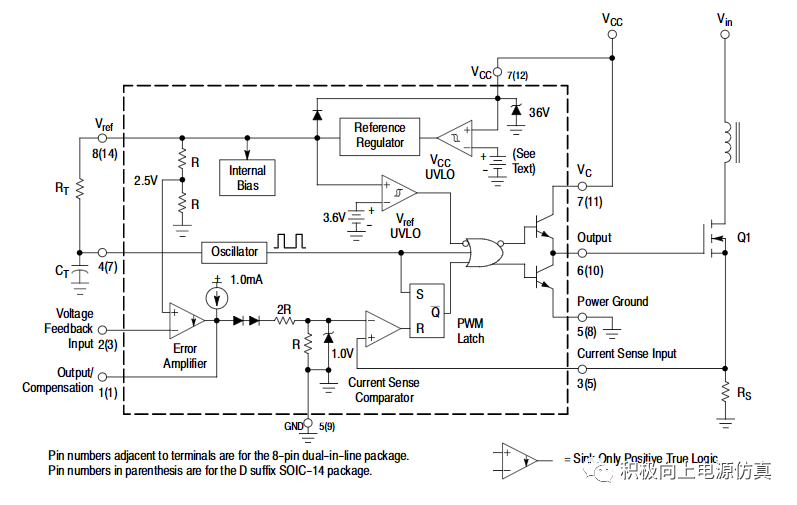

UCx843系列是非常经典的峰值电流模式PWM控制器,今天通过行为建模捋一捋其工作原理与频率、最大占空比计算。

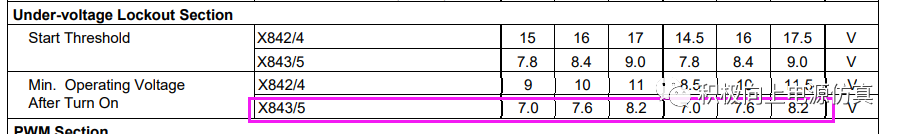

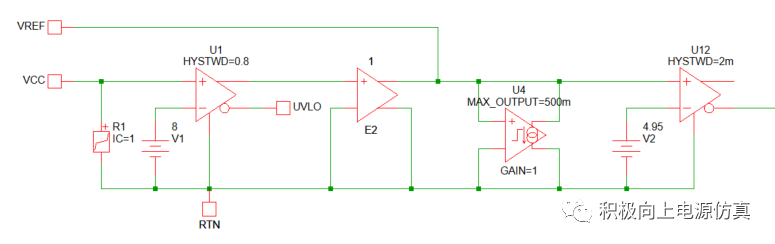

1、电源滞回与基准

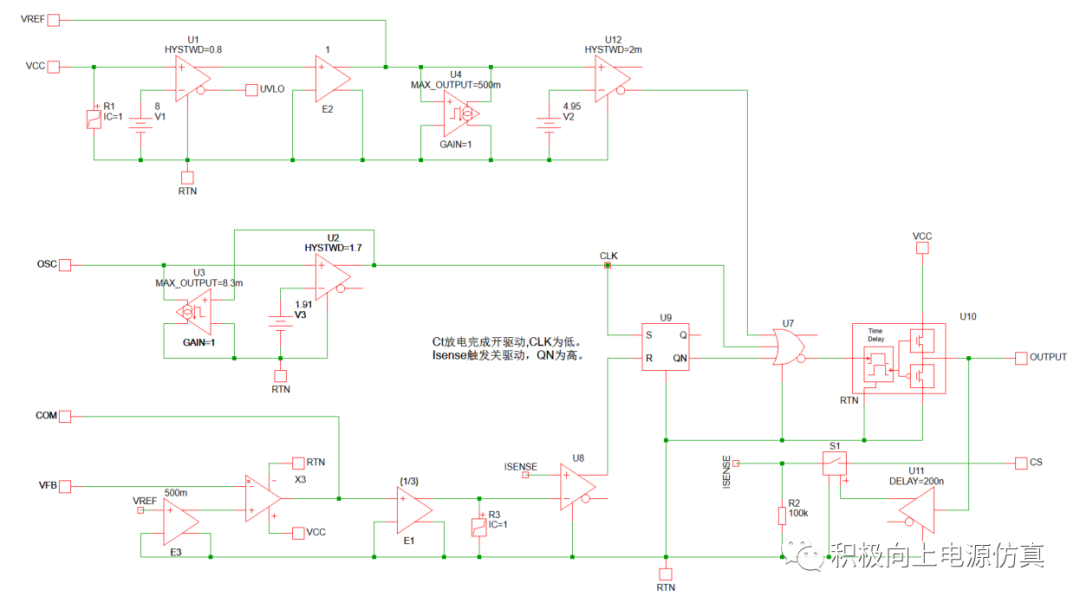

以UCX843为例,8.4V启动,7.6V欠压,回差0.8V,使用simplis滞回比较器可以直接实现该效果,HYSTWD=8.4-7.6=0.8,参考电压(8.4-7.6)/2=8。

因为比较器输出有阻抗,使用跟随器隔离阻抗输出5V,功耗与VCC过压不影响逻辑可忽略,高压启动和软启用仿真太慢了。

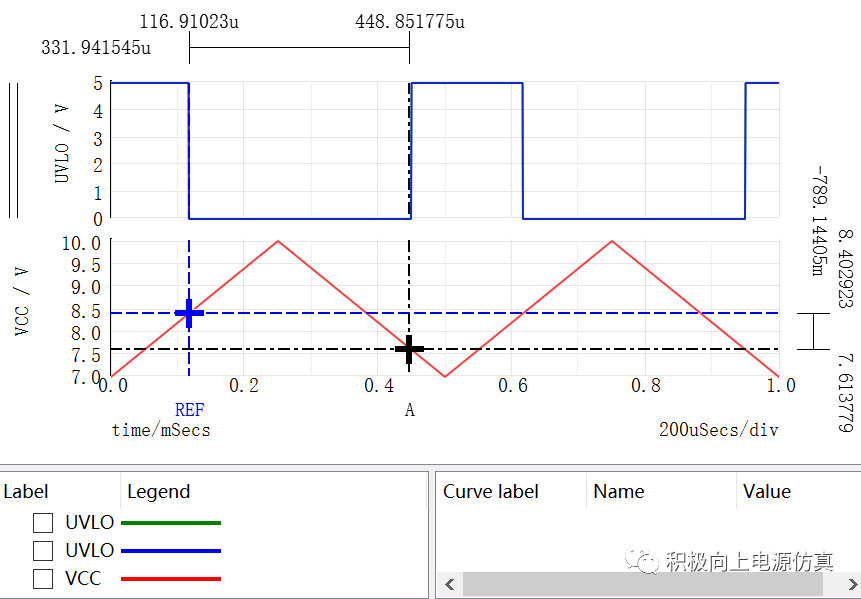

VCC欠压滞回波形:

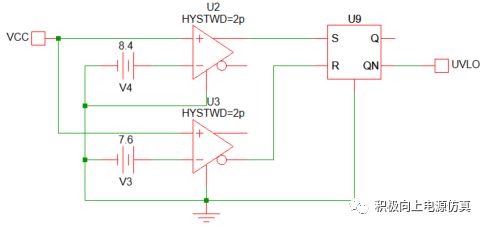

滞回也可以使用RS触发器实现:

2、振荡器

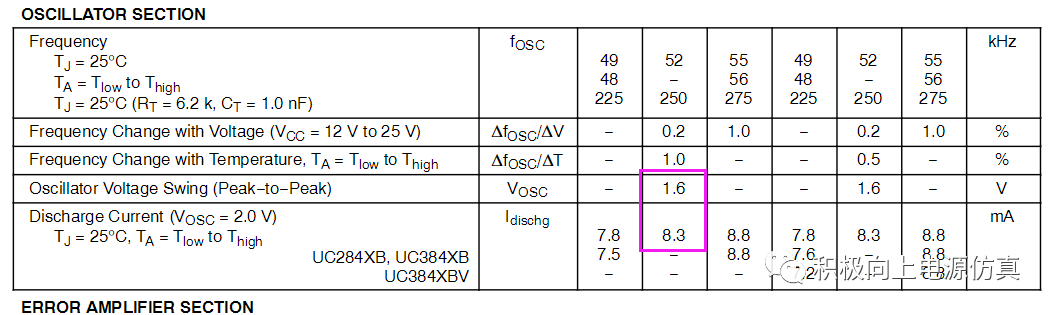

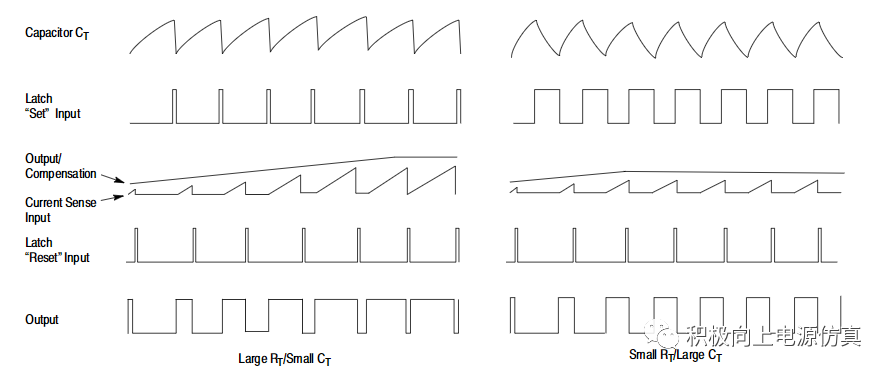

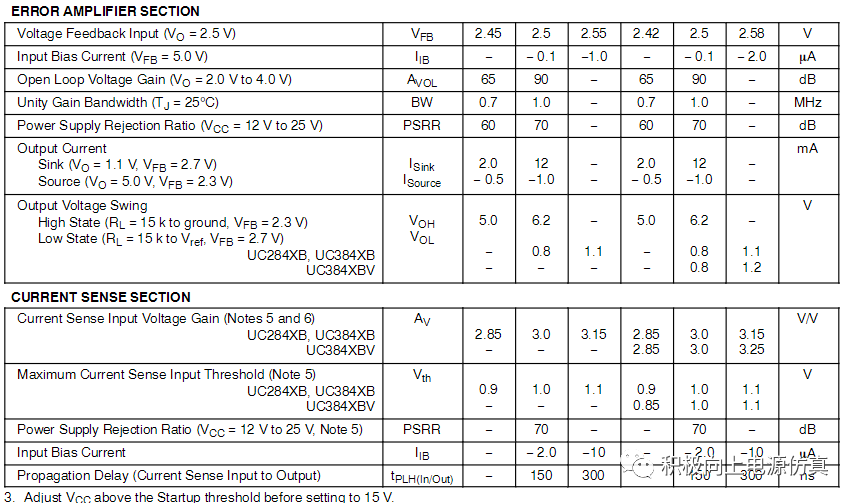

从表格可知内部有放电电流源8.3mA,振荡三角波峰峰值1.6V(这里按1.06-2.76)。

内部基准VREF通过Rt给Ct充电,电压达到2.76V时内部电流源(8.3mA)给Ct放电(外部VREF一直在充电);当CT电压低于1.06V时停止恒流放电。该过程会形成下图的第一排三角波,上升下降沿与电阻电容大小有关。

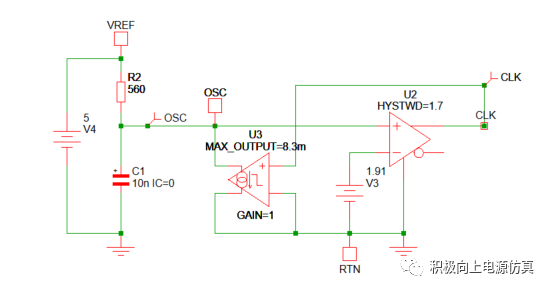

根据该逻辑搭建模型,这里的内部电流源用的饱和受控源,可以省一个开关和二极管:

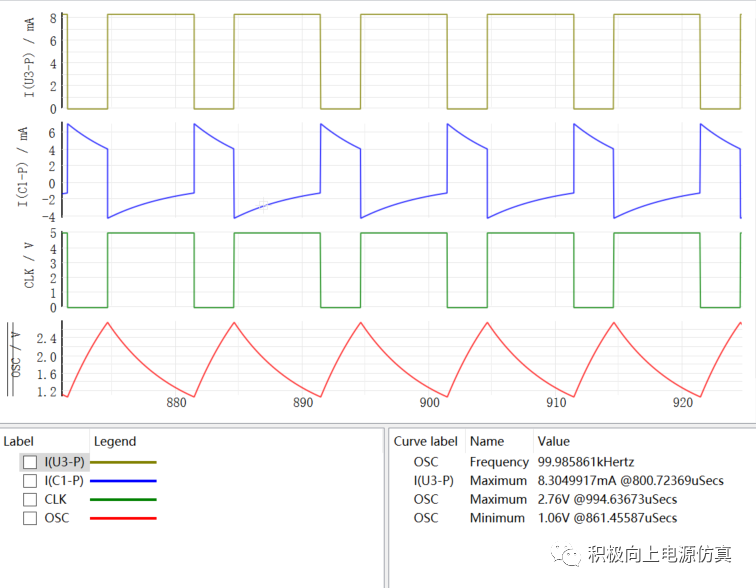

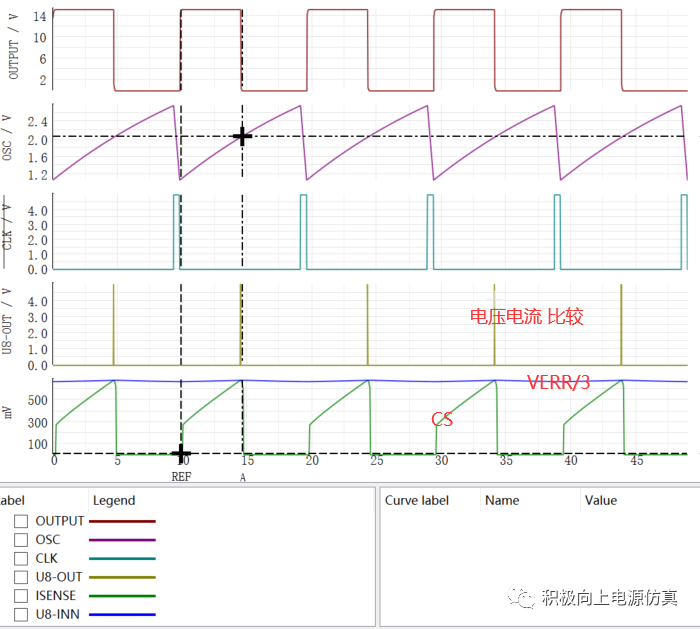

仿真波形(从上到下分别是内部电流源电流、电容CT电流、CLK、OSC):

OSC低于1.06时CLK置高,内部电流源停止放电,OSC高于2.76时CLK置高,同时内部电流源以8.3mA放电,期间VREF一直给电容充电。

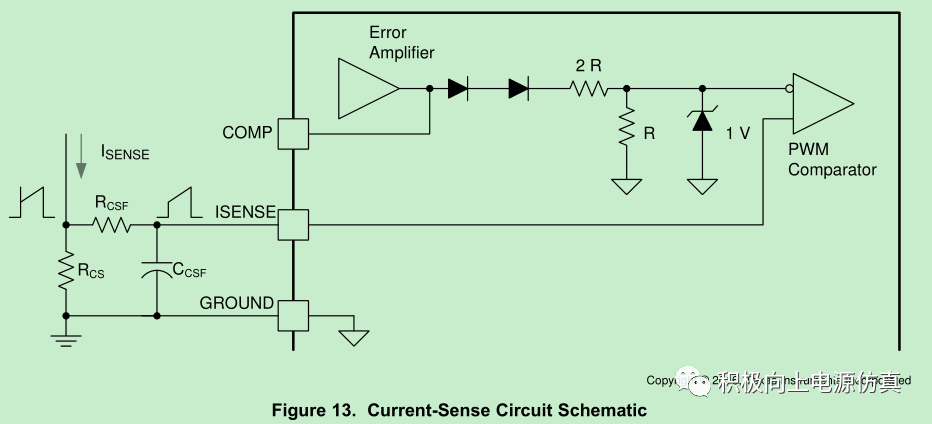

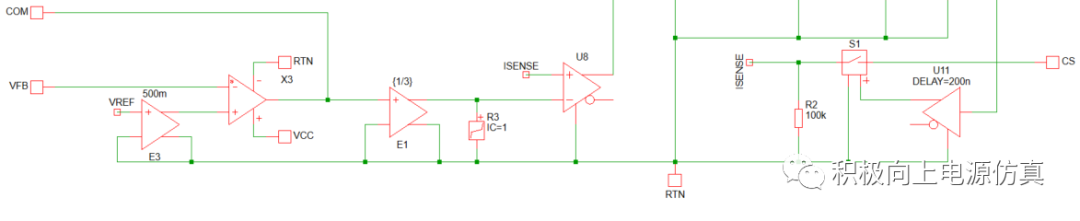

3、误差放大器与电流采样

运放同相端2.5V,反相端接VFB,输出衰减3倍,最高限制为1V。

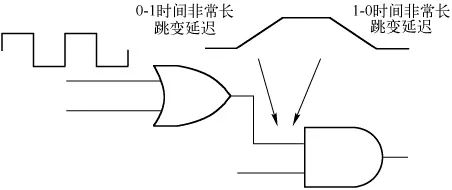

电流采样有前沿消隐150ns,用驱动 buffer延时触发开关即可。

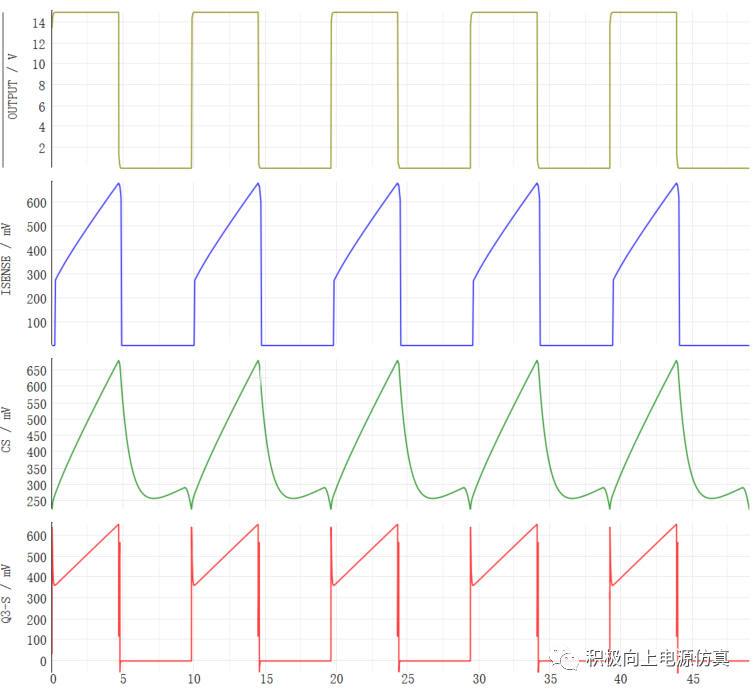

下图为CS电流采样波形,从下到上分别是电流采样信号、RC滤波和斜坡补偿后的电流采样信号、消隐后的电流采样信号、驱动。可见消隐后只剩尖峰,开驱动时的尖刺已被消隐。

具体运放参数可参考下表填入:

4、驱动逻辑

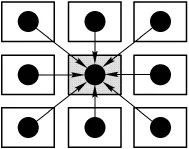

电流采样值>电压环输出时关驱动,CLK低时开驱动。

驱动使能还有两个条件:1)VCC不欠压,2)CLK不能为高(可以利用这个使用Rt限制最大占空比),在驱动上增加或非门实现。

根据以上驱动逻辑搭建仿真模型:

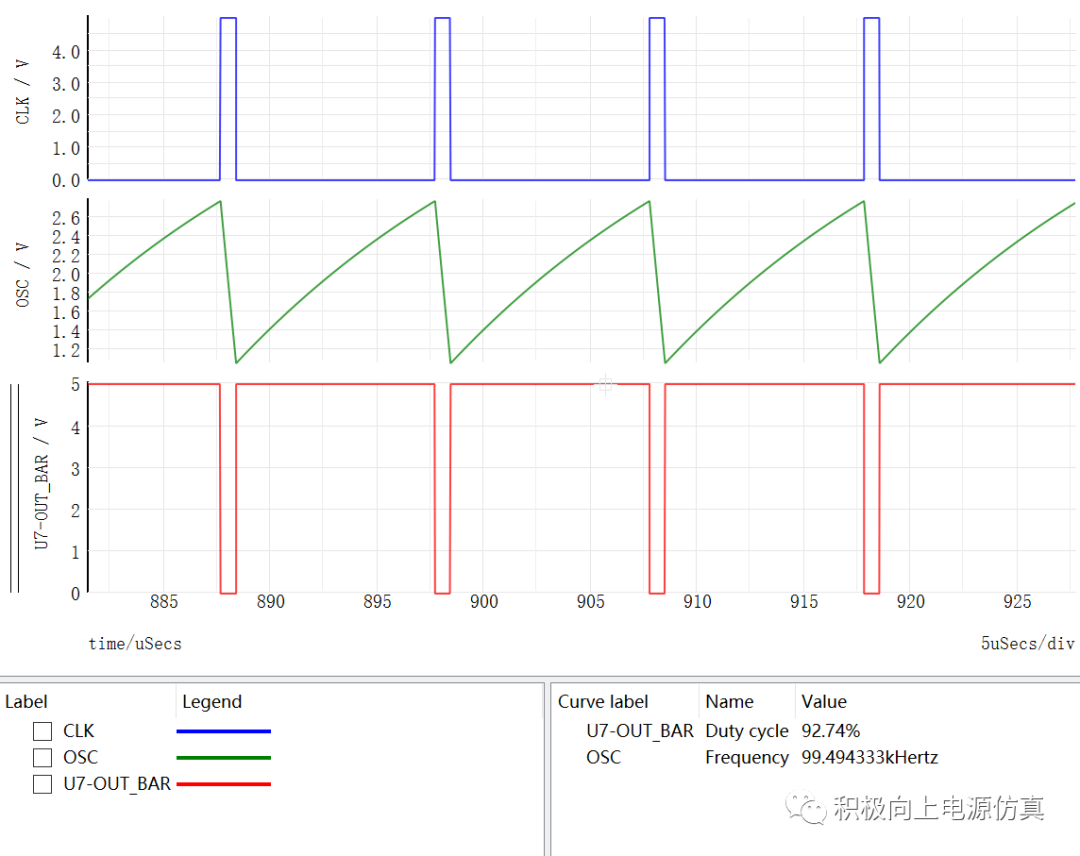

仿真波形:

从以上波形可知模型符合逻辑预期。

5、频率与最大占空比计算

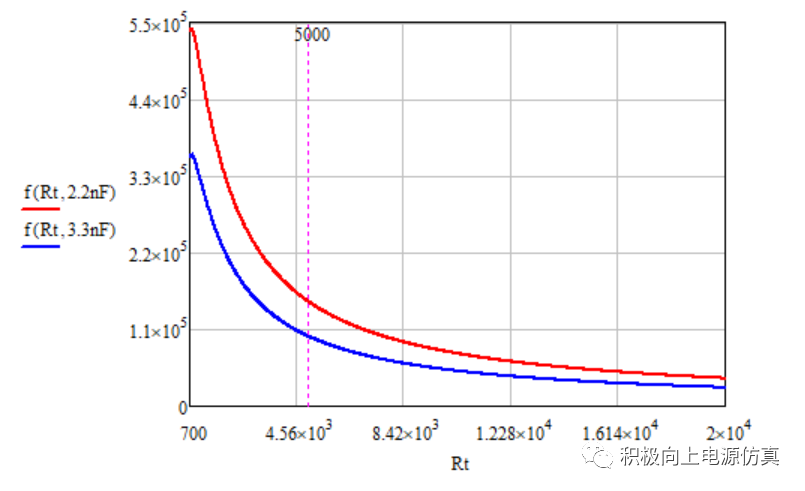

资料上频率计算一般以1.72/RC或1.8/RC,但限制条件是R>5KΩ,但如果R<5k该如何计算呢?<>

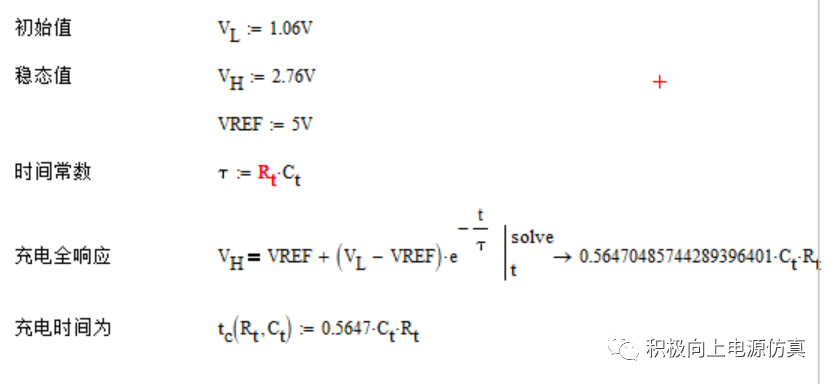

根据以上建模可知充放电为一阶电路的全响应模型:

Ct电压上升阶段:只有VREF通过Rt给其充电。

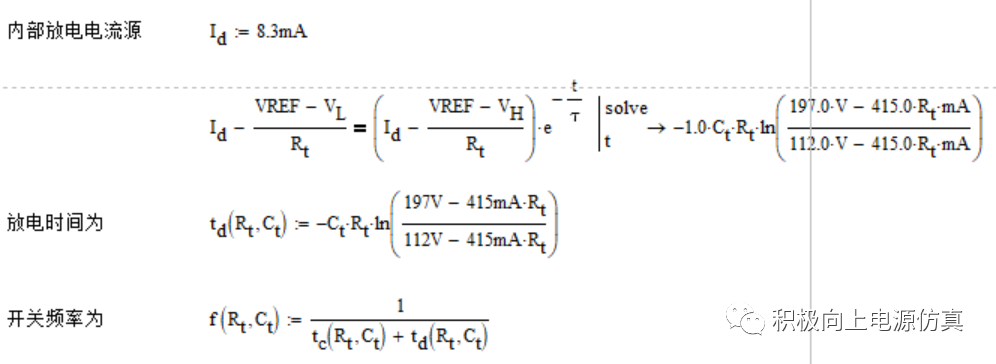

Ct电压下降阶段:电压达到2.76V时内部电流(8.3mA)给Ct放电(外部RT一直在充电);当CT电压低于1.06V时停止恒流放电。

当Rt>5k时,其频率曲线才接近线性。

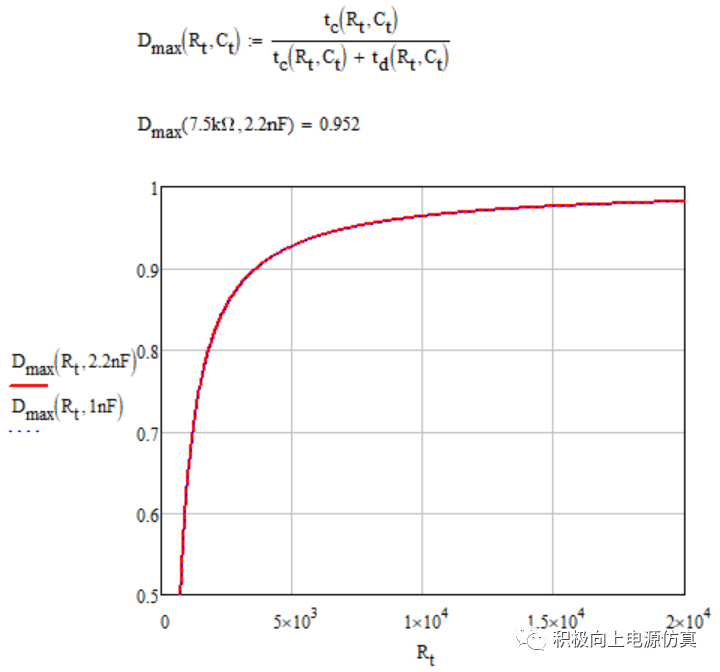

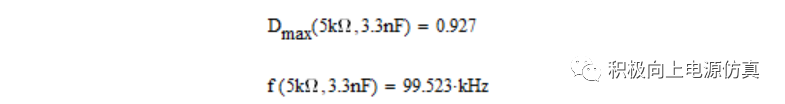

由于逻辑限定放电时驱动不能打开,所以调Rt值可以限制驱动最大占空比,即最大上升时间为Ton_max:

由上图知UC2843最大占空比只与电阻有关。

如果不想加斜率补偿可直接把最大占空比限在50%以下。

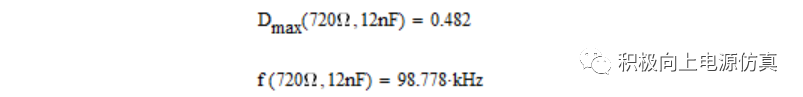

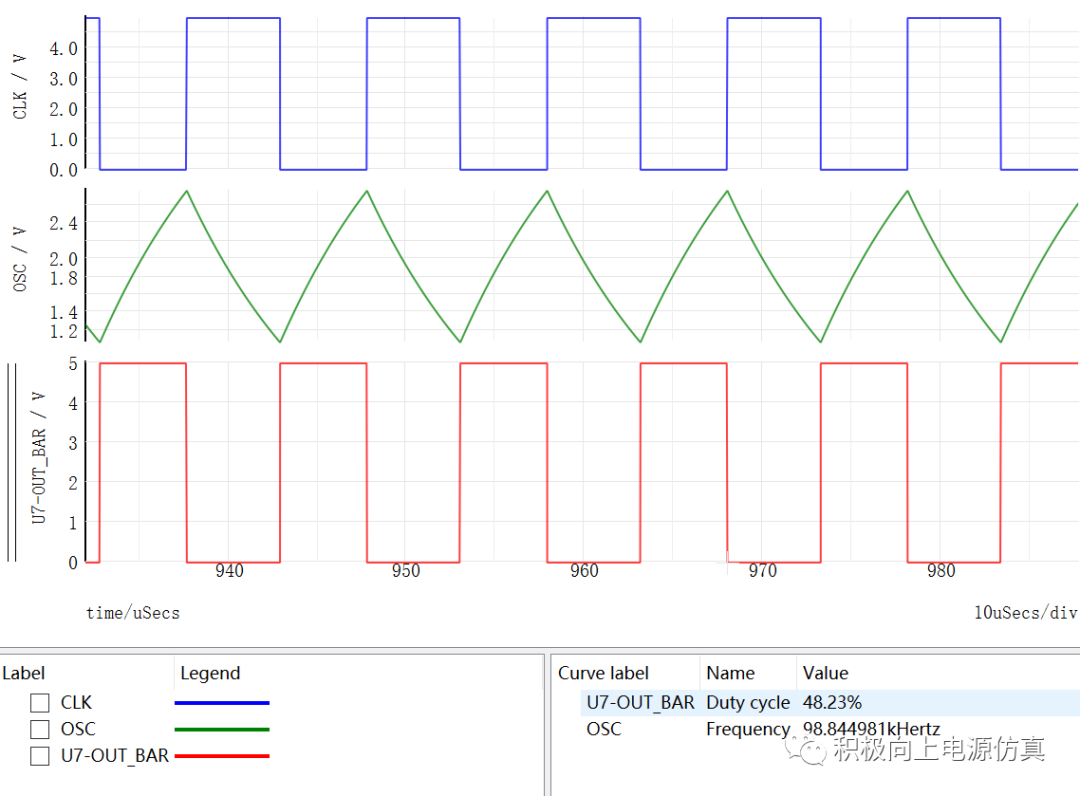

下面用仿真结果验证计算是否正确:

可见仿真与计算一致。

6、全片验证

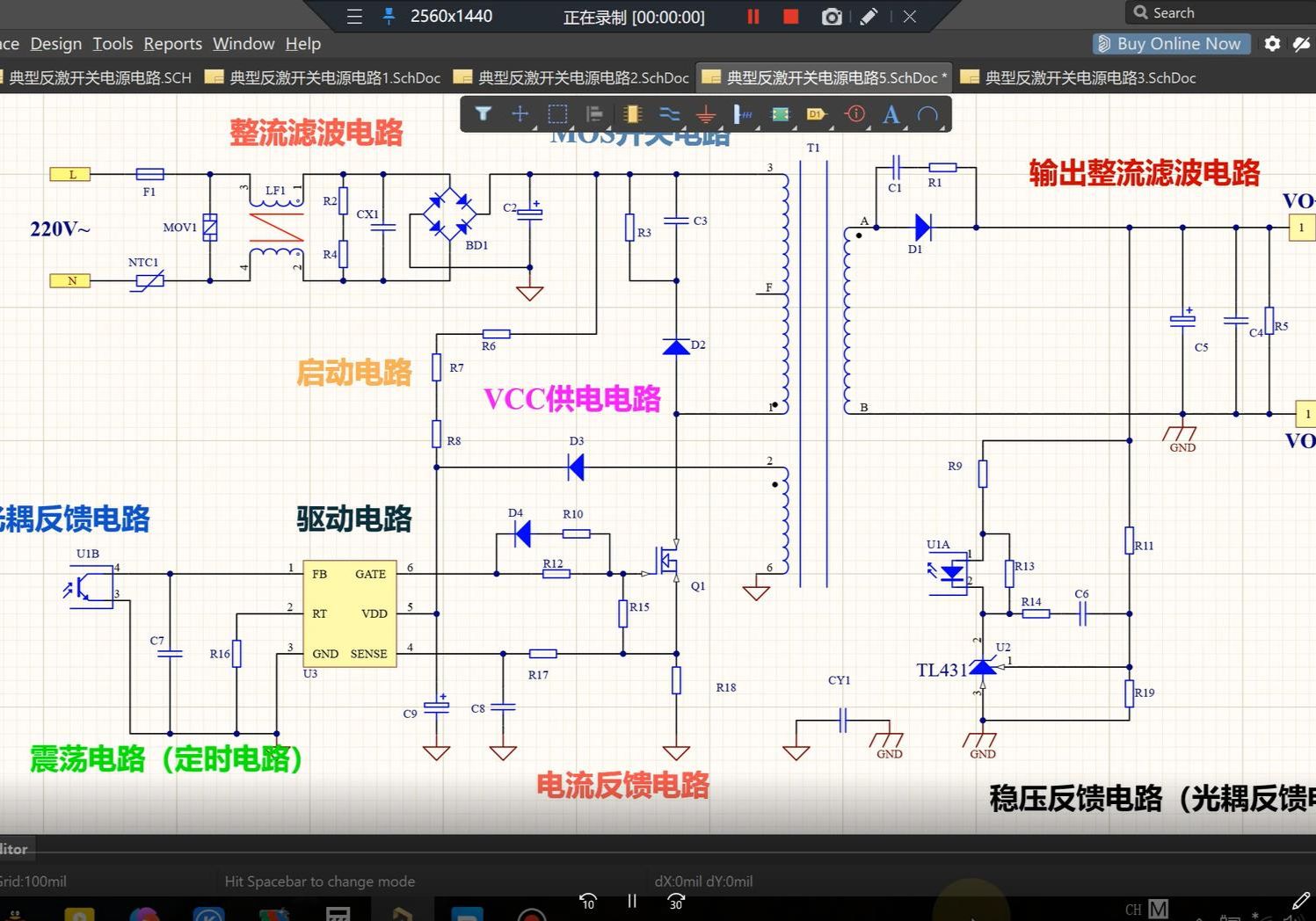

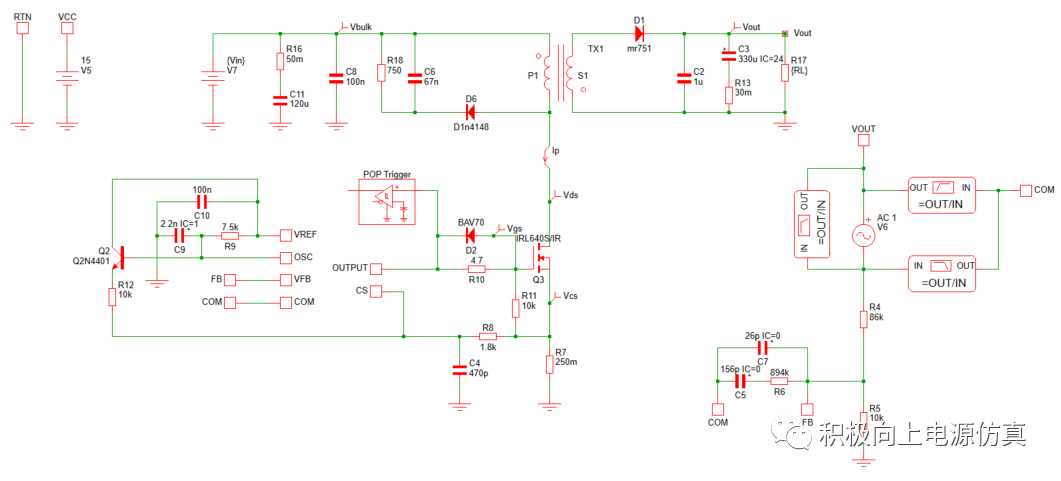

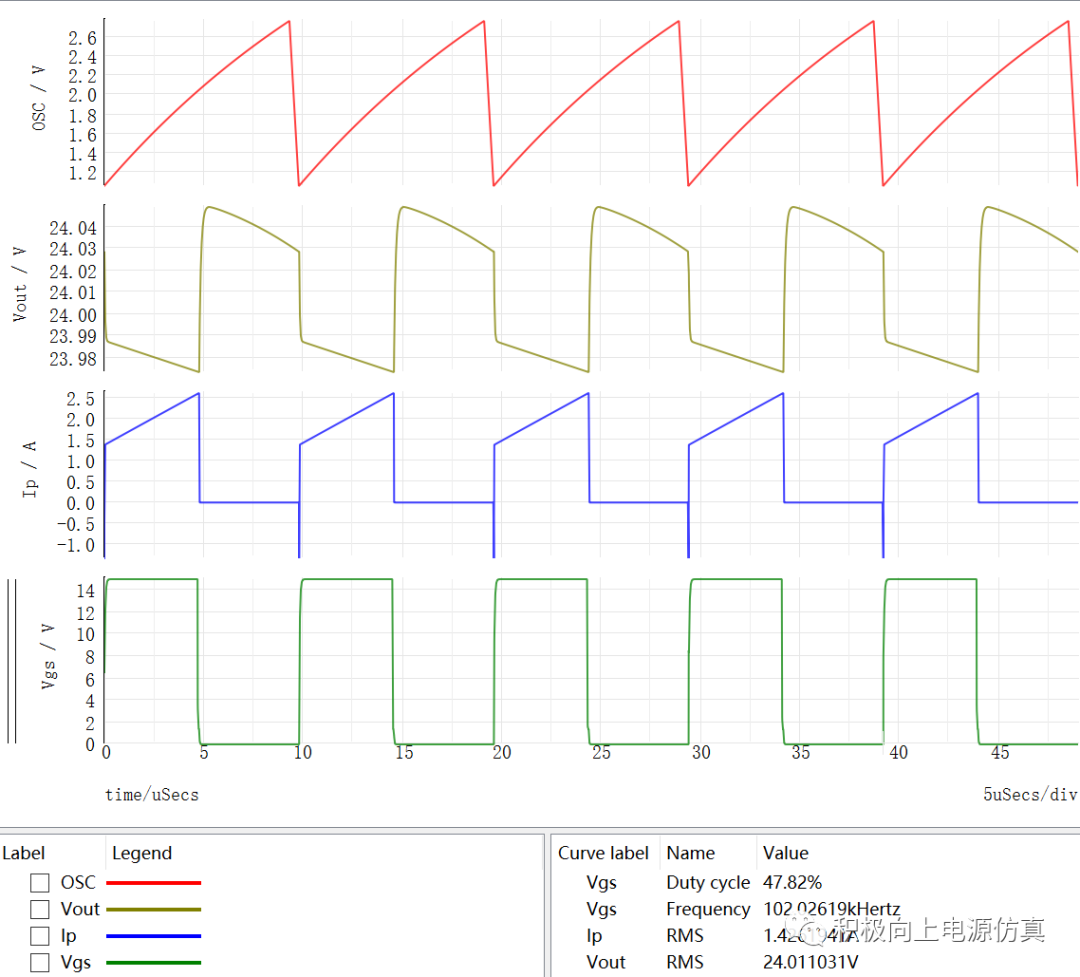

将建模的芯片代入反激电路中仿真验证是否可正常工作:

仿真波形正常,行为建模与计算完成,这样芯片工作原理就理得很清楚了。

扫码关注

扫码关注