在DC-DC转换电路设计中,滤波元件和去耦电容的精确防止,对抑制高频噪声、改善电磁干扰(EMI)性能至关重要,而且合理的布局不仅能够提升电路的稳定性和效率,也能确保信号的纯净度,那么如何放置?

滤波电容的放置策略

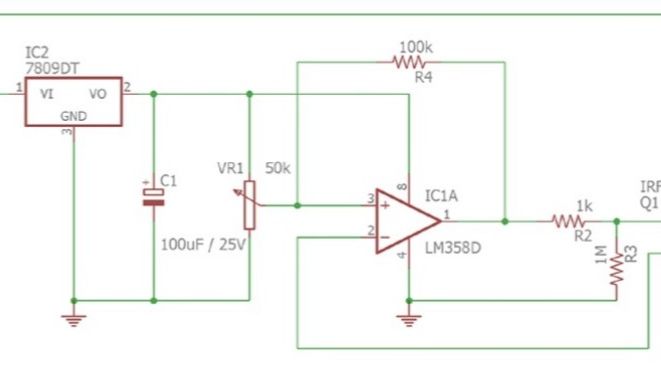

1、输入滤波电容(Cin)和输出滤波电容(Cout)

位置:Cin和Cout应尽可能靠近DC-DC转换器的输入和输出引脚,以缩短电流路径,减少纹波电压。

布局:Cin和Cout的接地引脚需分别独立接地,避免相互干扰,且接地线应尽量短而粗。

分离:Cin和Cout的接地端应彼此分开1cm~2cm,以减少相互间的耦合效应。

2、功率电感

距离:功率电感应放置在距离IC适中的位置,以最小化开关节点的辐射噪声。

铺铜:电感下方避免走线和铺铜,以防涡流产生,影响电感性能。

3、续流二极管

接线:续流二极管应采用短而宽的接线方式,直接接在IC的GND端和SW端,以减少噪声和寄生电感。

去耦电容的布置策略

1、容值选择

高频噪声:小容值电容(如10pF、100pF)更适合滤除高频噪声,应放置在靠近噪声源的位置。

低频噪声:大容值电容(如1uF、10uF)用于滤除低频噪声,可放置在稍远的位置。

2、并联使用

组合:采用多个不同容值的电容并联,可以有效覆盖更宽的频率范围,提高滤波效果。

布局:小容值电容应最靠近芯片电源引脚,按容值递增的原则依次远离芯片。

3、ESL和ESR

低ESL:选择ESL(等效串联电感)低的电容,以提高电容的自谐振频率,有利于高频噪声的抑制。

低ESR:ESR(等效串联电阻)低的电容在高频下阻抗更低,能更有效地滤除高频噪声。

4、布线

短路径:去耦电容与芯片电源引脚之间的布线应尽量短,以减少寄生电感。

避免平行:多个去耦电容并联时,避免平行排列以减少互感效应。

5、温度特性

选择:在高温或温度变化较大的环境中,应选用温度特性优异的电容,确保滤波效果稳定。

本文凡亿企业培训原创文章,转载请注明来源!

扫码关注

扫码关注