简介

在快速发展的半导体技术领域,Bunch of Wires(BoW)协议因其能够促进高效的芯片到芯片(D2D)并行接口而脱颖而出。本文探讨 BoW 的最新进展和未来方向,重点是其在光学、内存和物联网接口中的应用。

BoW 主要功能

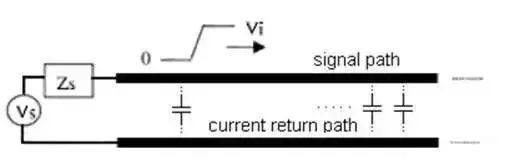

BoW 的开放式物理层和链路层规范旨在支持高性能 D2D 接口。关键性能指标包括每条线路高达 32Gb/s 的数据传输速率、低于 0.5pJ/bit 的能效和低于 8ns 的延迟。BoW 与各种封装和集成电路工艺的兼容性使其成为不同成本和性能设计点的通用解决方案。

发展到 BoW 2.1

为了促进开放式芯片经济的发展,BoW 正在不断改进,以满足新应用的需求,特别是在人工智能、边缘和物联网领域。即将发布的 BoW 2.1 版本将在三个关键领域引入规范扩展: 光学、内存和物联网。

为人工智能和边缘应用提供更高性能

BoW 2.1 的目标是提供人工智能和边缘应用所需的更高性能。这包括提高数据传输速率和降低功耗,使其成为适用于高需求环境的强大解决方案。

降低物联网应用成本

物联网应用的重点是在保持性能的同时降低成本。这就需要优化规格,确保低功耗和最小面积使用,这对于物联网设备非常重要。

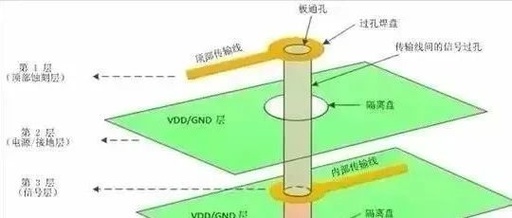

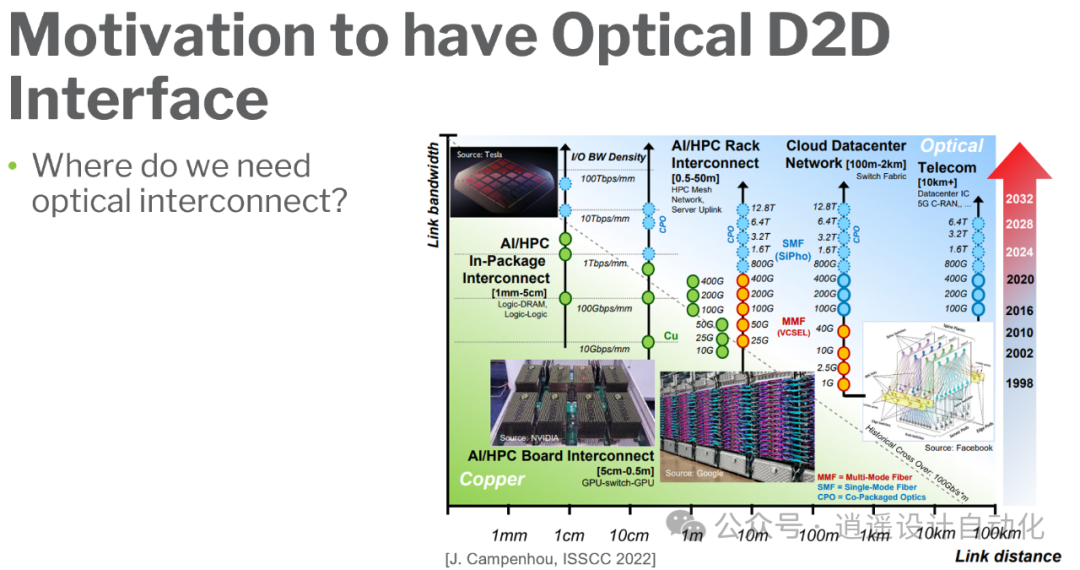

D2D 接口的光互连

光 D2D 接口的动机

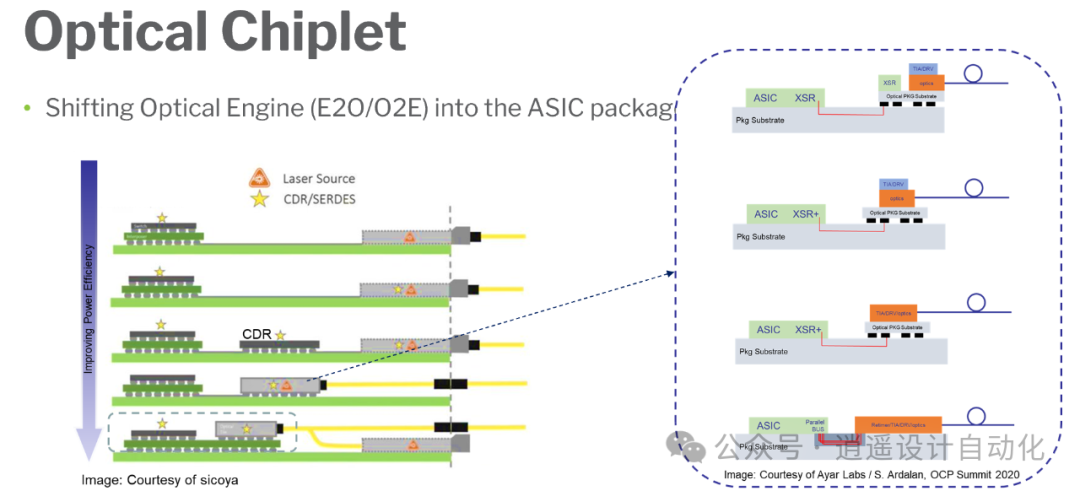

在 ASIC 封装中集成光学引擎(电-光和光-电)具有多种优势,如减少延迟和增强数据完整性。

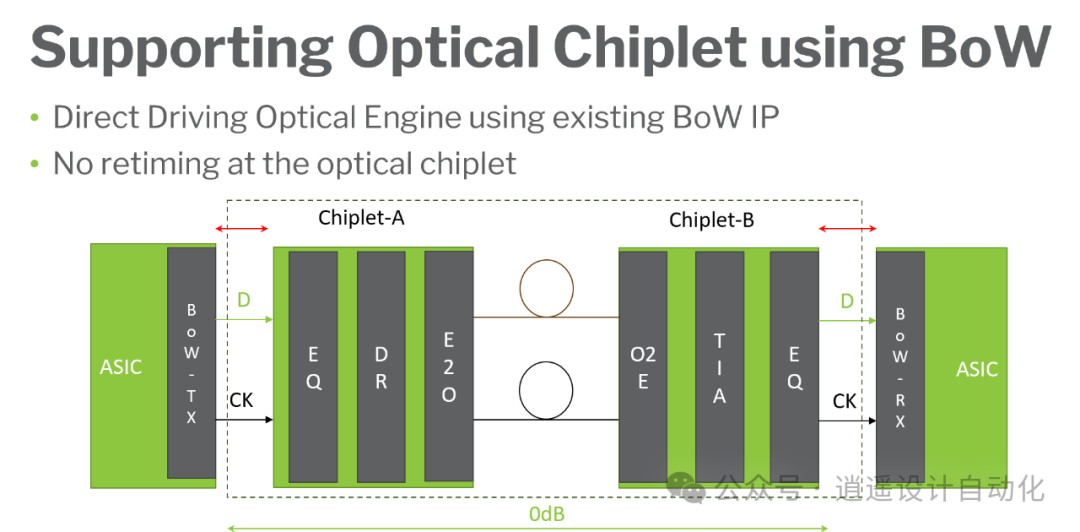

使用 BoW 直接驱动光引擎

这种方法是利用现有的 BoW IP 直接驱动光引擎,而无需在光芯片上重新定时。这既简化了设计,又提高了性能。

内存接口和 "内存墙

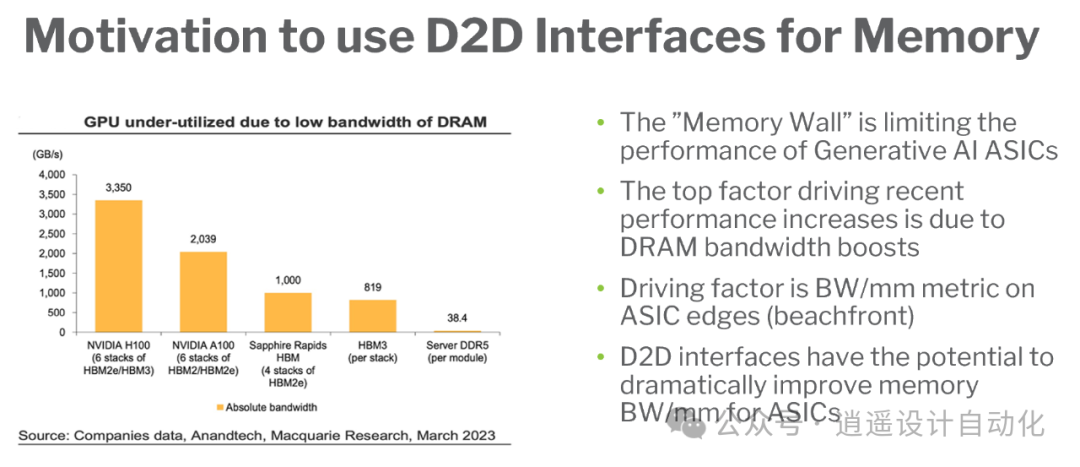

内存墙的挑战

内存墙 "是生成式人工智能 ASIC 性能的一个重要瓶颈,其主要驱动因素是 DRAM 带宽限制。BoW 接口可显著提高 ASIC 的每毫米内存带宽,从而有效解决这一难题。

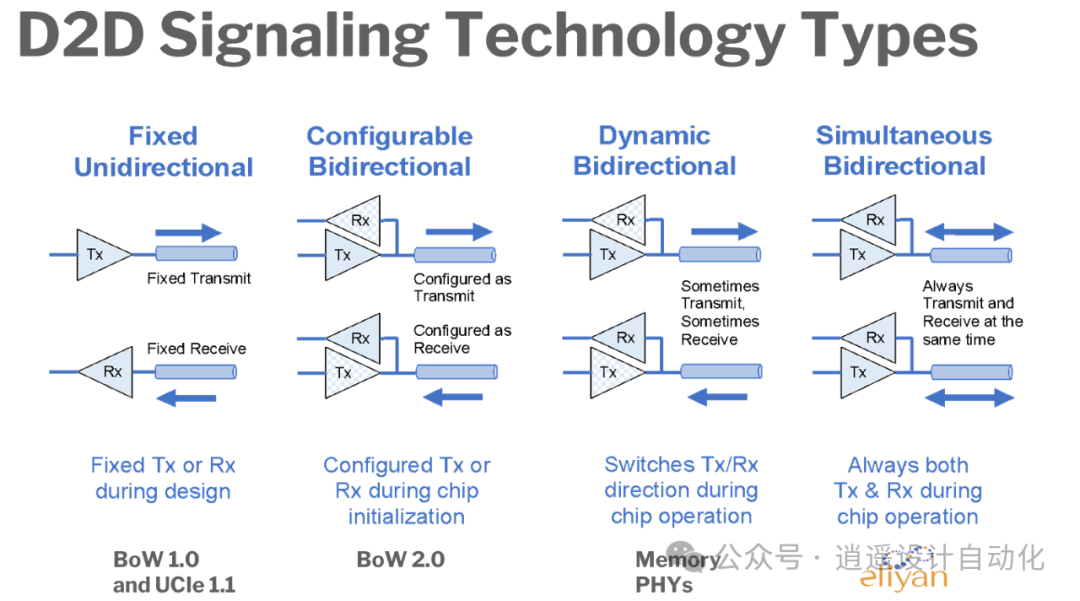

D2D 信令技术类型

BoW 1.0、UCIe 1.1 和即将推出的 BoW 2.0 为 D2D 信令提供了各种解决方案。每次迭代都会带来带宽、能效和延迟方面的改进。

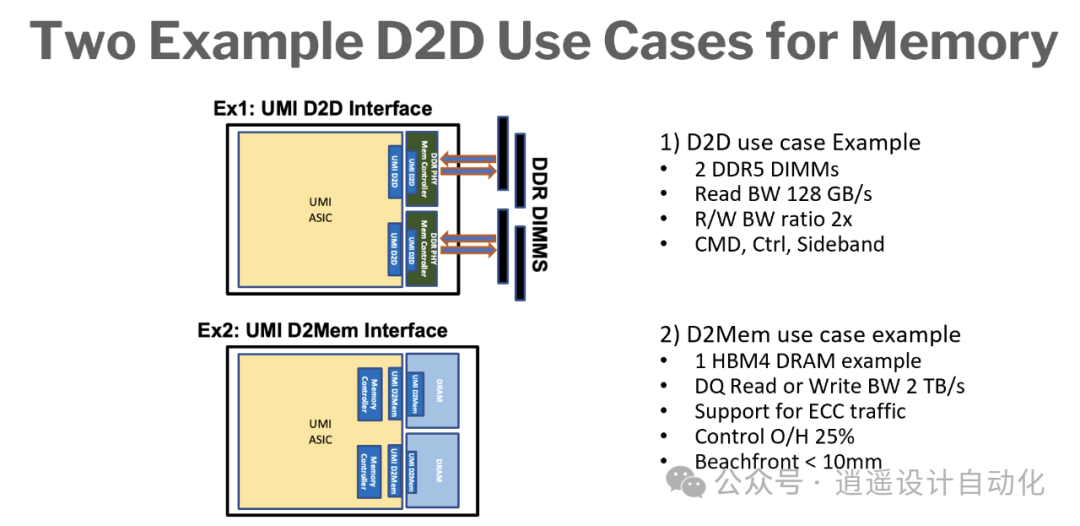

D2D 存储使用案例示例

1. DDR5 DIMM: 提供 128 GB/s 的读取带宽,读/写带宽比为 2 倍。

2. HBM4 DRAM:支持 2 TB/s 的读/写带宽,ECC 流量和控制开销为 25%,海滨面积小于 10 毫米。

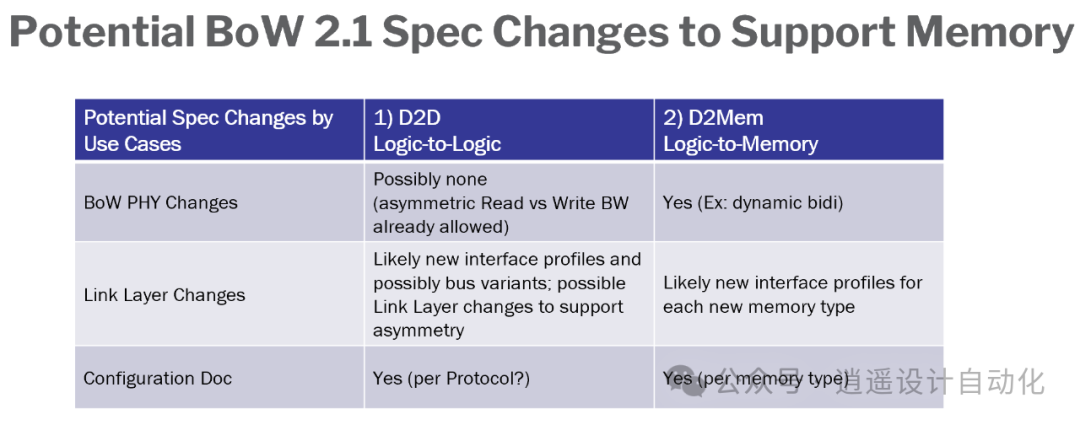

BoW 2.1 规范的潜在变化

逻辑到逻辑接口

物理层变化: 可能保留非对称读写带宽。

链路层变化: 支持非对称的新接口配置文件和可能的总线变体。

配置文档: 针对每个协议。

逻辑到内存接口

物理层变化: 动态双向通信。

链路层变更: 每种存储器类型的新配置文件。

配置文档: 针对每种内存类型。

物联网和传感器 定制解决方案

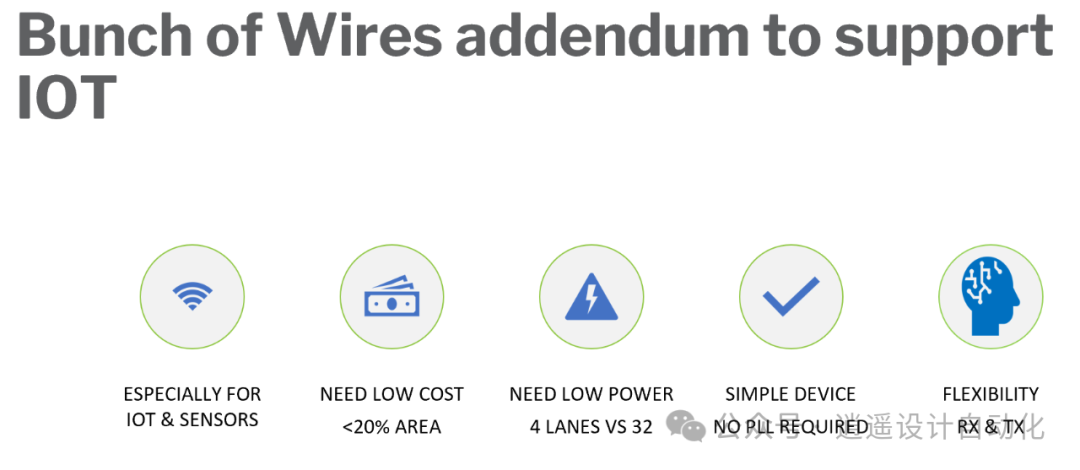

物联网接口要求

物联网应用要求低成本、低功耗的解决方案,并简化设备要求。BoW 可通过以下方式满足这些需求:

减少面积和功耗。

支持灵活的 RX 和 TX 配置,无需 PLL。

确保从低到高时钟速率(500 MHz 至 1 GHz 及更高)的可扩展性。

物联网提案的优点和缺点

优点

由于数据总线与时钟非常接近,因此优化了同步和信号完整性。

对称设计实现了 TX 和 RX PHY 之间的共享布局。

双用途 TX 和 RX PHY,可实现灵活的信号方案。

简化了器件设置,减少了 PLL 要求,降低了功耗和成本。

缺点

简化的设计可能会限制高性能应用所需的某些高级功能。

结论

BoW 不断发展,为光学、存储器和物联网应用提供了性能和成本效益方面的显著进步。随着 BoW 2.1 规范的不断完善,我们诚邀社会各界参与并为这一开放标准做出贡献。即将于 2024 年发布的版本有望增强互操作性并支持新的应用,从而推动半导体行业的创新。

扫码关注

扫码关注