简介

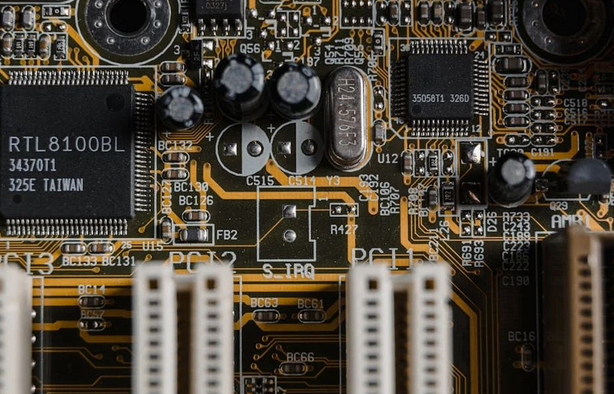

Kintex® UltraScale+™ FPGA在 FinFET 节点中提供高性价比,为需要高端功能(包括 33Gb/s 收发器和 100G 连接内核)的应用提供了经济高效的解决方案。该中端产品系列同时支持数据包处理和 DSP 密集型功能,是无线 MIMO 技术、Nx100G 有线网络、以及数据中心网络和存储加速等应用的理想选择。

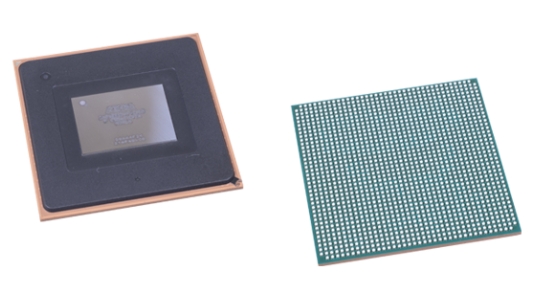

XCKU15P-1FFVA1760E

XCKU15P-2FFVA1760E

规格

系列:XCKU15P

逻辑元件数量:1143450 LE

自适应逻辑模块 - ALM:65340 ALM

嵌入式内存:34.6 Mbit

输入/输出端数量:588 I/O

最小工作温度:0°C

最大工作温度:+ 100°C

数据速率:32.75 Gb/s

收发器数量:76 Transceiver

安装风格:SMD/SMT

封装 / 箱体:FBGA-1760

分布式RAM:9.8 Mbit

内嵌式块RAM - EBR:34.6 Mbit

湿度敏感性:Yes

逻辑数组块数量——LAB:65340 LAB

工作电源电压:850 mV

应用

• 112MHz点对点MWR调制解调器与数据包处理

• 1GHz eBand调制解调器与数据包处理

特征

可编程系统集成

高达1.2M系统逻辑单元

适用于片上存储器集成的UltraRAM

集成100G以太网MAC,支持RS-FEC及150G Interlaken内核

提升系统性能

6.3 TeraMAC DSP计算性能

与Kintex-7 FPGA相比,系统级性能功耗比提升2倍多

16G和28G背板 - 支持各种收发器

中等速度等级可支持2666Mb/s DDR4

降低了BOM成本

最低速度等极的12.5Gb/s收发器

VCXO与fPLL(分频锁相环)的集成可降低时钟元件成本

降低了总功耗

与7系列FPGA相比,功耗降低60%

电压缩放选项支持高性能与低功耗

采用紧密型逻辑单元封装,降低了动态功耗

提高了设计生产力

与Vivado Design Suite协同优化,加快设计收敛

适用于智能IP集成的SmartConnect技术

注:本文部分内容与图片来源于网络,版权归原作者所有。如有侵权,请联系删除!

扫码关注

扫码关注