前面介绍过模拟VCO是通过改变电容充放电电流的大小实现调频的,详见LLC闭环仿真之L6599 VCO建模与工作原理分析。

那么数字环路该怎么实现呢?今天使用PSIM的C Block分享一下。

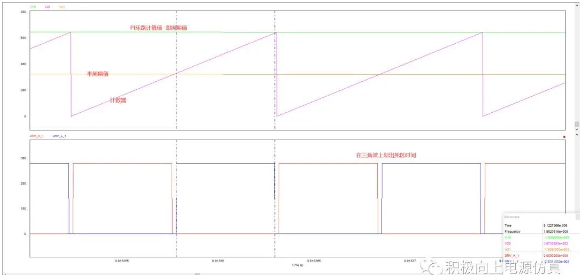

以前沿调制为例,如下图:每个中断周期内,软件通过环路计算出需要的频率(下图绿色直线),然后基于DSP主频内(这里设置的60MHz)累加的计数器(下图三角波),当三角波峰值等于环路计算值时归零(不同的工况有不同的环路输出值,闭环时自动计算),所以数字发波的三角波峰值不固定,而上升斜率固定,并且可以直接归零,这样就得到不同的周期量实现调频;

而模拟仿真是通过给电容充放电,其电压峰峰值固定(ΔV),斜率不固定(跟充电电流相关),且不可直接从最大值归零(电容放电需要时间)。

有了这个三角波后,即可发出想要的驱动,死区时间,轻载调宽移相等都可以通过操作三角波实现。

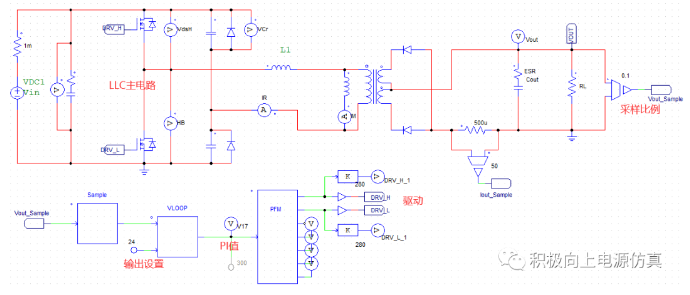

下图为总体仿真原理图:

一、输出采样

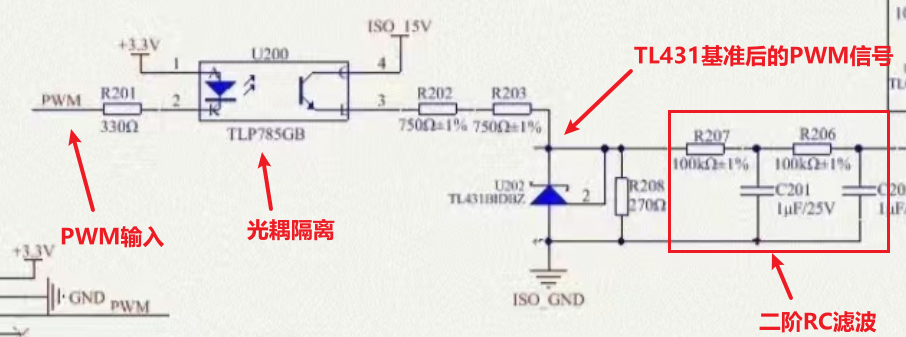

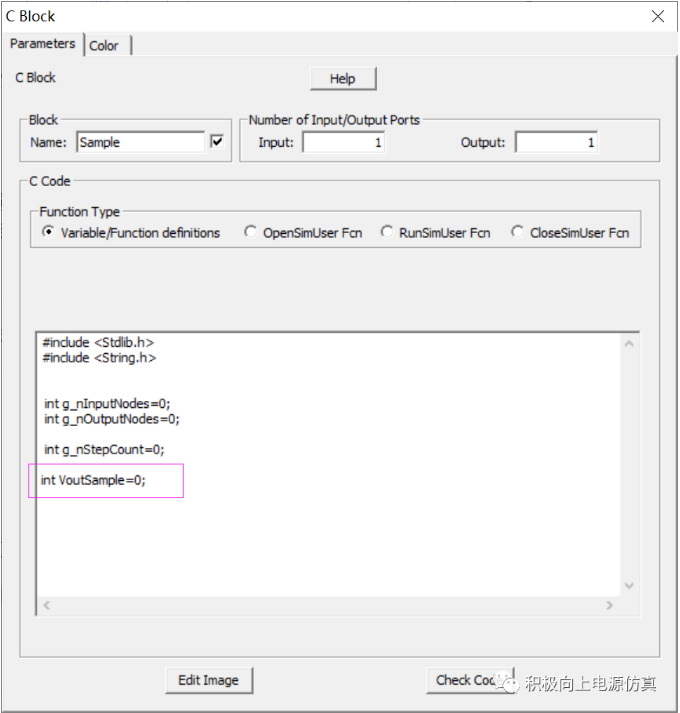

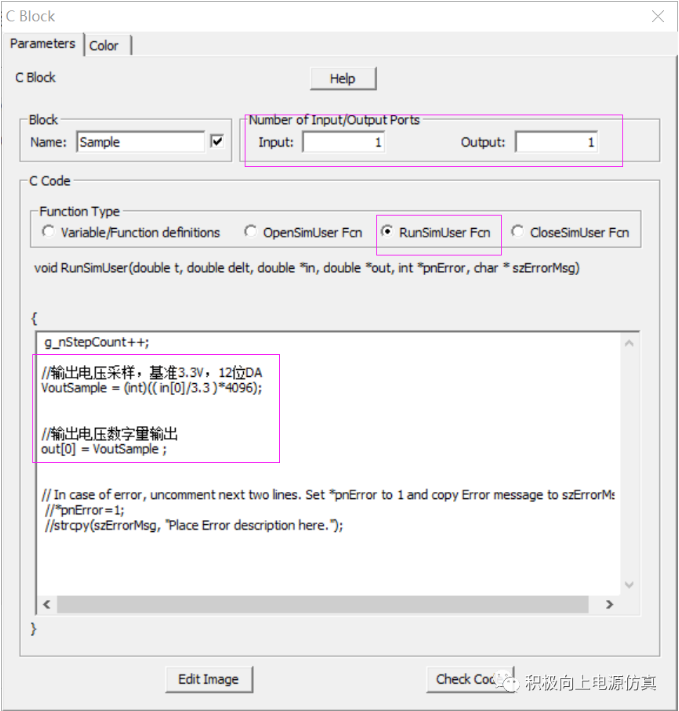

采样比例设置为0.1,电压基准为3.3V,ADC12位精度,若输出为24V,则采样为2.4,转换为数字量即为2.4/3.3*2^12

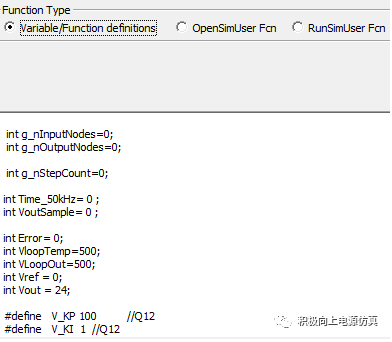

C Block第一个框中定义初始量,其他参数保持默认即可。

在第三个框中读取输入输出数值(第一个输入口为in[0],依此类推)

二、电压环

先定义初始值

然后在第三个框中设置中断和环路计算 g_nStepCount++;//设置中断累加,用以中断计算环路Time_50kHz++; //输出值设定Vout = in[1];//如60M主频的DSP,需要50K中断频率,即60000k/1200=50k,所以仿真跑1200次就进一次中断,进入后归0 if(Time_50kHz==1200) { //计数器清零

Time_50kHz = 0;

//上个模块输出的输出电压采样数字量

VoutSample= in[0];

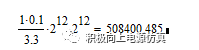

//Q12格式,因前面定义的整型,精度低,所以先把该值*2^12,如下图,然后再通过右移12位(即写代码时人为乘2^12,再用DSP除以2^12),DSP移位比较快,浮点型处理慢

采样比例/基准电压*ADC精度*Q12格式

Vref = (int)Vout*508400>>12;

//输出误差

Error = Vref - VoutSample ;

//简单的PI处理,同样为Q12

VloopTemp = VloopTemp + V_KP*Error;

VLoopOut = (VloopTemp + V_KI*Error)>>12;

//限制最小频率50khz,50K*1500=60M主频

if(VLoopOut>1200)

VLoopOut = 1200;

//限制最大频率250khz,同上

if(VLoopOut<240)

VLoopOut = 240;

}//计算结果输出,即图1绿色线out[0] = VLoopOut;

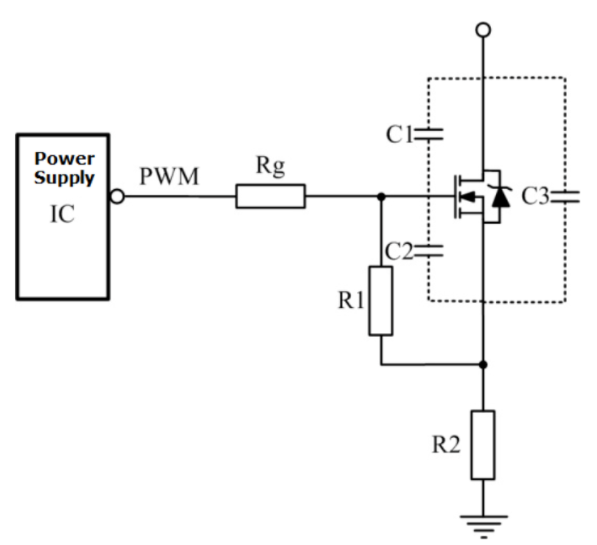

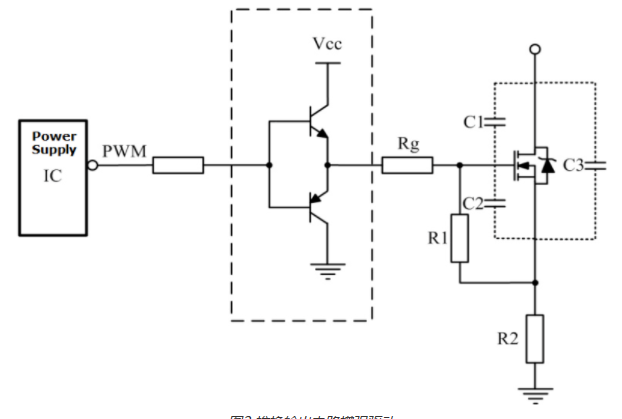

三、发波控制定义完初始值后,通过以主频为步进累加,峰值达到环路输出值后归0,这样就得到一个三角波(图1直角三角形) g_nStepCount++;//PWM周期计数器累加PWM_Cnt++; //读取上个模块的环路周期量Period = in[0] ; //死区时间,如果需要调宽,加大死时间即可。加入条件语句通过Period和Deadtime的函数就可以实现调频+调宽了,比模拟方式实现起来简单多了Deadtime = 20;//半周期HalfPeriod = Period/2; //半周期值以下OUT0出高,然后插入死区,方波两边分各分一半if(PWM_Cnt > Deadtime/2 && PWM_Cnt < HalfPeriod - Deadtime/2){out[0]=1;out[1]=0;}//半周期值以上OUT1出高,死区同上,仔细看三角波很好理解else if(PWM_Cnt > HalfPeriod + Deadtime/2 && PWM_Cnt < Period - Deadtime/2){out[0]=0;out[1]=1;}//死区内均为低电平else{out[0]=0;out[1]=0;}//周期发波完成后计数器归0if(PWM_Cnt==Period)PWM_Cnt=0;如果需要移相,也可能通过处理三角波实现,总之,数字发波比模拟发波确实方便很多,可以玩出各种花样。

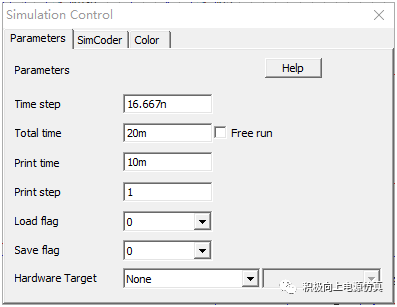

最后,要在仿真器中模拟60MHz主频,将仿真器仿真步长设置为16.667n即可。

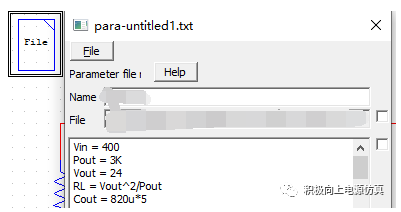

另外PSIM也可以像simplis F11窗口一样将参数定义在file文件中,这样对于参数修改更方便。

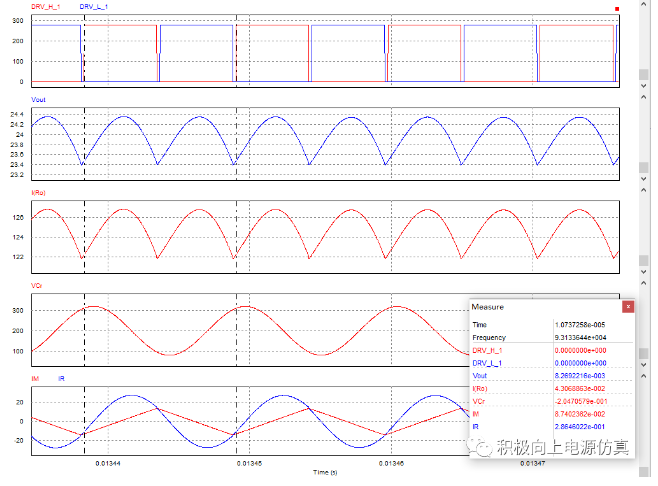

这样仿真就完成了,下面看下仿真波形:

参数都是随意编的,希望能帮助硬件新人简单的理解下LLC软件发波原理吧。

声明:本文转载自吴少琴的模电课 公众号,如涉及作品内容、版权和其它问题,请于联系工作人员,我们将在第一时间和您对接删除处理!

扫码关注

扫码关注