- 全部

- 默认排序

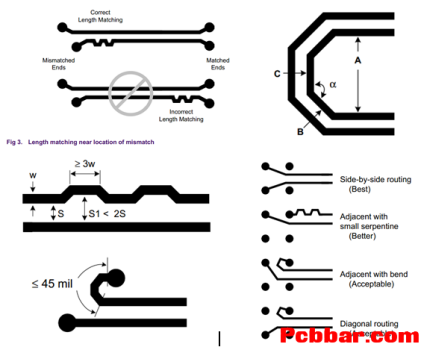

差分走线,信号换层过孔数量,等长长度把控,阻抗控制要求,跨分割的损耗,走线拐角的位置形状,绕线方式对应的插损和回损,布局不妥当造成的一系列串扰和叠层串扰,布局不恰当操作焊盘存在的stub。

串行总线的发展一共目前可以总结分为3个环节时期, 时钟并行总线:小于200MHZ,比如CPCI,PCIX,SDRAM,ISA,PIC 源同步时钟并行总线:小于3200Mbps,比如DDRr1234系列,MII,EMMC 高速串行总线:最高有56NRZ ,比如USB1/2/3/3.1/3.2,PCIE3,PCIE4,SAS3,SAS4.

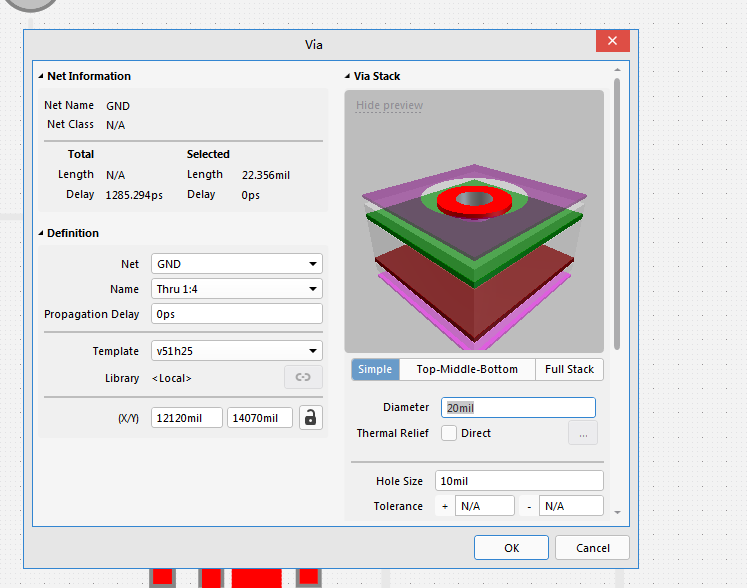

有时候为了为了增大内层的敷铜面积,特别是BGA区域,尤其在高速串行总线日益广泛的今天,无论是PCIE,SATA串行总线,还是GTX,XAUI,SRIO等串行总线,都需要考虑走线的阻抗连续性及损耗控制,而对于阻抗控制,主要是通过减少走线及过孔中的STUB效应对内层过孔进行削盘处理。

熟悉硬件/单片机的工程师,想必对PCIe接口不陌生吧!PCIe是一种高速串行总线接口,主要功能是数据传输,被广泛应用计算机、工业控制等多种领域。若是遇见PCIe的PCB项目该如何做?不如来看看这篇文吧!本文将介绍PCIe接口的PCB设计技术

PCI-Express,简称“PCI-e”是一种高速串行计算机扩展总线标准,PCI-E属于高速串行点对点双通道高带宽传输,所连接的设备分配独享通道带宽,不共享总线带宽,它的主要优势就是数据传输速率高。PCI-E2.0和PCI-E3.0主要存

在高速串行通信系统中,差分阻抗的精确控制是实现信号完整性和降低电磁干扰的关键因素,对电子工程师来说,理想中的差分阻抗是100Ω,但由于实际布线原因,如接地屏蔽的布局,很难实现。如果要实现这个设计,工程师需要选择具有宽泛差分阻抗匹配能力的Se

在高速串行通信系统中,差分阻抗的精确控制是实现信号完整性和降低电磁干扰的关键因素,对电子工程师来说,理想中的差分阻抗是100Ω,但由于实际布线原因,如接地屏蔽的布局,很难实现。如果要实现这个设计,工程师需要选择具有宽泛差分阻抗匹配能力的Se

高速串行接口简介

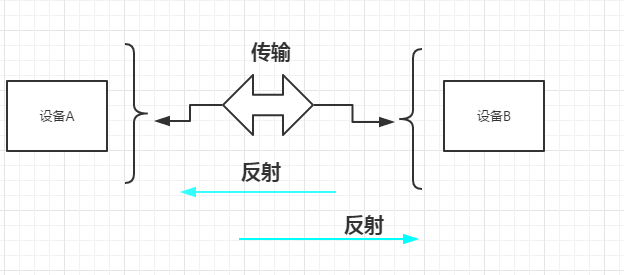

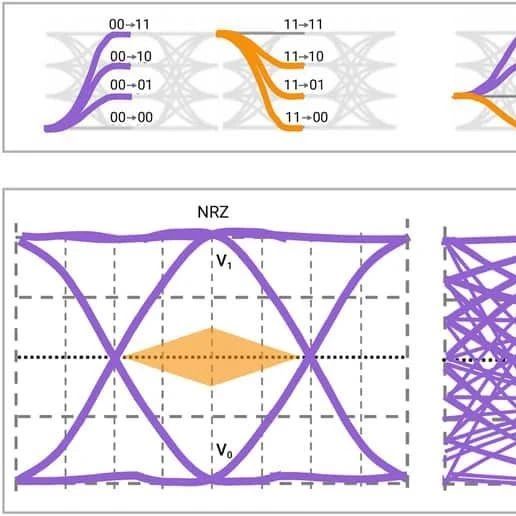

在计算机之间以及计算机内部各部分接口之间有两种数据传输方式:并行数据传输方式与串行数据传输方式。并行数据传输方式通过多个通道在同一时间内传播多个数据流;而串行数据传输方式在同一时间内只传输一个数据流。过去,前者,并行数据传输方式,是主流的数据接口,而后者常用于设备之间的远距离、低速率的数据通信以及设

在高速串行通信系统中,随着数据传输速率的不断提升,传统的并行通信方式受限于信号同步与感染问题,逐渐难以满足现代高速数据传输的需求,因此,时钟数据恢复技术应运而生,成为实现高速、稳定串行通信的关键技术之一。1、时钟数据恢复是什么?时钟数据恢复

扫码关注

扫码关注