- 全部

- 默认排序

1、MD5概念MD5信息摘要算法(MD5 Message-Digest Algorithm),一种被广泛使用的密码散列函数,可以产生出一个128位(16字节)的散列值(hash value),用于确保信息传输完整一致。输入任意长度的数据经过处理,输出都是128位的信息(数字指纹)。不同的输入得到的不

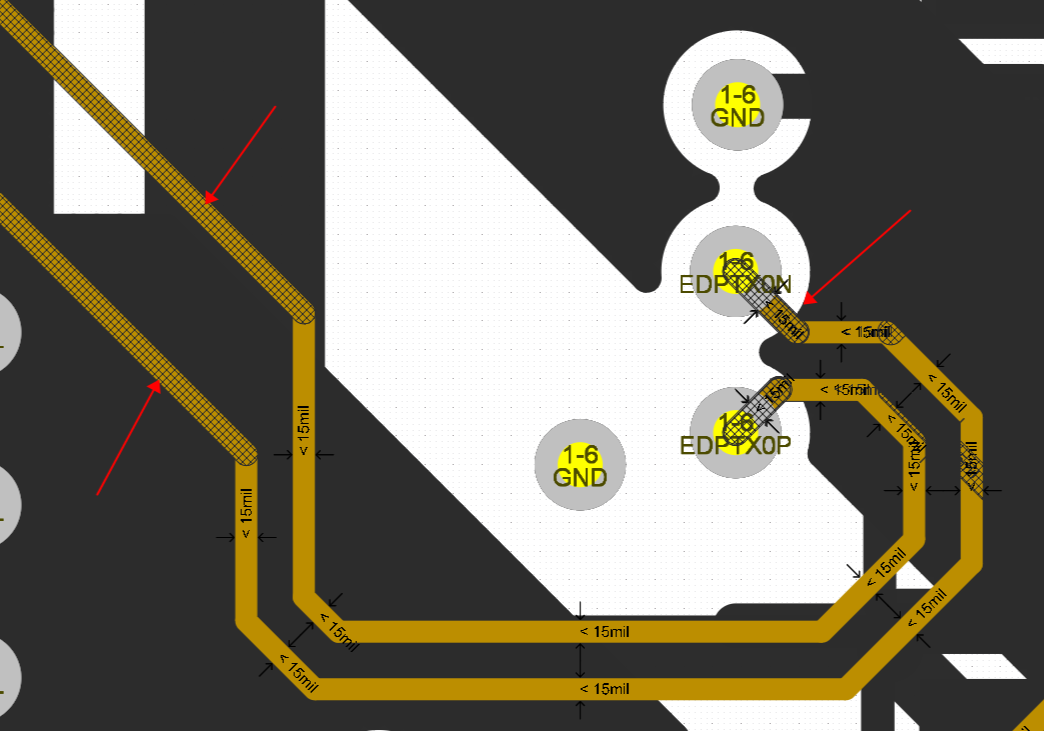

PADS蛇形等长处理

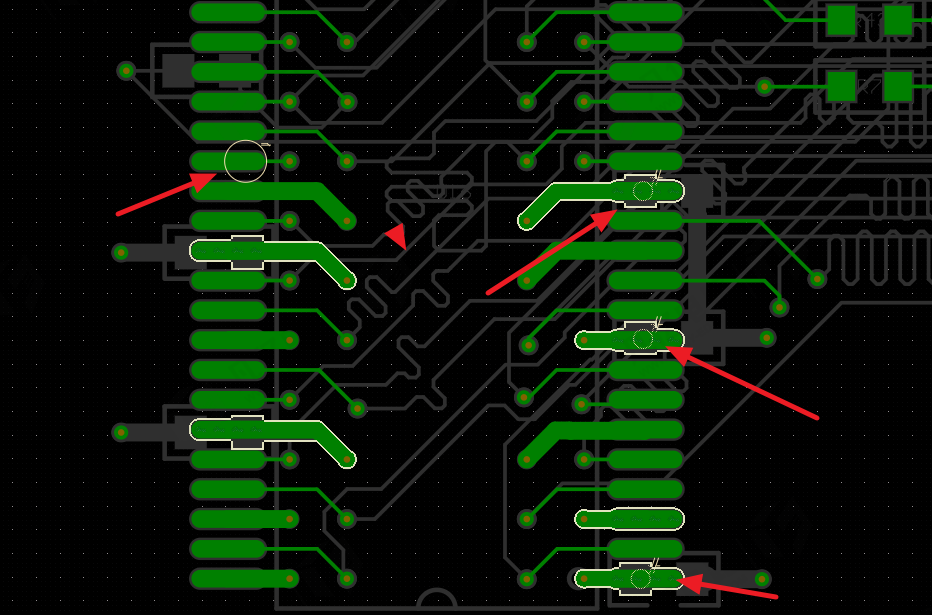

在做PCB设计时,为了满足某一组所有信号线的总长度满足在一个公差范围内,通常要使用蛇形走线将总长度较短的信号线绕到与组内最长的信号线长度公差范围内,这个用蛇形走线绕长信号线的处理过程,就是俗称的PCB信号等长处理。如图6-59示。图6-59

在DDR的设计中,需要对数据线及地址线进行分组及等长来满足时序匹配,通常DDR的数据线之间的长度误差需要保证在50mil以内,地址线的长度误差需要保证在100mil以内。执行菜单命令【设计】-【规则】或者使用快捷键DR打开规则约束器,在“H

示例代码说明执行主程序初始状态执行代码前 5 句准备调用子程序调用子程序子程序寄存器入栈保护计算字符串长度返回结果寄存器出栈返回指令ret在任何一门编译型语言中,栈操作都是非常重要的。利用栈的后进先出特性,可以很方便的解决一些棘手的问题,以至于 CPU 单独分配了 push 和 pop 这两个命令来

Altium Designer走差分线出现网格是什么原因?答:如图1所示,在AD软件中走差分线出现网格主要是差分线的未耦合长度没有满足差分规则所导致的,未耦合长度指的是差分线中不满足差分间距的长度。图 1 差分走线出现网格走线当出现这种错误

之前我们学习了前向串音的电容特性,接下来是学习后向串音的反射,一般来说,很多工程师都会更加重视前向串音,但这是错误的思维,今天谈谈为什么要更加重视后向串音,希望对小伙伴们有所帮助。首先,与前向串音不同,后向串音脉冲幅值与线路长度无关,其脉冲

PCB板目前最严重的问题莫过于电磁兼容(EMC)和散热问题,面对这些问题,工程师在PCB设计时都会发愁如何根据辐射决定环路面积,那么今天就回答这个问题,来看看吧!一般来说,无终点传输线的反射情况决定了线路的最大长度,由于对产品的EMI辐射有

1、存在开路和短路。2、地址线的等长是ic到ddr的长度。3、时钟线布线错误,应该从u16到r46再到u1。4、时钟线等长错误,是SDRAM段到电阻和电阻段ic的线一样长。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PC

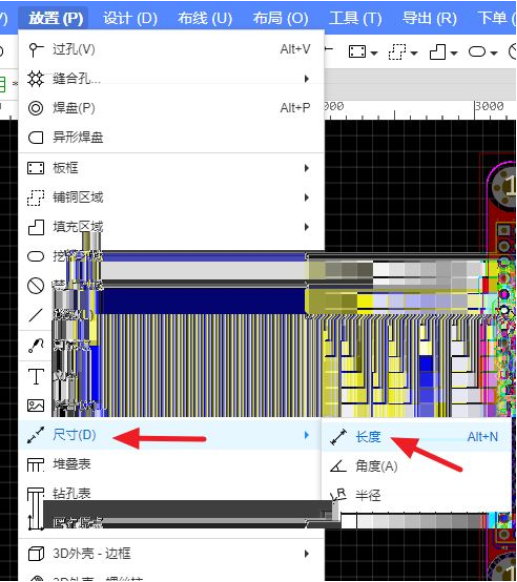

为了使设计者或生产者更方便地知晓PCB尺寸及相关信息,在设计的时候通常考虑到给设计好的PCB添加尺寸标注。尺寸标注方式分为长度、角度、半径等形式,下面对最常用的长度标注及半径标注进行说明。1.1 长度标注1)尺寸标注一般放置在机械层,选择一

1.多处焊盘出线问题,焊盘中心出线至外部才能拐线处理。2.过孔没有网络3.焊盘出线尽量耦合、长度相等,存在多处相同问题。4.差分等长拱起处间距要在一倍间距到两倍间距之间。差分没有做对内等长差分走线不耦合需要加宽的走线宽度不一致多处存在开路过

扫码关注

扫码关注