PCB板目前最严重的问题莫过于电磁兼容(EMC)和散热问题,面对这些问题,工程师在PCB设计时都会发愁如何根据辐射决定环路面积,那么今天就回答这个问题,来看看吧!

一般来说,无终点传输线的反射情况决定了线路的最大长度,由于对产品的EMI辐射有强制性要求,因此环路区域的面积和线路长度都受到限制,如果采用非屏蔽外壳,这种限制将直接由PCB来实现。

注意:若是在异步逻辑电路设计中采用串联端接负载,必须要注意出现准稳性,特别是对称逻辑输入电路无法确定输入信号是高还是低,而且可能导致非定义输出情况。

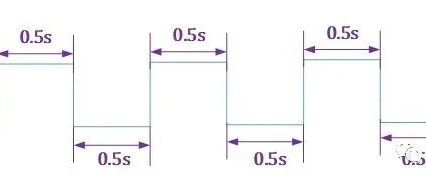

对于频域中的逻辑信号,频谱的电流幅度在超出逻辑信号带宽(=1/π.tr)频率上与频率的平方成反比,用角频率表示,环路的辐射阻抗仍随频率平方成正比,因而可计算出最大的环路面积,它由时钟速率或重复速率、逻辑信号的上升时间或带宽及时域的电流幅度决定。电流波形由电压波形决定,电流半宽时间约等于电压的上升时间。

电流幅度可用角频率(=1/T.tr)表示为:l(f)=2.1.tr/T

其中:l=为时域电流幅度;T=为时钟速率的倒数,即周期;tr为电压的上升时间,约等于电流半宽时间tH。

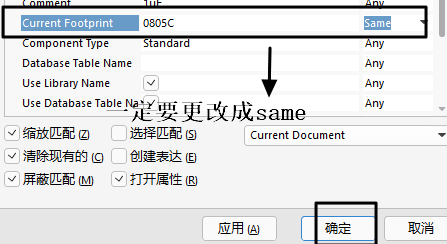

从这一等式可计算出某种逻辑系列电路在某一时钟速率下最大环路面积,表5给出了相应的环路面积。最大环路面积由时钟速率、逻辑电路类型(=输出电流〉和 PCB上同时存在的开关环路数量n决定。

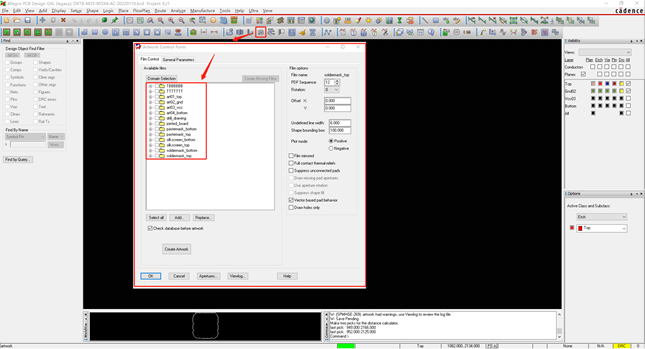

如果所用的时钟速率超过30MHz,就必须要采用多层电路板,在这种情况下,环氧树脂的厚度与层数有关,在60至300um之间。只有当PCB上的高速时钟信号的数量有限时,通过采用层到层的线路进行仔细布线,也可在双层板上得到可以接受的结果。

注意:在这种情况下,如采用普通DIL封装,则会超过环路面积的限制,一定要有另外的屏蔽措施和适当的滤波。

所有连接到其它面板及部件的连接头必须尽可能相互靠近放置,这样在电缆中传导的共模电流就不会流入PCB电路中的线路,另外,PCB上参考点间的电压降也无法激励(天线)电缆。

为避免这种共振影响,必须使靠近接头的参考地和PCB上电路的接地层、接地网格或电路参考地隔开,如果可能,这些接地片应接到产品的金属外壳上,从这个接地片上,只有高阻器件如电感、电阻、簧片继电器和光耦合器可接在两个地之间,所有的接头要尽可能靠近放置,以防止外部电流流过PCB上的线路或参考地。

扫码关注

扫码关注