- 全部

- 默认排序

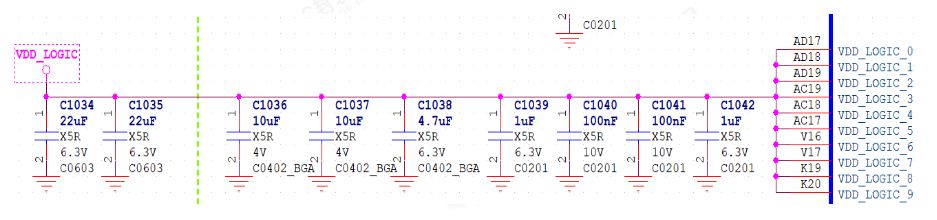

RK3588 VDD_LOGIC电源PCB设计1、VDD_LOGIC的覆铜宽度需满足芯片的电流需求,连接到芯片电源管脚的覆铜足够宽,路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚路径都足够。2、如图1所示,原理

1、VDD_NPU的覆铜宽度需满足芯片的电流需求,连接到芯片电源管脚的覆铜足够宽,路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚的路径都足够。2、VDD_NPU的电源在外围换层时,要尽可能的多打电源过孔(7个以

RK3588 VDD_CPU_LIT电源PCB设计1、VDD_CPU_LIT覆铜宽度需满足芯片电流需求,连接到芯片电源管脚的覆铜足够宽,路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚的路径都足够。2、VDD_C

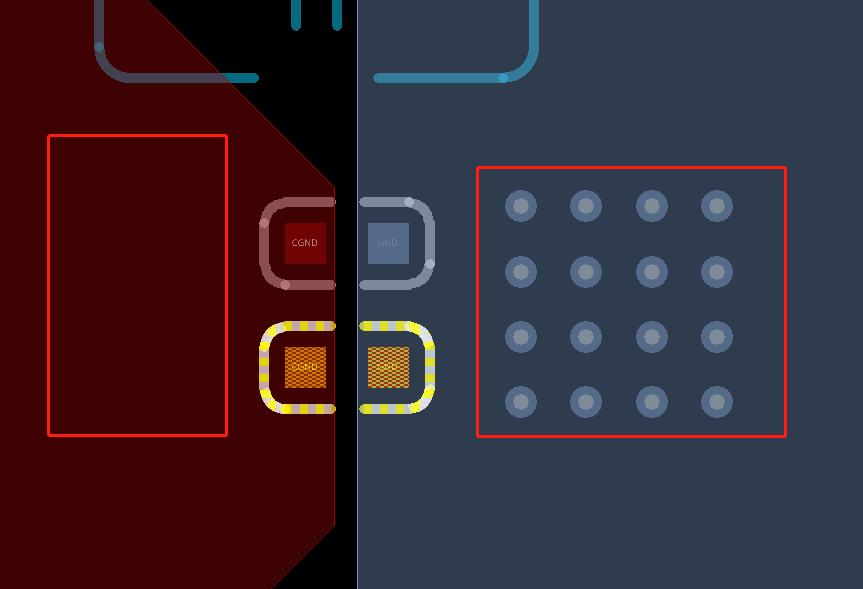

1.dcdc需要单点接地,地网络焊盘连接到一起在芯片下方打孔2.反馈信号应从电源最末端连接3.焊盘出线要从短边出线避免长边出线;走线避免直角锐角4.电源输出主路径应该加宽载流5.大电感下方应做铺铜挖空处理,相邻大电感需要朝不同方向垂直摆放6

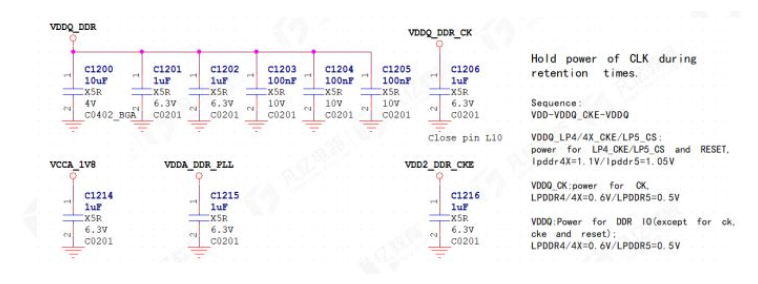

RK3588 VCC_DDR电源PCB设计1、VCC_DDR覆铜宽度需满足芯片的电流需求,连接到芯片电源管脚的覆铜足够宽,路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚的路径都足够。2、VCC_DDR的电源在外

PCB设计,细节要牢记,技巧规范,别忘记。元件选择,要慎重权衡,性能优化,细节考虑。电路布局,尺寸精确,差分信号,清晰准确。地平面铺,阻抗匹配,多层堆叠,功耗降低。信号路径,长度平等,串扰减小,信噪比增。参考设计,莫忽略,静电防护,接地要密

Cadence allegro学习笔记第一节 启动与板框的制作1、启动操作启动PCB Editor图标,弹出对话框后选择Allegro PCB Designer后择OK进入界面。 选择File文件菜单选择New新建弹出下面对话框。设置保存路径、输入文件名称、选择Board后选择OK

随着电子技术的飞速发展,高速电路的设计和制造已成为电子工程师的重要任务,在高速电路中,路径回流问题是一个很关键的问题,它对电路的性能和稳定性产生了重要影响,其中芯片互连、铜面切割和过孔跳跃最为复杂常见,本文将从这三方面出发介绍。1、芯片互连

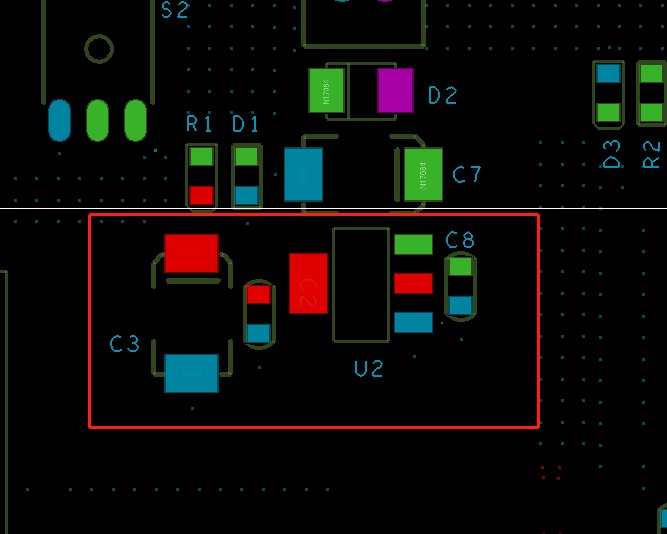

跨接器件的地过孔打在地焊盘旁边,如右侧的电路地打孔一样:注意变压器上除了差分信号,其他的信号走线20MIL:注意走线规范,不要从电阻电容内部穿线,更改此信号的路径:注意扇孔间距保持,不要吧负片层割裂了:注意电路地与机壳地之间间距2MM:RX

注意下器件整体对齐:器件位号不要覆盖再焊盘上,设计完成之后都是需要调整器件丝印:晶振需要就近靠近IC对应管脚放置:走线注意规范,不要从电容内部走线,更换下路径:建议看下此处VBAT 20MIL是否满足载流:上述一致问题,从电阻内部走线:以上

扫码关注

扫码关注