- 全部

- 默认排序

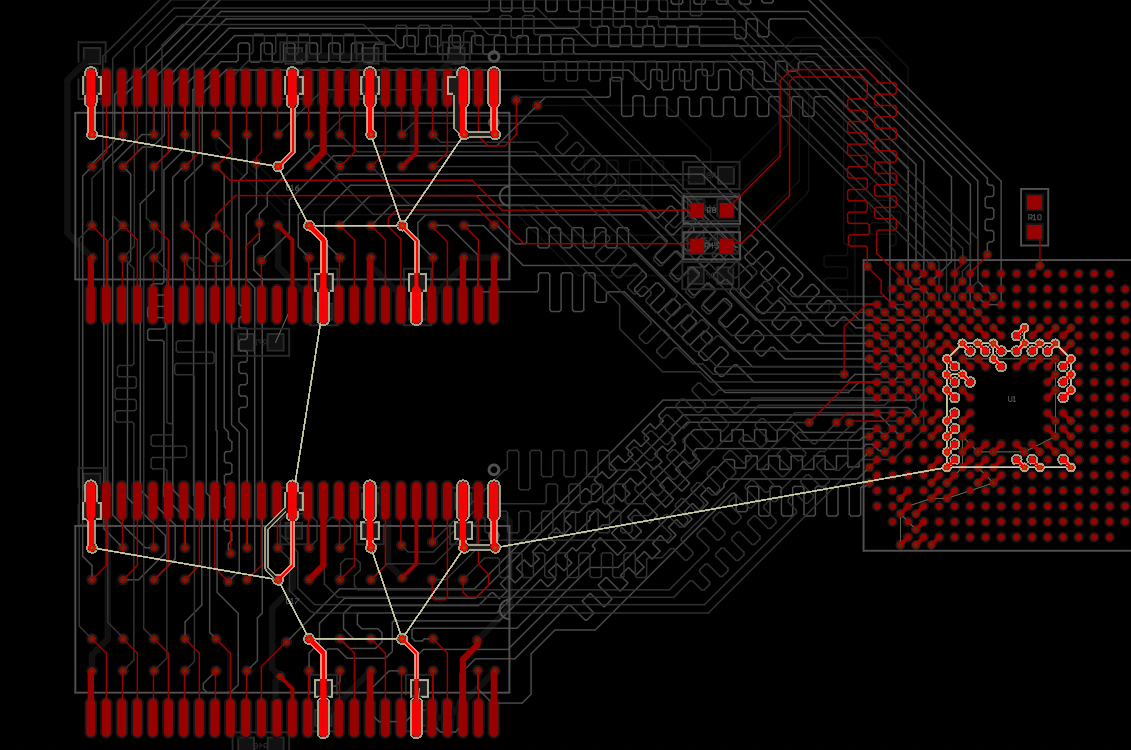

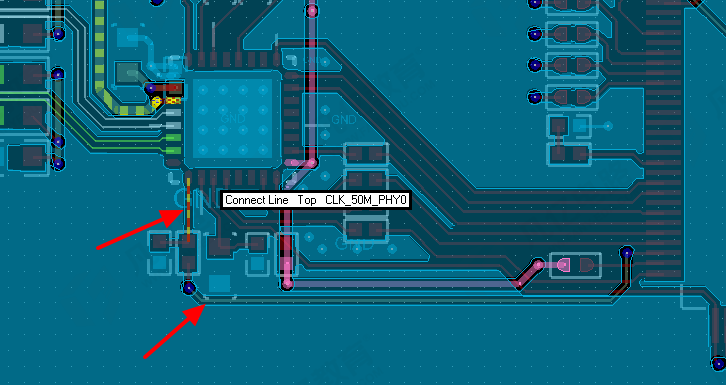

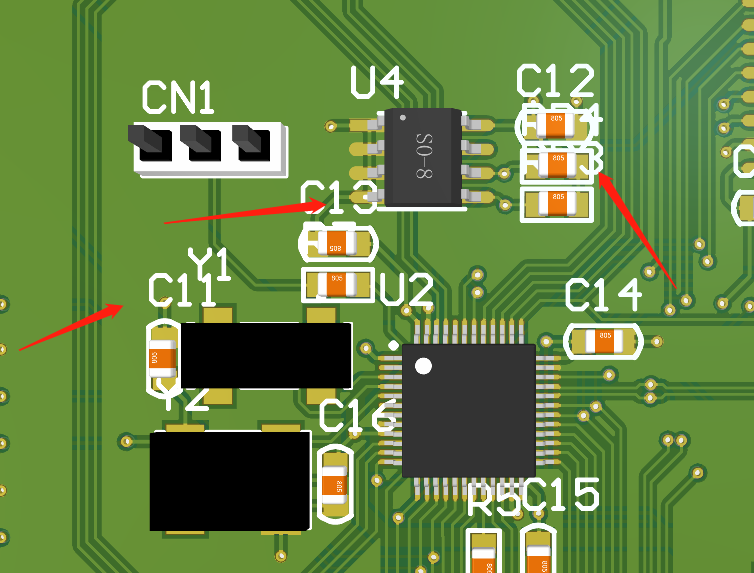

电源网络DP3V3全都是飞线显示,内层存在电源层赋予对应网络即可:电源平面层没有赋予网络,导致存在飞线网络没有连接:焊盘扇孔注意对齐,都没对齐,需要修改:类似这种过孔内存在线头的自己删除:注意走线优化:地址线内还存在误差报错:不需要拉线的地

晶振注意包地:缝合孔不需要打太密集,间距150mil放置一个即可:过孔不要打在焊盘上,自己注意调整:多处存在这样的情况,自己更改。铺上铜皮就不用走线了:走线不能在器件内部:晶振是需要保持净空的,不能走线:以上评审报告来源于凡亿教育90天高速

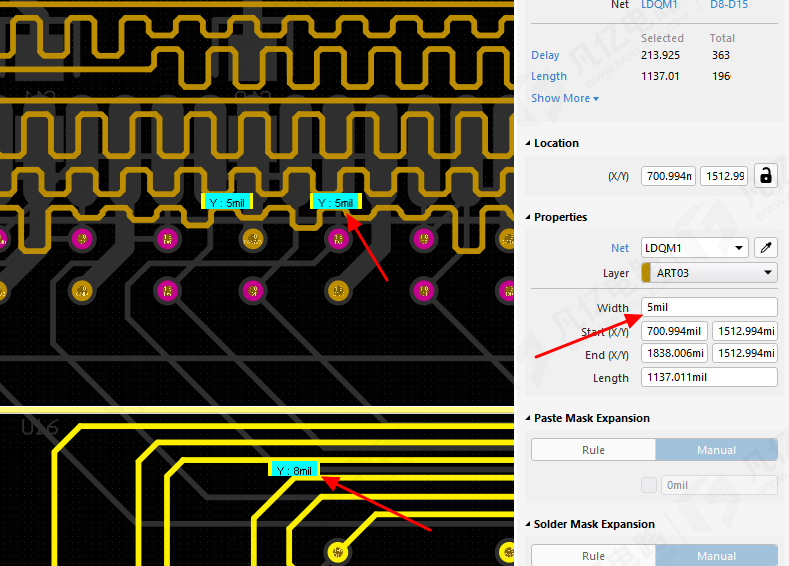

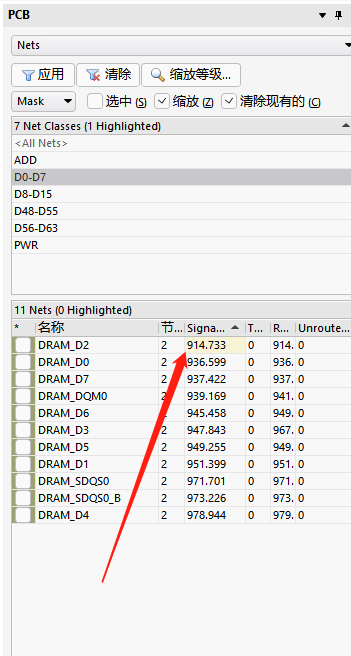

走线保持3w间距等长绕线尽量咬合电容尽量靠近焊盘,电源走线加粗时钟线等长错误以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/item

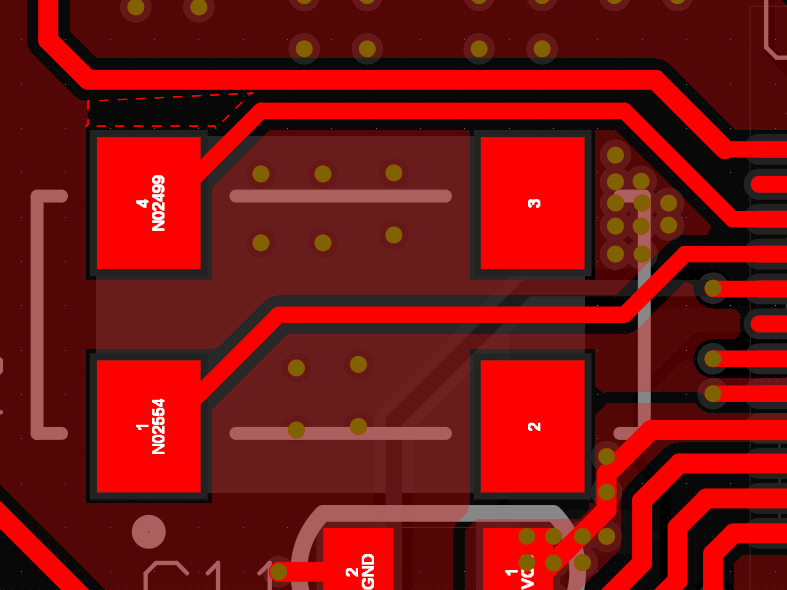

走线在焊盘中,走线宽度不要超过焊盘,可以拉出后在加粗铺铜不要有直角电感下面不要走线以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/i

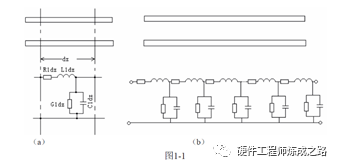

前几天写的关于示波器的文章,提到了探头上面的寄生电容,两个导体并排放置,天然就是一个电容。忽然想到,现如今HDMI 线里面的信号速率到上Ghz,HDMI线也做到了十几米,这么长,等效电容肯定不小啊?这怎么能传呢?信号不都被寄生电容滤波滤没了么?虽说这个时候也能用均匀传输线理论,集总参数模型,分布参数

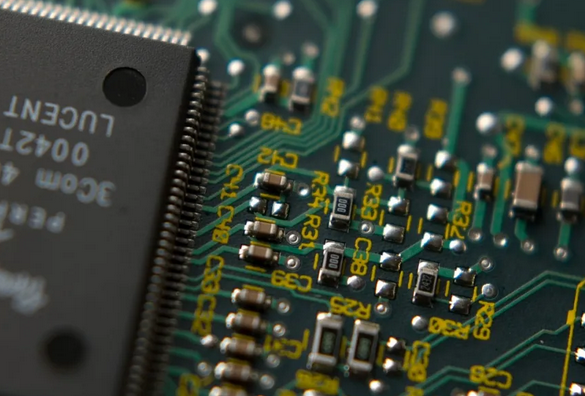

如果观察许多大佬的硬件电路设计,很容易发现他们都会放去耦电容,这样的做法是可以消除电源噪声,保障关键元件如ROM、RAM等的稳定工作,但很多小白不太清楚,所以今天我们来讲讲为什么要这么摆放去耦电容,需要注意什么?一般来说,PCB板上的走线、

寄生电感怎么来的

最近在整理电感的内容,忽然就有个问题不明白了:寄生电感怎么来的呢?一段直直的导线怎么也会存在电感,不是只有线圈才能成为电感吗?想到以前看的书,这个寄生电感的存在大家都默认是有的,貌似也没有人怀疑这个东西是真的存在吗(还是只有我没怀疑)?说到芯片,就是引脚寄生电感,走线长点,就是引线电感这些东西,说到

等长存在误差报错2.注意地址线之间等长也需要满足3W规则3.尺寸走线需要优化一下,尽量不要走直角4.地址线等长存在误差报错后期自己调整一下时钟差分信号中高端匹配电阻应该靠近T点放置等长可以在优化一下,满足3W的前提尽量紧凑一些,提高空间利用

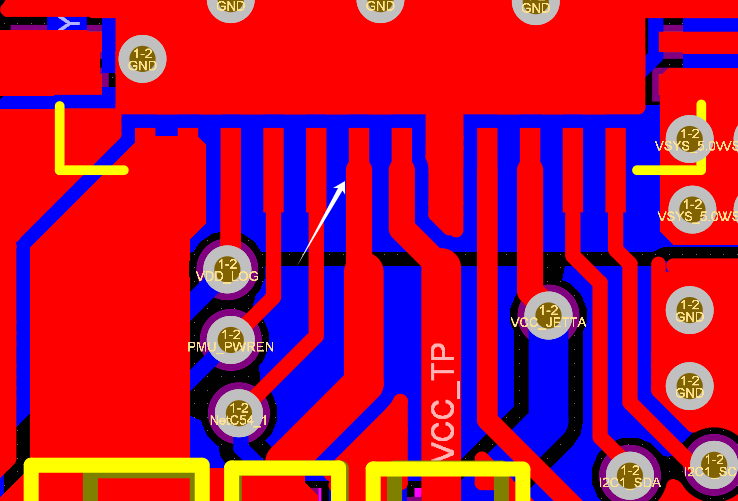

时钟走线包地打孔处理差分对内等长错误,按照规范绕线变压器下方铺铜挖空多处尖细铜皮rx、tx需要分别建立等长组,控制100mil误差等长以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教

器件丝印要么重叠,要么就覆盖在焊盘上,都调整下器件丝印:上述一致原因:电池信号走线需要加粗:软件内多处存在此孤铜没有割除:晶振底部净空,不要有走线:上述一致原因: 打孔尽量打对齐:过孔不要打在焊盘上:以上评审报告来源于凡亿教育90天高速PC

扫码关注

扫码关注