- 全部

- 默认排序

在PCB制造中,波峰焊是极为关键的环节,波峰焊焊接的好坏将直接影响到产品的性能和可靠性。为了提升波峰焊焊接品质,确保PCB产品的优势,电子工程师必须从多方面提升。1、设计规则优化PCB布局,减少焊接点之间的距离,提高焊接效率;合理规划走线,

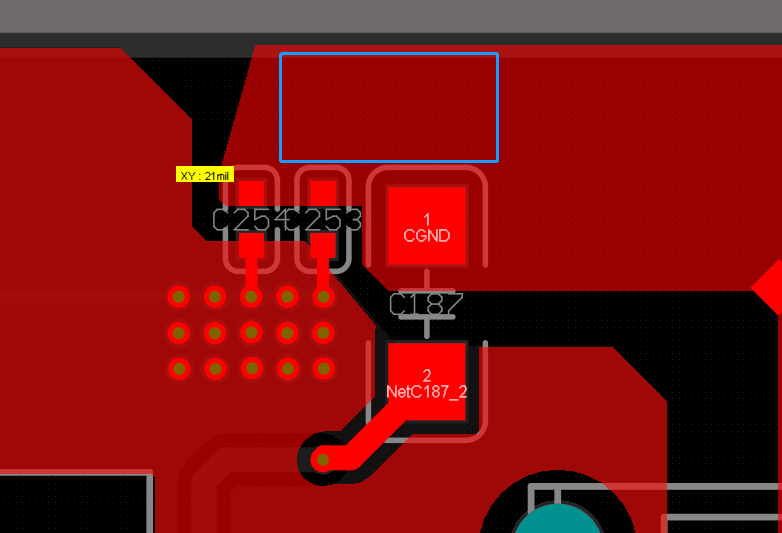

AD软件中怎么添加不同元素之间的间距规则呢答:AD软件提供了某一个元素针对其他元素之间的间距规则的设置。首先执行菜单命令【设计】-【规则】或者快捷键DR打开规则约束编辑器,然后在间距规则Clearance里面添加一个新的规则,如图1所示图1

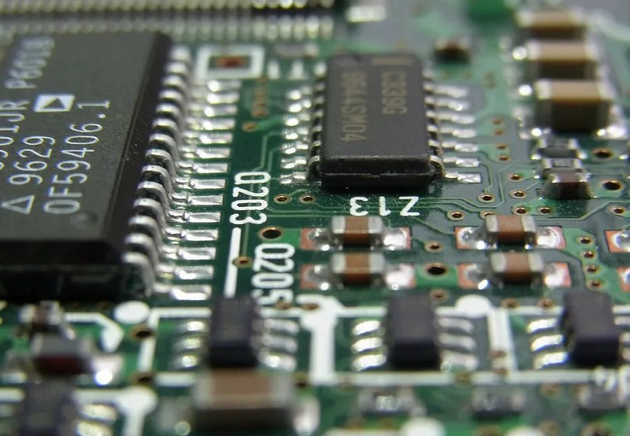

板载芯片(COB)技术是现代电子制造中的重要环节,其表面处理的好坏将直接决定芯片与基板的结合能力及整体性能,那么电子工程师如何做好板载芯片的表面处理?1、设计规则在进行COB表面处理前,设计阶段的规划至关重要,应遵循以下规则:合理安排芯片布

详解常见的BGA扇孔的规则设置答:很多时候由于规则没设置正确,会导致BGA扇孔失败,下面介绍几种常见的BGA规则设置:一、1.0mm BGA1)过孔间过一根线:使用10-22的孔,线宽6mil,线到孔盘5.5 mil2)过孔间过一根线:使用

对电子工程师来说,电子设计过程很漫长且繁琐,其中有个环节是PCB原理图传递给版图设计,这就很考验工程师的经验及操作水平,下面将总结版图设计的准备工作及注意事项,希望对小伙伴们有所帮助。1、版图设计的准备工作①根据要求设置设计规则;②为常用层

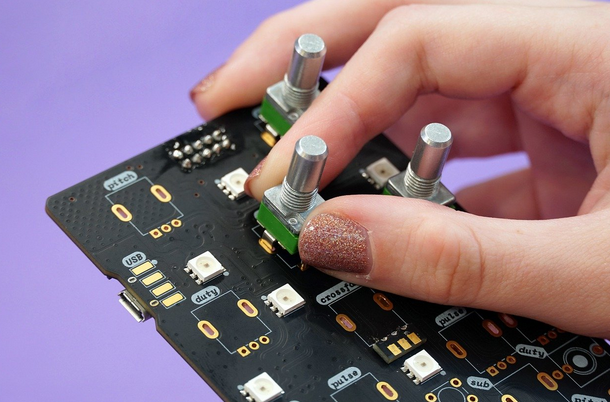

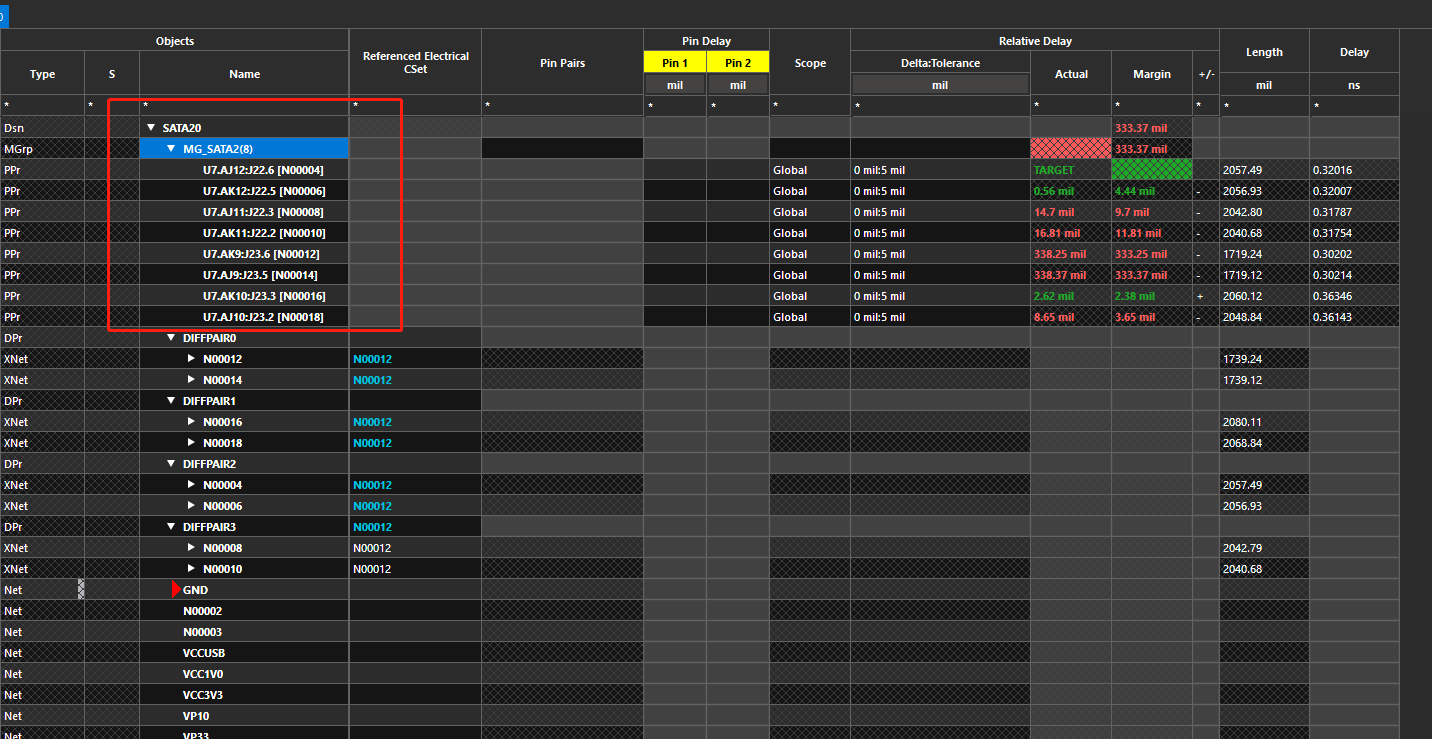

跨接器件旁边尽量多打地过孔2.焊盘出线需要优化一下3.差分走线不满足阻抗线距规则4.晶振下面不要放置器件和走线,包地需要在地线上打过孔5.注意打孔尽量不要打在焊盘中心6.走线一层连通,不用打孔7.走线需要优化一下,尽量45度8.RX等长误差

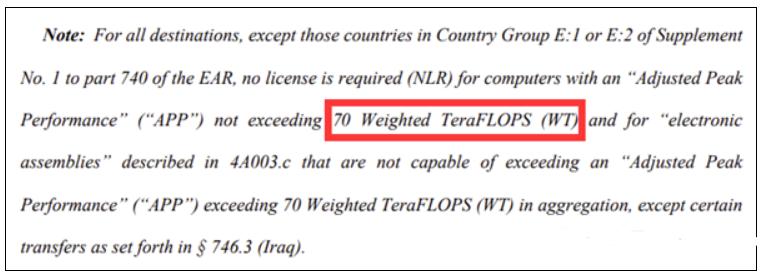

近年来,美国继续加大对华AI芯片的出口限制,范围已经升级到了英伟达的“特供版”AI产品,即H20、RTX4090D等。近日,美国公布了新的限制规则,将在今年4月4日正式生效,4A003类目下 “数字计算机”、“电子组件”及其相关设备和“组件

随着信号上升沿时间的减小,信号频率的提高,电子产品的EMI问题,也来越受到电子工程师的重视。高速pcb设计的成功,对EMI的贡献越来越受到重视,几乎60%的EMI问题可以通过高速PCB来控制解决。1高速信号走线屏蔽规则如上图所示:在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果

随着科技的快速发展,高速信号逐渐替代低速信号,成为许多电子系统的最佳选择,然而高速信号最大的缺点在于其稳定性和可靠性不如低速信号,这就需要靠走线系统来弥补。那么如何走线,保证高速信号的质量?1、屏蔽规则在高速PCB设计中,时钟等关键高速信号

差分线对内等长误差5mil,同一组差分误差5mil规则要分开进行设置,后期自己处理一下2.焊盘出线不要走直角3.差分对内等长尽量在不耦合处进行等长4.注意器件摆放不要超出板框5.差分走线要耦合走,后期自己优化一下6.后期自己在地平面铺铜,把

全站最新内容推荐

- 1加码技术,打破困境,PSPice电路仿真助你解锁职场新高度!

- 2简谈稳压二极管和普通二极管的区别

- 3贴片元件如何拆卸及焊接?

- 4盘点电子工程师必须了解的21个电路

- 5英伟达GB300芯片受阻,存在过热问题

- 6WARELEO李增原创H04课程大纲的安排课程中内容及工具及课程的重点学习办法的讲解

- 7WARELEO李增原创H03根据自己的关注知识点和所需要的知识来选择需要的图书包邮递

- 8WARELEO李增原创H02理工男生李老师的介绍从51单片机驱动到FPGA到仿真设计之路

- 9WARELEO李增原创H01信号电源完整性设计与HFSS射频天线设计仿真验证研修课程主题

- 10WARELEO李增:反射仿真的信号观察办法及时域串扰的仿真设置及观察技巧

扫码关注

扫码关注