- 全部

- 默认排序

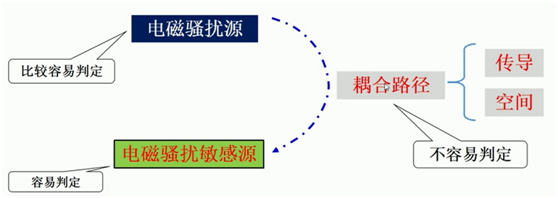

如何分析一个电磁兼容的问题?分析一个电磁兼容的问题需要从三个方面入手:骚扰源敏感源耦合路径找到这三个因素后,再决定去掉哪一个。只要去掉一个,电磁兼容的问题就解决了。例如,当骚扰源是雷电,敏感源是电子线路时,我们能做的就是消除耦合路径(因为没法去掉骚扰源,我们没法让自然界不产生雷电吧)。 耦合路径分为

在单片机系统中,干扰信号的耦合方式多种多样,这些耦合方式将决定了干扰源如何对单片机系统产生影响,如果想设计稳定性高的单片机,了解这些耦合方式是很有必要的。1、直接耦合直接耦合是最直接的方式,也是单片机系统中常见的一种方式。干扰信号可能通过电

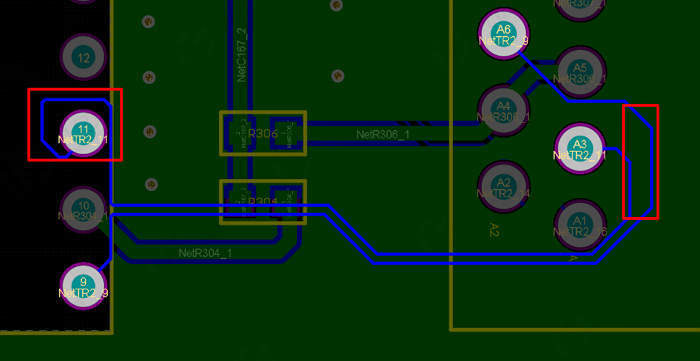

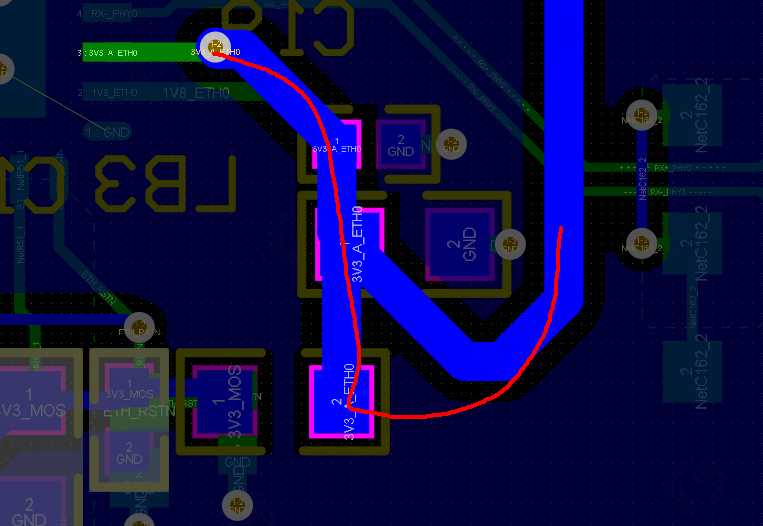

注意地址线之间等长需要满足3W间距规则2.差分对内等长凸起高度不能超过线距的两倍蛇形走线需要优化,等长尽量使用钝角,不要用圆弧或者直角,走线能拉直尽量拉直差分对内等长需要优化,原则哪里不耦合就在哪里绕等长走线到焊盘间距太近,后期容易造成短路

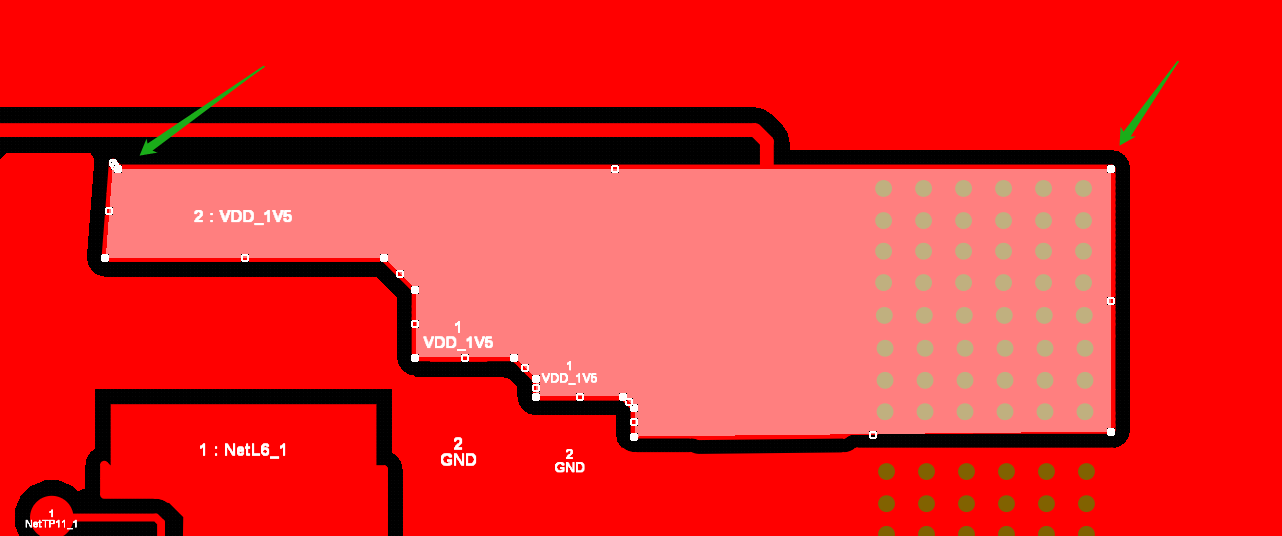

注意铜皮形状尽量钝角,不要直角以及尖角,类似情况自检修改下:走线也不能出现直角:电感内部的铜皮挖空处理:过孔按照对应的电流大小计算数量加2 或者4个裕量就行了:差分进过孔也是需要耦合连接的,优化下:注意下等长线之间需要满足3W间距:避免高速

等长绕线应在引起不等长处绕线,差分出焊盘应尽快耦合数据线满足3w间距要求,rx、tx分开布线不要伴随布线多处焊盘不完全连接,多处 细长铜皮未处理以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫

在PCB设计中,很多工程师会遇见各种问题,其中之一是差分对可以不同层走线吗?答案是可以的,这种设计策略旨在减少电磁干扰和信号损耗,特别是在高速数据传输和射频(RF)应用中。在PCB中,差分信号是一种通过两条相互耦合的传输线(即差分对)来传输

电源输入按照原理图顺序从第一个器件连接时钟信号走线包地打孔处理信号线保持3w间距要求等长绕线从引起不等长端绕线差分走线尽量耦合,减少不必要绕线以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码

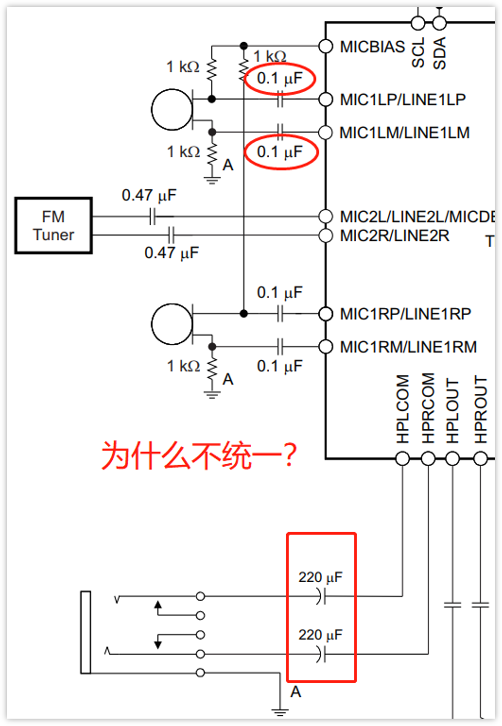

输入阻抗,输出阻抗,这两个参数似乎没那么重要,但事实并非如此。下面说下我的看法吧。 一个问题音频中的耦合电容从0.1uF-220uF都有,这是有病吗?都是用作隔离直流的,怎么就不能统一呢?明白这个问题其实很简单,我们看信号是如何传输就容易明白了。这里就讲一个电路

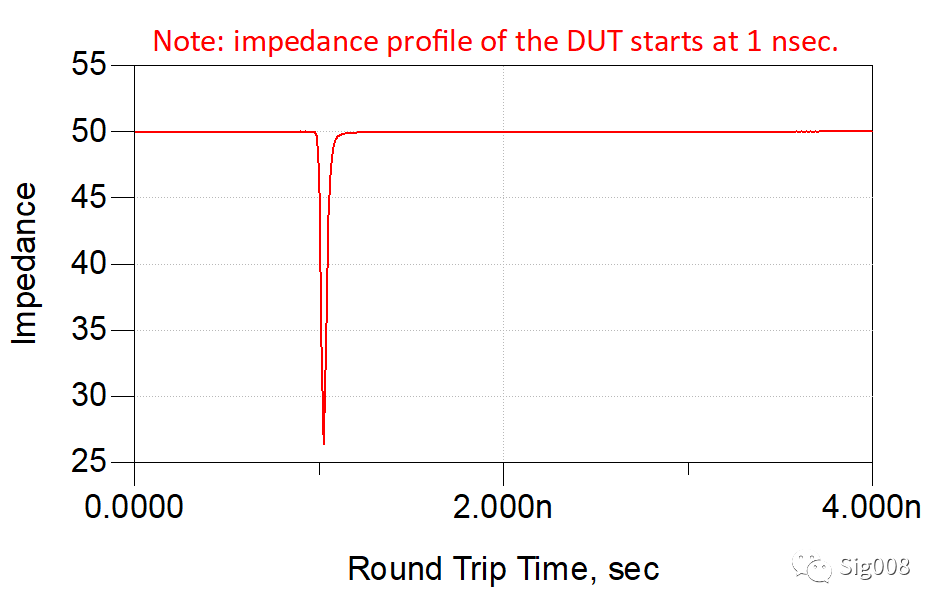

单从焊盘这一点来看,可以看到阻抗一般会比较小,但是对信号未必造成比较大的影响,可问题就在于,整个链路的阻抗不连续点不止这一处;比如,信号BGA处的焊盘,扇出孔,连接器等都是阻抗不连续处,那么这些地方和电容的焊盘就会互相影响,我们来看S参数:可以看到,红色为仅有电容焊盘时的反射,在与扇出孔级联后会变得

片式电感器,又称为片式电感元件,是一种用于电路中的电感器件。它的名称来源于其外观形状,呈片状结构。在电子电路中,片式电感器通常用于滤波、隔离、耦合、共模抑制等功能。01片式电感器基本结构片式电感器通常由多个薄片状的导磁材料堆叠而成。每个薄片

扫码关注

扫码关注