- 全部

- 默认排序

电子设计:光耦设计那些事

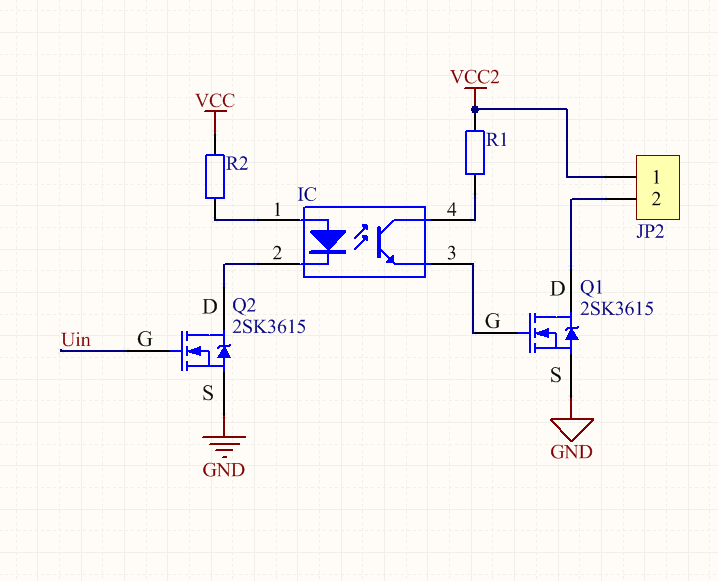

我们知道常用的隔离器件有继电器,拨码开关,以及光耦等等,光耦器件是一种以光-电-光传输的形式的信号隔离器件。它的优势就在于可以构成各种逻辑电路,由于光电耦合器的抗干扰性能好,由它构成的逻辑电路更可靠。 按输出结构分有三种:无基极引线光耦,有基极引线光耦,双三极管的达林顿光耦。

想要大概了解共射放大电路的原理是很简单的,几行数学推导就可以了。但是想要真正涉及好一个共射放大电路却并不是容易的事,我们用前面的几篇文章讨论了共射放大器的基础问题,有了这些基础概念,就可以真正的电路设计了。这里来总结下共射放大器的设计步骤。 1、电子设计要求: 以阻容耦合共射放大电路为例,对输入峰峰值为2V的1kHz正弦信号,负载100kohm,设计5倍放大电路。2、电子设计思路和步骤 第一步:首先,必须选定供电电压VCC 电路中,供电电压高则功耗大,在可能的情况下大家应该不断的减小供电电压以

电路设计防静电原理解析

一、静电放电波形和能量频谱 静电放电(ESD)理论研究的已经相当成熟,为了模拟分析静电事件,前辈电路设计了很多静电放电模型。 常见的静电模型有:人体模型(HBM),带电器件模型,场感应模型,场增强模型,机器模型和电容耦合模型等。芯片级一般用HBM做测试,而电子产品则用IEC 6 1000-4-2的放电模型做测试。为对 ESD 的测试进行统一规

一、输入失调电压(Offset Voltage,VOS) (一)定义:在运放开环使用时, 加载在两个输入端之间的直流电压使得放大器直流输出电压为 0。 (二)优劣范围:1µV 以下,属于极优秀的。100µV 以下的属于较好的。最大的有几十mV。 (三)对策: 1)选择 VOS远小于被测直流量的放大器, 2)过运放的调零措施消除这个影响 3)如果你仅关心被测信号中的交变成分,你可以在输入端和输出端增加交流耦合电路,将其消除。 4)如果 IB1=IB2,那么选择 R1=R2//RF,可

一、输入失调电压(Offset Voltage,VOS) (一)定义:在运放开环使用时, 加载在两个输入端之间的直流电压使得放大器直流输出电压为 0。 (二)优劣范围:1µV 以下,属于极优秀的。100µV 以下的属于较好的。最大的有几十mV。 (三)对策: 1)选择 VOS远小于被测直流量的放大器, 2)过运放的调零措施消除这个影响 3)如果你仅关心被测信号中的交变成分,你可以在输入端和输出端增加交流耦合电路,将其消除。 4)如果 IB1=IB2,那么选择 R1=R2//RF,可

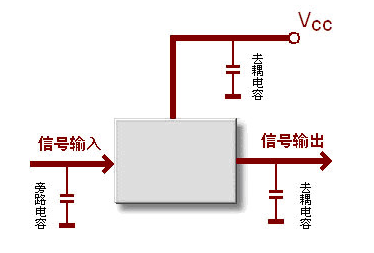

旁路电容与去耦电容的区别

可将混有高频电流和低频电流的交流电中的高频成分旁路滤掉的电容,称做“旁路电容”。 对于同一个电路来说,旁路(bypass)电容是把输入信号中的高频噪声作为滤除对象,把前级携带的高频杂波滤除。 去耦电容是电路中装设在元件的电源端的电容,此电容可以提供较稳定的电源,同时也可以降低元件耦合到电源端的噪声,间接可以减少其他元件受此元件噪声的影响。 去耦和旁路都可以看作滤波。去耦电容相当于电池,避免由于电流的突变而使电压下降,相当于滤纹

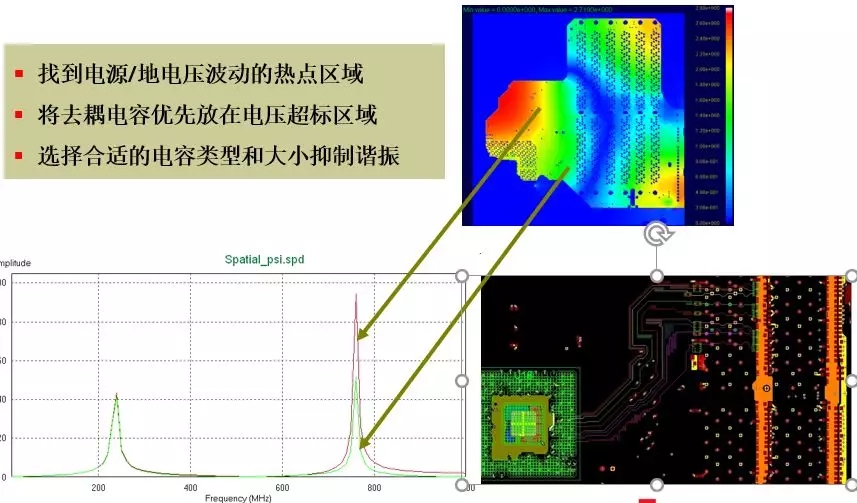

Sigrity PowerSI是IC封装和PCB设计快速准确的全波电磁场分析,作为专业的频域分析工具,为当前高速电路设计中面临的各种信号完整性(SI)、电源完整性(PI)和电磁兼容(EMI/EMC)分析提供快速准确的全波电磁场分析,并提供宽带 S参数提取以及频域仿真。PowerSI可以为IC封装和PCB设计提供快速准确的全波电磁场分析,从而解决高速电路设计中日益突出的各种PI和SI问题:如同步切换噪声(SSN)问题,电磁耦合问题,信号回流路径不连续问题,电源谐振问题,去耦电容放置不当问题以及电压

扫码关注

扫码关注