- 全部

- 默认排序

很多人学习FPGA后,接下来进入进阶提升技术环节,一个专业优秀的FPGA工程师,需要学习哪些知识,如何提升这方面的能力?上篇我们讲述了入门FPGA的学习路线,这篇文将讲述进阶FPGA的路线学习,希望对小伙伴有所帮助。进阶学习FPGA主要分为

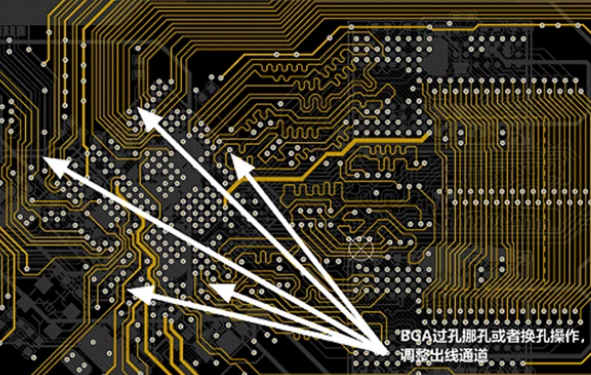

前言现在很多的PCB Layout工程师都是按照硬件工程师或者PI SI工程师给出的约束规则来完成布局布线的,俗称的“拉线工”。如不想被当做“拉线工”来看待。要具备一定的电路理解能与SI/PI工程师做PI/SI分析的能力。PCB Layou

干式绝缘结构是互感器诞生时的原型方式,其制造工艺简单、本钱较低,但因为其绝缘条件的约束,不能接受很高的电压,一般常用于380V及以下的场合。干式绝缘结构一般运用的绝缘资料有绝缘纸、玻璃丝布带和酚醛塑料等。二次绕组用QZ型漆包线,绕在酚醛纸筒

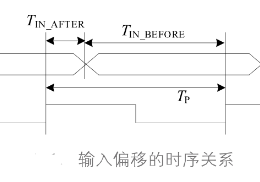

FPGA的时序分析及时序约束一直以来是小白难以搞懂的知识点,经常劝退不少小白,尤其是其中的偏移约束,所以本文将重点谈谈偏移约束。偏移约束属于基本时序约束,规定了外部时钟和数据输入输出引脚之间的相对时序关系,智能用于端口信号,不能应用于内部信

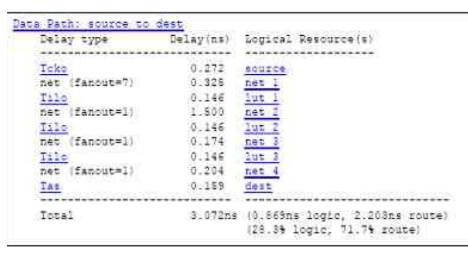

时序性能是FPGA设计最重要的技术指标之一,在项目设计中很多人经常会遇见时序性能差的现象,但不知道该如何解决。造成时序性能差的根本原因有很多1、布局太差如图所示:该图是布局太差的时序报告示意图,其中附加的周围约束为3nm,实际周期为3.02

在FPGA设计时,我们总会遇到各种各样的设计难题,并发愁如何解决,所以小编将搜集网络上九个小白最头疼的FPGA设计问题,并进行回答,希望对小白有所帮助。1、如何控制XST插入buffer?①用buffer_type约束,具体使用方法在XST

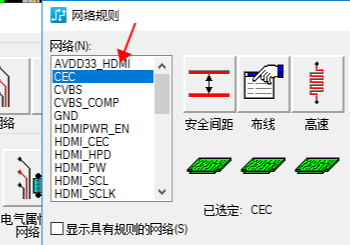

PADS网络规则设置

若需要对某一特定网络进行设置约束规则,可在网络规则中设置。单击“网络”图标,弹出“网络规则”对话框,如图5-89所示,在“网络”的列表中选择我们需要设置网络规则的信号,比如“CEC”,再单击“安全间距”或“布线”,对此网络进行单独约束规则设

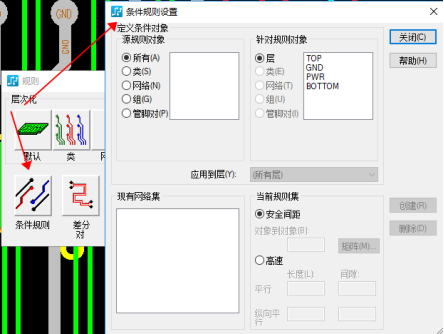

PADS条件规则设置

设计多层板时,需要对不同层设置不同线宽、间距规则,对特定网络或者类在不同层设置约束规则进行区分,此时可在条件规则内进行设置。1)点击“条件规则”图标之后,弹出其对应的对话框,如图5-90所示。图 5-90 “条件规则设置”对话框2)可在“源

边缘计算和云计算之间的区别处理和数据存储发生在云端边缘系统上。但网络限制可能是区分边缘和云的最好方法。在核心,边缘计算和云计算之间的主要区别归结为一个概念:网络连接约束。如果互联网连接能在任何地方持续可用,并且数据可以立即传输而没有任何延迟

同步电路是常见的电子电路之一,也是电子人才最头痛的电路学习难点之一,很多人在面对同步电路的时序约束和附加约束等等内容都会感到头疼,所以今天为帮助小伙伴们更好地理解,今天将换种方式聊聊同步电路的时序约束和附加约束?1、时序约束时序约束主要包括

扫码关注

扫码关注