- 全部

- 默认排序

半导体先进封装是一种将多个芯片组件集成在一起的技术,旨在提高芯片的性能、集成度和效率,它涉及将生产加工后的晶圆进行切割、焊线、塑封等步骤,使电路与外部器件实现连接,并为半导体产品提供机械保护,免受物理、化学等环境因素损失。封装技术可分为传统

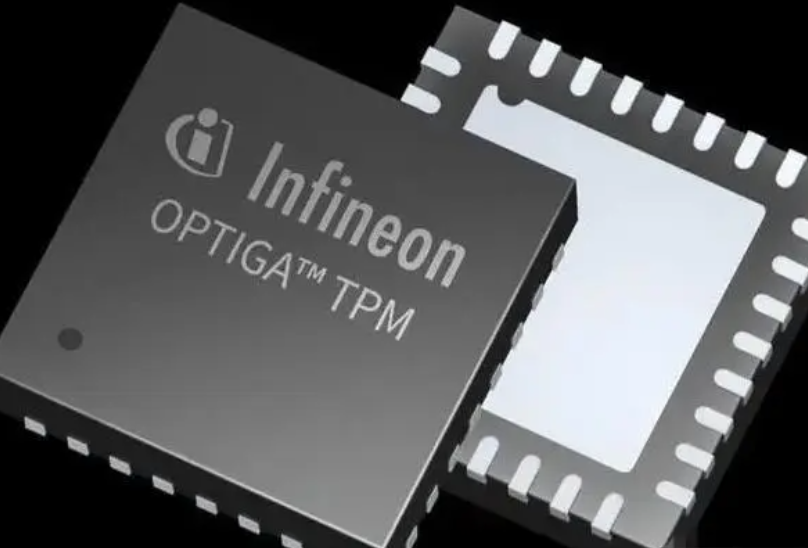

什么是IC测试?任何一块集成电路都是为完成一定的电特性功能而设计的单片模块,IC测试就是集成电路的测试,就是运用各种方法,检测那些在制造过程中由于物理缺陷而引起的不符合要求的样品。从而确保产品良率和成本控制的重要环节,在IC生产过程中起着举

在印刷电路板(PCB)设计中,信号传输速度是一个极为关键的参数,直接影响电路的性能,而介电常数作为材料的一种固有属性,与信号传输速度有紧密联系,本文将简要阐述这两者之间的关系。1、介电常数定义介电常数是衡量材料在电场作用下极化程度的物理量,

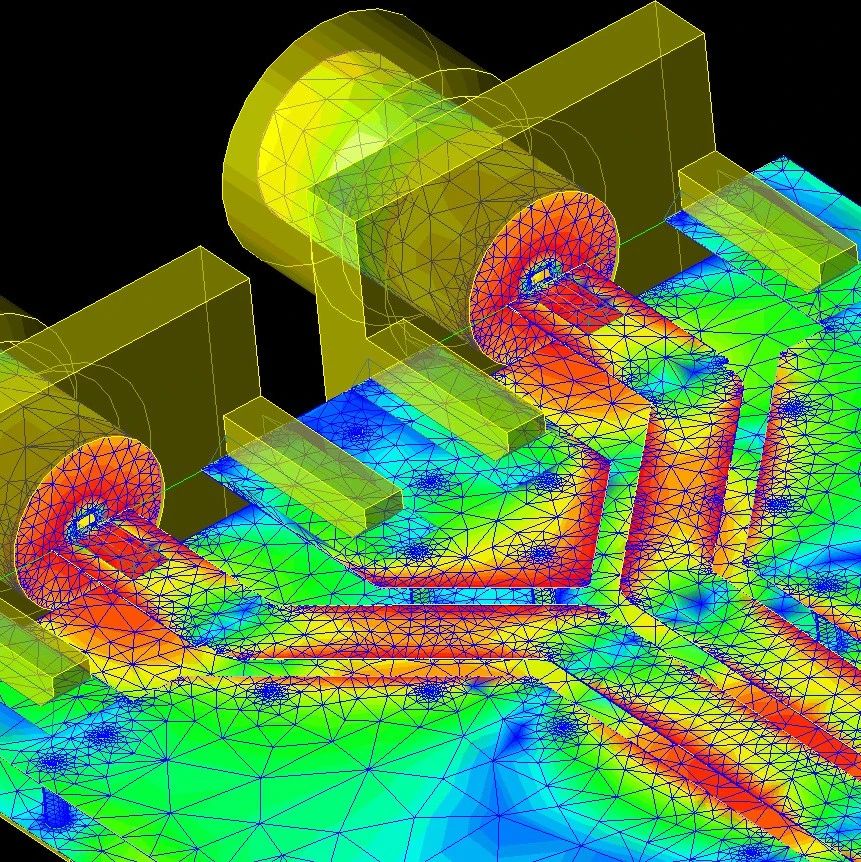

Keysight PathWave EMPro 是一个三维建模与仿真环境,可用于分析高速和射频/微波元器件的三维电磁效应。EMPro 可以与 ADS 进行联合仿真,在制作物理原型之前,通过电磁(EM)仿真进行深入分析, 利用电路仿真实施综合电磁分析。运行电磁仿真可能需要几个小时的时间。通过将电磁仿真

简介在快速发展的半导体技术领域,Bunch of Wires(BoW)协议因其能够促进高效的芯片到芯片(D2D)并行接口而脱颖而出。本文探讨 BoW 的最新进展和未来方向,重点是其在光学、内存和物联网接口中的应用。BoW 主要功能BoW 的开放式物理层和链路层规范旨在支持高性能 D2D 接口。关键性

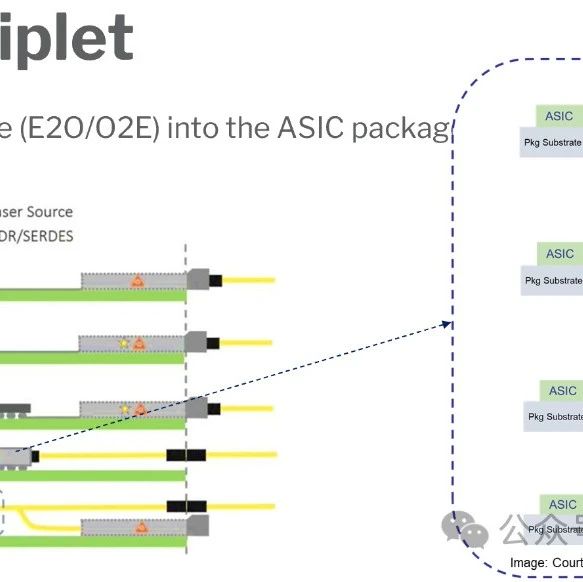

简介过去六十年里,摩尔定律面临过多次挑战,但半导体工程师总能找到突破,让芯片上的晶体管密度继续翻倍。然而,这背后的成本却在飙升。历来,缩小晶体管尺寸有助于提高芯片的运行速度。目前,制造商已能在硅芯片上形成仅有几个原子厚的微结构。但鉴于物理的极限,这些微结构无法无限缩小,虽然降温或降低电压等方法也能提

电子元器件的检验和筛选是确保其质量和性能的重要过程。以下是一些常见的检验和筛选步骤:1. 外观检查封装和引脚:检查封装是否有破损、划痕或其他物理损伤,引脚是否有氧化、弯曲或损坏。标识和文字:核对元器件上的标识和文字是否清晰,是否与规格书中的

作为组成芯片的基本元件,晶体管的尺寸和数量多少将决定着芯片的性能大小,为了尽可能达到芯片,晶体管早已接近物理极限,其中发挥着绝缘作用的栅介质材料十分关键。据媒体报道,中国科学院上海微系统与信息技术研究所的研究员狄增峰所带领的团队,成功开发出

使用虚拟机运行Linux操作系统通常会比在物理机上直接安装系统的运行效率更低,本篇博文将介绍如何优化虚拟机的设置,进而提升虚拟机性能体验。第1步:选择VMware菜单:编辑–>首选项–>更新,将”启动时检查产品更新“和”根据需要检查软件组件“两项取消勾选。第2步:选择VMware菜单:编辑–>首选项

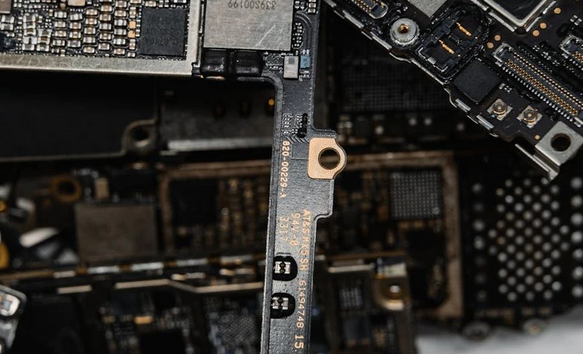

检测IC芯片的好坏是确保电子产品功能正常的重要步骤。以下是常见的IC芯片检测方法及注意事项:1. 检测方法a. 视觉检查· 描述:通过显微镜或放大镜检查芯片的外观,寻找物理损伤、焊接缺陷或污染。· 注意事项:检查引脚是否弯曲、缺失或有氧化现

扫码关注

扫码关注