- 全部

- 默认排序

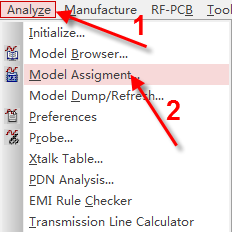

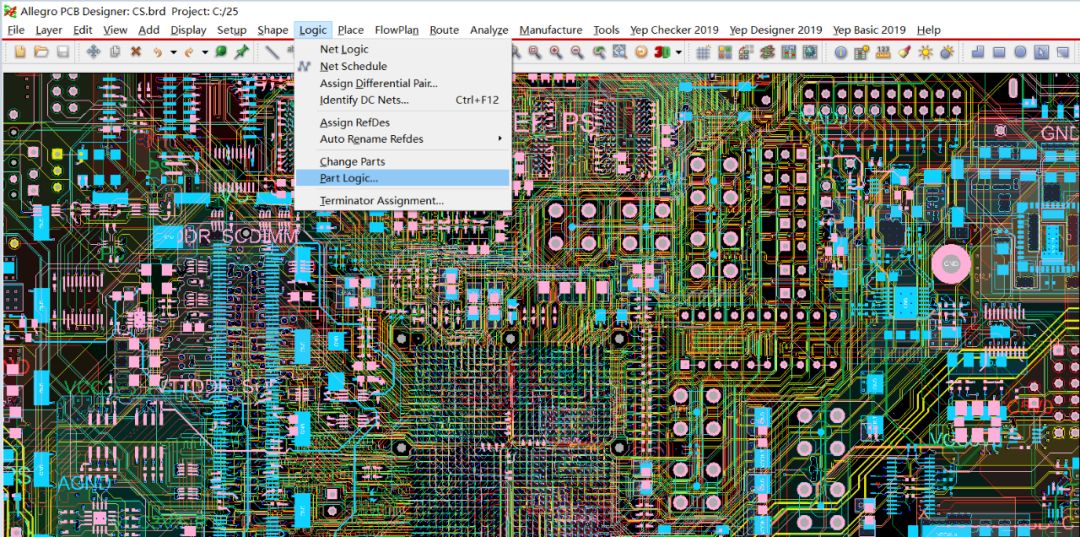

所谓的Xnet,是指在无源器件的两端,两个不同的网络,但是本质上其实是同一个网络的这种情况。比如一个源端串联电阻或者串容两端的网络。在实际设计情况中,我们需要对这种进行Xnet的设置,方便进行时序等长的设计,一般信号传输要求都是信号的传输总长度达到要求,而不是分段信号等长,这时采用Xnet就可以非常方便的实现这一功能,在Allegro软件中添加xnet的具体步骤如下所示:第一步,执行菜单命令Analyze-Model Assigment,进行模型的指定,如图5-112所示; 图5-11

一般不规则的焊盘被称为异型焊盘,典型的有金手指、大型的器件焊盘或者板子上需要添加特殊形状的铜箔(可以制作一个特殊封装代替)。如图27所示,此处我们以一个锅仔片为例进行说明。

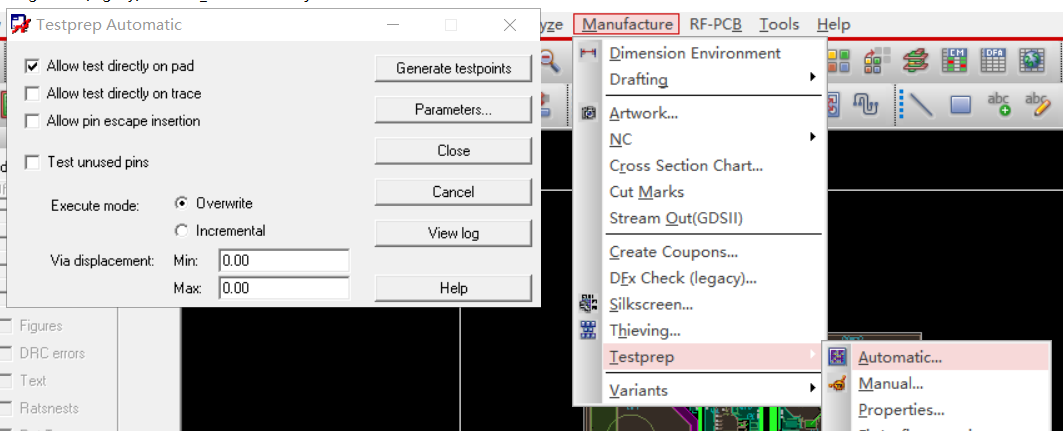

cadence allegro Allow test directly on pad:允许测试点在焊盘上,允许时将自动替换已有的过孔。Allow test directly on trace:允许测试点在信号线上,允许时测试点可以直接在信号线上。Allow pin escape insertion:允许从引脚上自动引出测试点。Test unused pins:无网络引脚添加测试点。

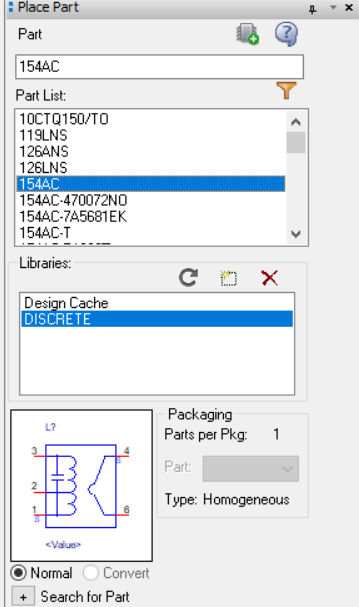

orcad绘制原理图时怎么放置器件?orcad在绘制原理图时,需要从库中把元器件放置到原理图中,放置的方法如下:第一步,执行菜单Place→Part,或者按快捷键P、或者点击右侧菜单栏放置元器件的图标,来调出放置元器件的窗口,如图3-9所示; 图3-9 放置元器件窗口示意图第二步,在放置元器件之前,需要在下面的库路径下指定封装库的路径,如图3-10所示,点击Add Library命令添加库路径; 图3-10 添加库路径示意图第三步,在库路径下选中改元器

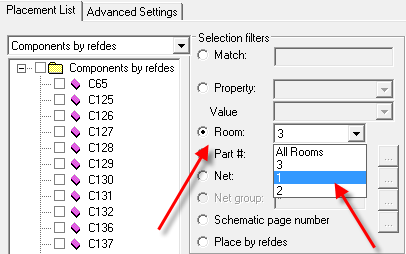

上述我们讲解了怎么快速的将元器件放置在PCB板上,通过图6-40所示的图可以看出,器件放置的都是很零散的,不是按模块或者是按页放置的,这里给大家介绍一些,通过在原理图添加ROOM属性,然后通过ROOM框在PCB板上来放置元器件,这样就可以根据模块或者一页原理图去发放置元器件了,具体操作如下:第一步,需要对原理图中的元器件添加ROOM属性,这个在前面的问答中已经讲述过了,这里不再做赘述,然后导入网表到PCB中;第二步,在PCB中绘制ROOM框,执行菜单命令Setup-Outlines-ROOM O

Allegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产(目前高速PCB设计用的最多工具,就是Allegro)。

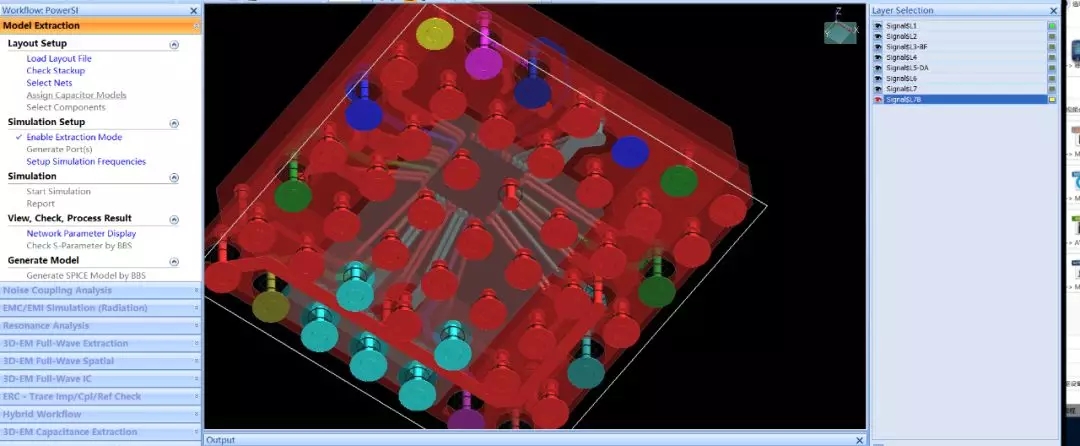

在IC封装的分析中,为了能够提取到更加趋近于真实测量结果的参数S参数(或者其他参数),需要在封装体上添加假性球体和参考层,下面来讲解添加假性球体和参考层的方法。

扫码关注

扫码关注