- 全部

- 默认排序

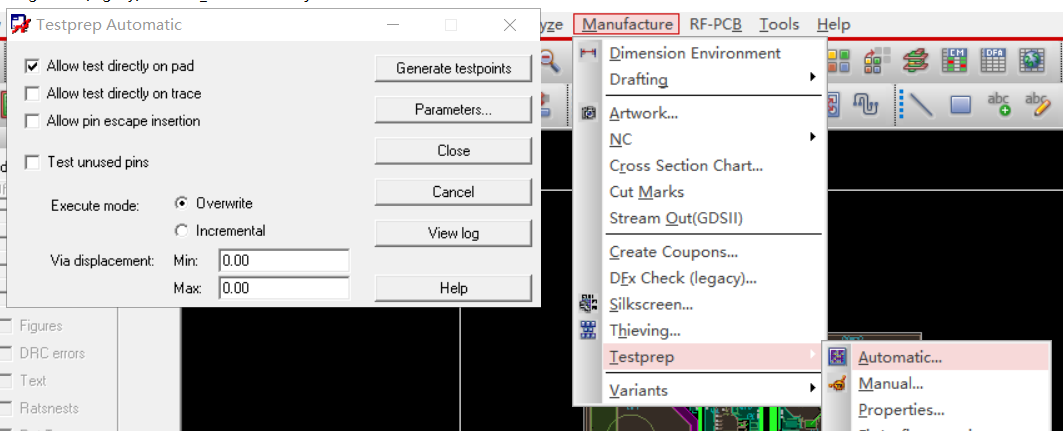

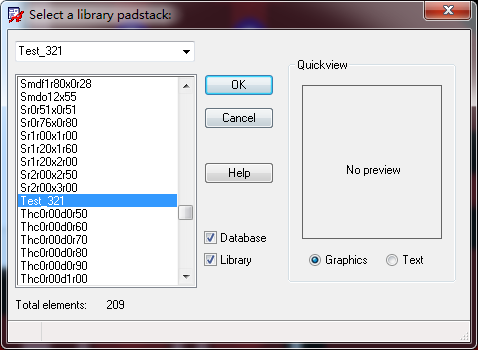

cadence allegro Allow test directly on pad:允许测试点在焊盘上,允许时将自动替换已有的过孔。Allow test directly on trace:允许测试点在信号线上,允许时测试点可以直接在信号线上。Allow pin escape insertion:允许从引脚上自动引出测试点。Test unused pins:无网络引脚添加测试点。

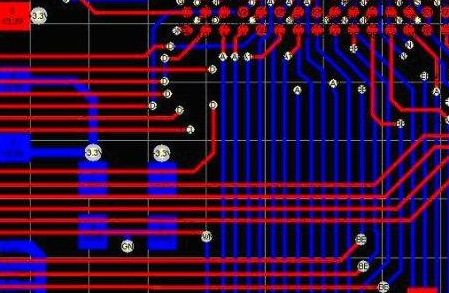

答:1)需要塞孔的过孔在正反面都不做阻焊开窗;2)需要过波峰焊的PCB板卡,BGA下面的过孔都需要做塞孔处理、不开窗;3)BGA器件的pintch间距≤1.0mm,BGA下面的过孔都需要做塞孔处理、不开窗;4)BGA器件加的ICT测试点,测试焊盘直径32mil,阻焊开窗37mil。

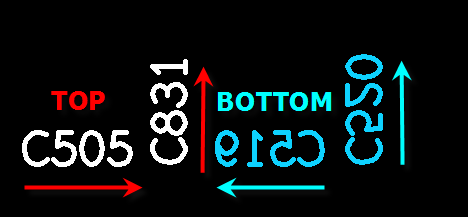

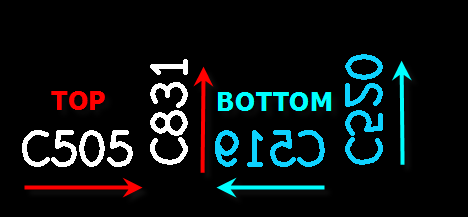

答:一般情况下,我们推荐位号字符在与阻焊不干涉的情况下,推荐位号字符与SMD焊盘、插装焊接孔、测试点、Mark点至少保证6mil的间距,位号字符之间部分重合是可以的,任何位号字符由于重叠导致的无法辨认必须进行调整。位号字符的方向设定,一般推荐在正视的情况下,位号字符的排列是从左到右,从上到下的,如图1-30所示,TOP面与Bottom面的位号字符排列。 图1-30 TOP面与Bottom面的位号字符排列示意图

答:ICT,In Circuit Tester,自动在线测试仪,是印制电路板生产中重要的测试设备,用于焊接后快速测试元器件的焊接质量,迅速定位到焊接不良的引脚,以便及时进行补焊。在PCB设计中,就需要在设计中添加用于ICT测试的焊盘。ICT测试可以检测的内容有:线路的开短路、线路不良、元器件的缺件、错件、元器件的缺陷、焊接不良等,并能够并能够明确指出缺点的所在位置。一般来说,ICT常用的设计要求如下所示:Ø ICT测试点焊盘大小直径为40mil,最小不小于32m

答:DC-DC电路,指的是直流/直流转换电路,主要的目的就是为了电压的变换,通过开关变换的方式将直流变换成直流的电路,就被称为DC-DC电路。DC-DC电路必须有调整管,调整管工作于开关状态或者是线性放大状态就决定了其工作方式。DC-DC电路的应用领域很广泛,应用于数字电路、电子通信设备、卫星导航、遥感遥测、地面雷达、消防设备和医疗器械教学设备等诸多领域。DC-DC电路的优点有很多,如:功耗小、效率高、体积小、重量轻、可靠性高、自身抗干扰性强、输出电压范围宽、模块化功能强等等。DC-DC电路可以

答:ICT (In Circuit Tester,自动在线测试仪)是印制电路板生产中重要的测试设备:用于焊接后快速测试元器件的焊接质量,能迅速定位焊接不良的引脚,以便及时进行补焊。体现在PCB设计上,则需要在设计中添加用于ICT测试的焊盘,并对符合测试点要求的焊盘添加测试点属性。因测试点焊盘和间距及位置有严格的要求,对于有ICT设计要求的板卡,建议在设计前就明确添加ICT的网络,拟定ICT的添加计划,在设计的过程中边布线边添加。如果在设计完后再添加ICT测试点,必将大量返工,甚至有的网络根本无法

答:一般情况下,我们推荐位号字符在与阻焊不干涉的情况下,推荐位号字符与SMD焊盘、插装焊接孔、测试点、Mark点至少保证6mil的间距,位号字符之间部分重合是可以的,任何位号字符由于重叠导致的无法辨认必须进行调整。

答:ICT,In Circuit Tester,自动在线测试仪,是印制电路板生产中重要的测试设备,用于焊接后快速测试元器件的焊接质量,迅速定位到焊接不良的引脚,以便及时进行补焊。

扫码关注

扫码关注