- 全部

- 默认排序

答:串扰,就是指一条线上的能量耦合到其他传输线,它是由不同结构引起的电磁场在同一区域里的相互作用而产生的。串扰在数字电路中非常普遍地存在着,如芯片内部、PCB板、接插件、芯片封装,以及通信电缆等等。 串扰可能是数据进行高速传输中最重要的一个影响因素了。它是一个信号对另外一个信号耦合所产生的一种不受欢迎的能量值。根据麦克斯韦定律,只要有电流的存在,就会有磁场存在,磁场之间的干扰就是串扰的来源。这个感应信号可能会导致数据传输的丢失和传输错误。 所以串扰对

致公司全体员工:根据国家法定假期的规定,并结合公司实际情况,现对春节放假安排如下:一、2021年春节放假调休日期为:2月9日(星期二)至2月18日(星期四)放假,共计十天。2月19日(星期五)上班。二、其中2月7日(星期日)、2月20日(星期六)上班,2月21日放假。 二、放假期间注意事项:请公司各职员做好自己的节前工作安排,并检查相关设施设备,做好防火防盗工作,确保办公场所的安全、有序。三、公司各职员应保持节假期间的通讯流畅,以便公司工作需要。四、希望全体员工在节假日外出期间,应注意

答:我们在创建多管脚的器件封装时,分Part的依据一般如下:查看改器件的Datasheet,根据芯片手册的分类来划分Part;把电源管脚与信号管脚分开;把功能一致的管脚分为一个Part;空管脚比较多的器件,把所有的空管脚分为一个Part。

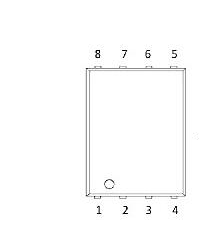

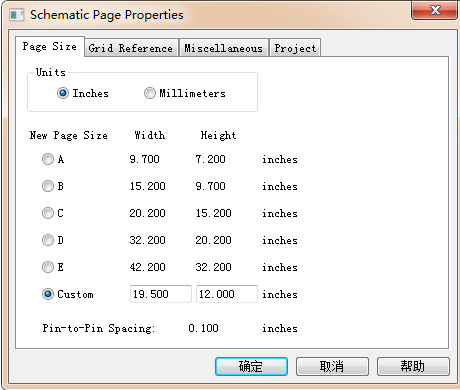

答:在绘制复杂的原理图时,会根据功能模块来将原理图进行分页处理,在绘制原理图过程中,会对原理图页面进行一些处理,如参数设置。拷贝等,操作方法如下所列:页面大小设置:选中原理图页面,点击右键,选择Schematic Page Properties属性设置,即可对页面大小进行设置了,如图3-31所示: 图3-31 页面大小设置示意图页面拷贝与粘贴:选中要拷贝的原理图,点击右键选择Copy,即对当前页面拷贝好,该页原理图的所有内容、属性全部包括在内;选中原理图的根目录,可以对拷贝

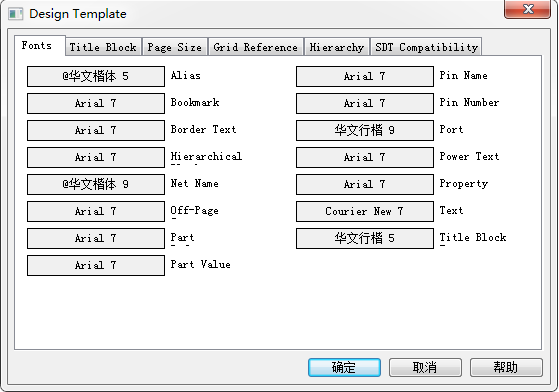

答:我们在运用Orcad进行原理图绘制时候,一般使用的都是默认的字体,用的最多的是就是网络标号的字体、位号的字体、封装属性的字体。当然使用默认字体是没有任何问题的,只是有时候我们将一些属性加以批示与标注,更加醒目这时就需要对其进行更改,一个一个去改费时费力,这里我们讲解下如何批量的去进行更改,具体操作的方法如下:第一步,首先打开原理图,对设计的模板进行更改,这样模板设定好了以后,原理图设计的内容都会根据模板来进行设定,执行菜单命令Options-Design Template,会弹出如图3-13

答:在使用Orcad软件进行原理图的过程中,会经常遇到这样的问题,原理图一共是绘制了很多页,但是在“Title Block”的显示栏中,原理图页面的显示总是1 of 1,每次都要手动去进行修改,非常的麻烦,有没有什么方法进行调整下,可以让这个原理图的页面可以自动根据原理图绘制的情况,自信进行增加呢?下面,我们就对这个问题进行一一的解析,详细如下所示:第一步,选中原理图的根目录,DSN文件,然后执行菜单命令Tools-Annotate,进行参数的设置;第二步,进入参数设置界面之后,需要选择两个参数

答:用Allegro软件里,每一个封装都有一个占地面积,一般是在Package Geometry-Place_Bound_top层画一个比器件实际尺寸大一些的Shape,这个Shape表示了单个器件在PCB上应该占用的空间大小,在做PCB设计时需要考虑不要将不同器件的占地面积堆叠重合在一起,如果放的过近,可能导致安装不方便、PCB维修有困难。一般放置占地面积是根据不同的器件类型放置不同尺寸大小,具体大小可参考以下尺寸。Chip元件, place_bound层器件最大外围尺寸(焊盘和丝印中取大值)

答:在将网表导入到PCB的过程中,常会由于带通孔的PCB封装内的焊盘中Flash在相应的路径中找不到,而导致导网表报错,报错内容及提示如图4-93所示: 图4-93 错误提示示意图根据图4-93所示,我们可以分析得出以下几个结论:Ø 导网表时报错的器封装名是CON2X5_2P54M。Ø PCB封装中焊盘名为PAD100SQR165THR的焊盘不能被完整提取到,原因是在设置的库路径下找不到名为THR100X165C150X180X040的Flash。对于此

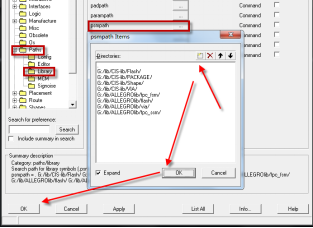

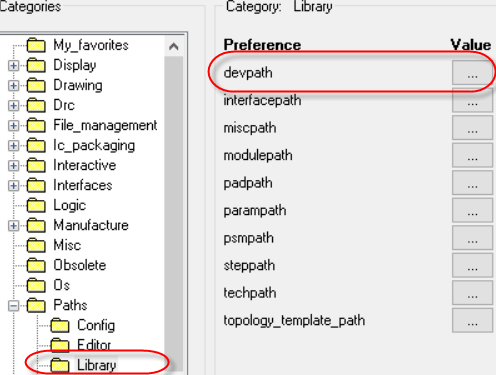

答:导网表时,常会用到第三方网表(用Other方式导出的网表)导入到PCB中,导入时常会发生找不到device的报错,具体报错内容可查看以下内容,如图4-97所示: 图4-97 错误提示示意图根据4-97所示,我们可以分析得出以下几个结论:Ø 导网表时,器件C1的封装报错。Ø 导网表时找不到封装名为SMD_0603的device文件。可以按照以下几个步骤来解决此问题:第一步,查看device路径是否设置正确。在命令Setup-UserPreference

答:根据器件规格书(Datasheet)制作封装时,一般做出来的封装焊盘管脚长度需要做适当的补偿,即适量地对器件原先的管脚加长一点,具体的补偿方法,是根据器件的管脚类型来补偿的,可按以下办法:第一类,无引脚延伸型SMD封装,如图4-100所示: 图4-100 无引脚延伸型SMD封装示意图A—零件实体长度 X—补偿后焊盘长度 H—零件脚可焊接高度

扫码关注

扫码关注