- 全部

- 默认排序

对刚开始学C语言的电子小白来说,实践是提升其技能的关键,然而不知道如何选择项目,是很多人共有的难题,所以本文将推荐20个C语言项目,适合小白入手实战。1、LED闪烁灯:编写程序控制LED灯的开关,实现简单的闪烁效果。2、数字时钟:使用C语言

晶振作为电子设备中的关键元件,其频率的选择直接关系到设备的性能和稳定性,工程师必须熟记不同电子产品的晶振频率选择,下面将列出一些常见的电子设备的晶振频率,希望对小伙伴们有所参考。1、主机主板32.768kHz:主要用于实时时钟(RTC)模块

接口篇—IIC协议

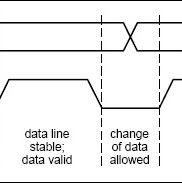

先聊聊IIC接口,今天只聊聊IIC协议,后续会将IIC接口测试、研发中会遇到的故障分析一一分享给大家,欢迎拍砖,更欢迎一起交流学习。1、I2C总线特征: 只要求两条总线线路:一条串行数据线SDA 一条串行时钟线SCL;每个连接到总线的器件都可以通过唯一的地址和一直存在的简单的主机/从机关系软

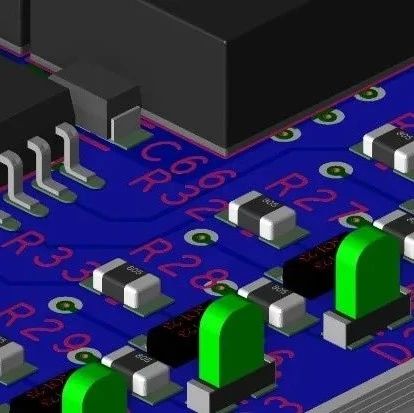

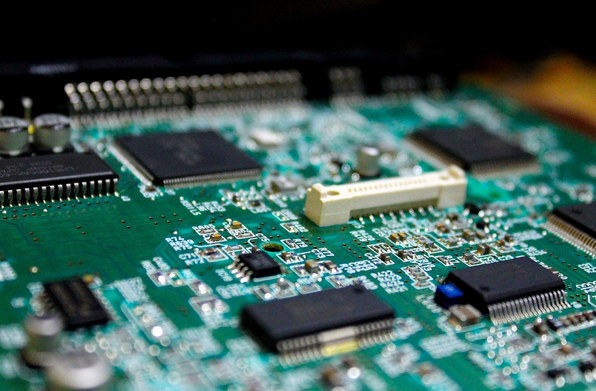

DDR布线技术的重要性在如今的印刷电路板设计中,双数据速率(DDR)存储器非常普遍。许多设计都会用到DDR存储器配置的不同版本,这需要在布局中使用特定的布线模式。DDR的名称来源于其能够在每个时钟周期内发送和接收两次信号,是原先的单数据速率(SDR)存储器速率的两倍。由于速率增加了一倍,必须在布设D

在PCB设计中,时钟信号是极为关键的敏感信号,若设置不当很容易干扰到系统稳定,电磁干扰更加严重。所以工程师必须慎重对待时钟信号,遵循其高频特性和对时序的严格要求,确保其布局布线顺利。1、减少过孔数量时钟线上应尽量减少过孔的使用,因为过孔会增

在嵌入式开发中,可能会接到关于微控制器(MCU)要求低功耗的项目需求,特别是在对电池寿命有严格要求的应用场景,如可穿戴设备、物联网传感器等,如果想要高效实现MCU的低功耗需求,该如何做?1、关闭非必要外设时钟逐一检查MCU的外设,仅保留工作

在PCB设计中,电子工程师需要遵循一系列设计原则,以此确保电路性能、稳定性和可靠性,但有太多原则是工程师无法理解,所以我们谈谈那些不为人知的原则,分析其原因。1. 时钟线包地原则原则:时钟线两侧建议包地线,包地线每隔3000mil打接地过孔

在高速串行通信系统中,随着数据传输速率的不断提升,传统的并行通信方式受限于信号同步与感染问题,逐渐难以满足现代高速数据传输的需求,因此,时钟数据恢复技术应运而生,成为实现高速、稳定串行通信的关键技术之一。1、时钟数据恢复是什么?时钟数据恢复

在IC芯片进入流片阶段前,工程师必须做好大量准备,确保后续环节的顺利进行,而合理的布局设计是确保芯片性能、可靠性和成本效益的关键。1、Pin布局优化明确pin的引出方向和位置,特别是将时钟pin与模拟信号pin保持适当距离,以减少信号干扰。

作为嵌入式系统的代表,51单片机应用广泛,其正常运作依赖稳定而精确的时钟信号,要想信号稳定,就离不开时钟振荡电路,它决定了单片机的执行速度及同步操作的时序。51单片机的时钟振荡电路可分为内部和外部时钟振荡方式,以此满足不同需求。1、内部振荡

扫码关注

扫码关注