- 全部

- 默认排序

晶振,作为电子设备的核心时钟源,其频率稳定性是很多电子工程师设计时需要考虑的重要原因之一,若是处理不当,晶振频率发生漂移,导致设备无法正常运行,还带来一系列问题,所以今天来讲讲晶振频率漂移,希望对小伙伴们有所帮助。1、系统稳定性下降晶振的频

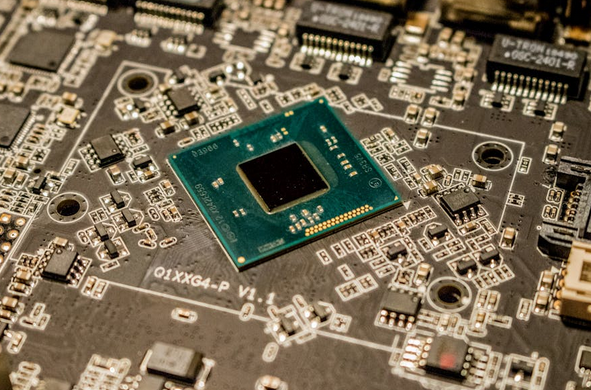

在嵌入式系统设计中,晶振作为系统的心脏,其频率的选择直接关系到系统时钟的准确性和稳定性,进而影响外设如串口通信的性能。特别是在高精度高频率场景,因此本文将谈谈晶振频率的选择问题。1、晶振频率选择的直接影响①波特率精准度不同的晶振频率在计算得

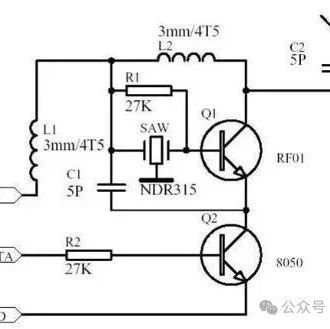

315M发射电路原理静态时,12V通过L1、R1、Q1的B-E向Q2的C极提供电压,当DATA来数据时,使Q2导通,这时Q1的E极旧处在0电位,原静态时Q1是截止的。当Q1的E极处0电位,Q1管导通,使得C极信号为B极的晶振频率。当DATA的信号不是一直处在高电平时,Q2就处在通断状态,就是说DAT

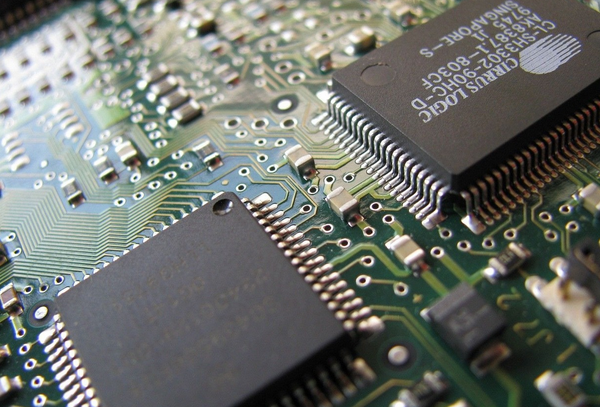

晶振作为电子设备中的关键元件,其频率的选择直接关系到设备的性能和稳定性,工程师必须熟记不同电子产品的晶振频率选择,下面将列出一些常见的电子设备的晶振频率,希望对小伙伴们有所参考。1、主机主板32.768kHz:主要用于实时时钟(RTC)模块

全站最新内容推荐

- 1加码技术,打破困境,PSPice电路仿真助你解锁职场新高度!

- 2简谈稳压二极管和普通二极管的区别

- 3贴片元件如何拆卸及焊接?

- 4盘点电子工程师必须了解的21个电路

- 5英伟达GB300芯片受阻,存在过热问题

- 6WARELEO李增原创H04课程大纲的安排课程中内容及工具及课程的重点学习办法的讲解

- 7WARELEO李增原创H03根据自己的关注知识点和所需要的知识来选择需要的图书包邮递

- 8WARELEO李增原创H02理工男生李老师的介绍从51单片机驱动到FPGA到仿真设计之路

- 9WARELEO李增原创H01信号电源完整性设计与HFSS射频天线设计仿真验证研修课程主题

- 10WARELEO李增:反射仿真的信号观察办法及时域串扰的仿真设置及观察技巧

扫码关注

扫码关注