- 全部

- 默认排序

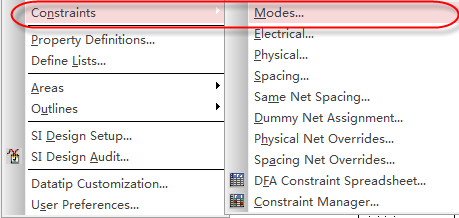

答:我们在设计完成以后,都需要对一组传输的总线进行时序等长,在做时序等长的时候,分为绝对传输延迟与相对传输延迟。绝对传输延迟,顾名思义,信号传输在PCB设计中都是有一个走线的长度,我们通过设置这个信号线传输的最大值与最小值,来实现等长的方法,就称之为绝对传输延迟。一般情况下如果信号是从一个点传输到另一个点,中间没有任何的串阻、串容,这个绝对传输延迟的方法还是非常有效而却直观的。具体在PCB中设置绝对传输延迟的方法如下所示:

答:所谓的Xnet,是指在无源器件的两端,两个不同的网络,但是本质上其实是同一个网络的这种情况。比如一个源端串联电阻或者串容两端的网络。在实际设计情况中,我们需要对这种进行Xnet的设置,方便进行时序等长的设计,一般信号传输要求都是信号的传输总长度达到要求,而不是分段信号等长,这时采用Xnet就可以非常方便的实现这一功能,在Allegro软件中添加xnet的具体步骤如下所示:

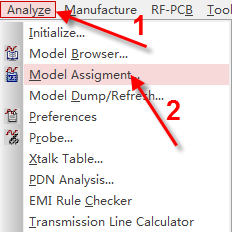

答:我们在时序等长时,除了考虑信号线的走线的长度以外,在高速设计领域里还需要考虑封装本身的引脚长度。所谓封装引脚长度,指的就是元器件封装内部的引脚长度,这个长度一般芯片的厂家会提供这数据,我们要做的就是将数据导入到规则管理器中,与等长一起处理,具体的操作步骤如下:

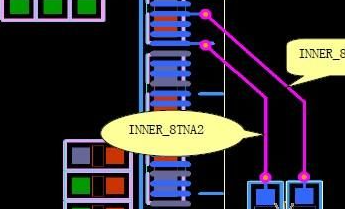

答:我们对于高速信号传输,比如差分信号、一组总线传输,都需要对其进行时序等长处理,在16.6版本以上,Allegro软件推出了自动等长的功能,在空间足够的情况下,是可以采用自动等长的功能,省去手动绕等长的时间,具体操作步骤如下所示:

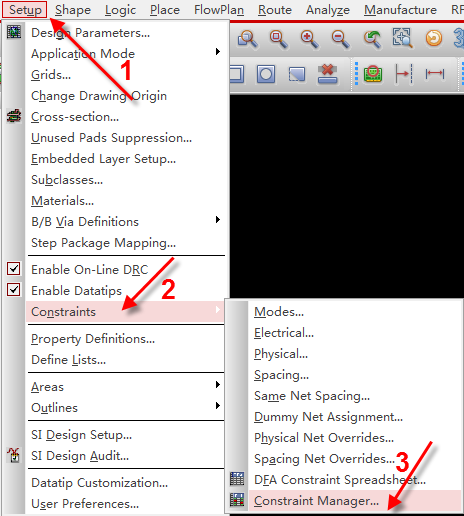

答:PCB设计中有一些信号组需要进行等长处理,以保证组内信号时序要求。第一步,点击Setup-Constraints-Constraint Manager选项,调出规则管理器,如图6-269所示;

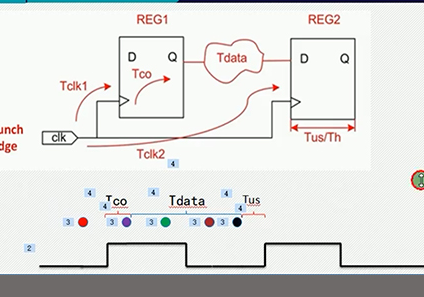

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。

在高速PCB设计中,差分信号(DIFferential Signal)的应用越来越广泛,电路中最关键的信号往往都要采用差分结构设计。为什么这样呢?和普通的单端信号走线相比,差分信号有抗干扰能力强、能有效抑制EMI、时序定位精确的优势。差分信

在高速PCB设计中,差分信号(Differential Signal)的应用越来越广泛,电路中最关键的信号往往都要采用差分结构设计。为什么这样呢?和普通的单端信号走线相比,差分信号有抗干扰能力强、能有效抑制EMI、时序定位精确的优势。布线要

众所周知,芯片行业存在一个定理,那就是摩尔定律,主要内容是集成电路上可容纳的晶体管数目在大约每18个月便会增加一倍。掌握FPGA/IC工程师需要的核心技能,来凡亿教育!>>《基于VIVADO平台的FPGA时序约束教程》随着技术的提升和原材料

很多人学习FPGA后,接下来进入进阶提升技术环节,一个专业优秀的FPGA工程师,需要学习哪些知识,如何提升这方面的能力?上篇我们讲述了入门FPGA的学习路线,这篇文将讲述进阶FPGA的路线学习,希望对小伙伴有所帮助。进阶学习FPGA主要分为

扫码关注

扫码关注