- 全部

- 默认排序

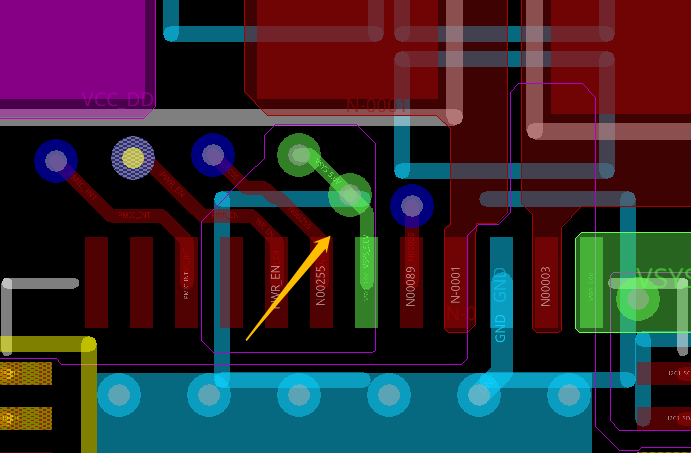

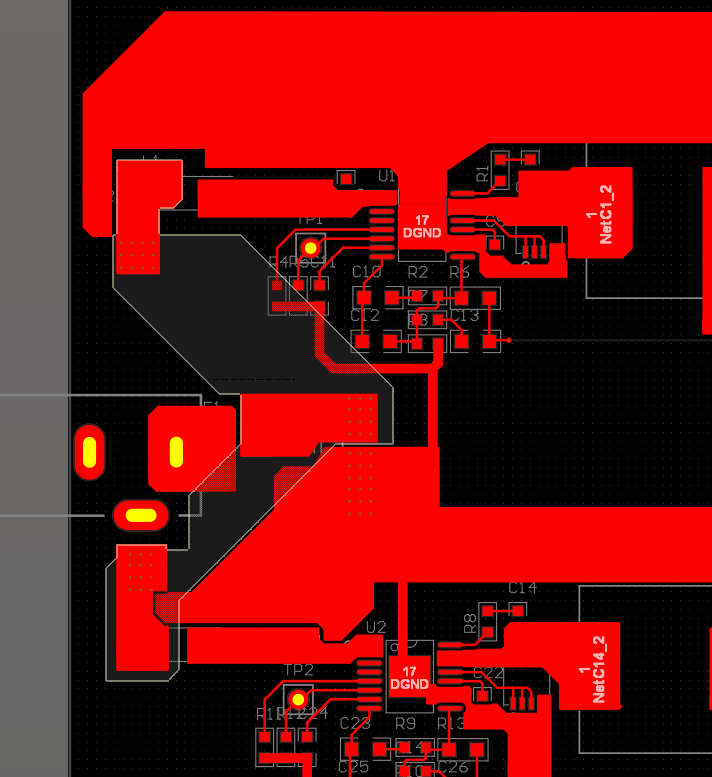

此处DCDC5.0V线宽满足不了载流:电感内部放置铜皮挖空区域,进行内部挖空:注意LDO电源的器件尽量整体中心对齐下:扇孔注意下对齐:看下此处的VCC-IO线宽是否能满足载流:器件注意对齐:以上评审报告来源于凡亿教育90天高速PCB特训班作

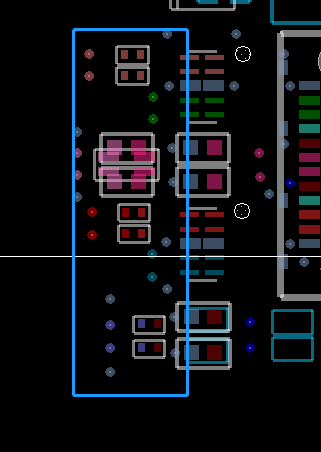

注意器件尽量整体中心对齐:上述一致问题,器件整体对齐处理:注意差分打孔换层的回流地过孔,打在正左右两侧,调整下:注意差分从过孔拉出,前两组调整为第三组的模式:此处电源信号并未连接:注意差分对内等长误差为5MIL:其他的没什么问题。以上评审报

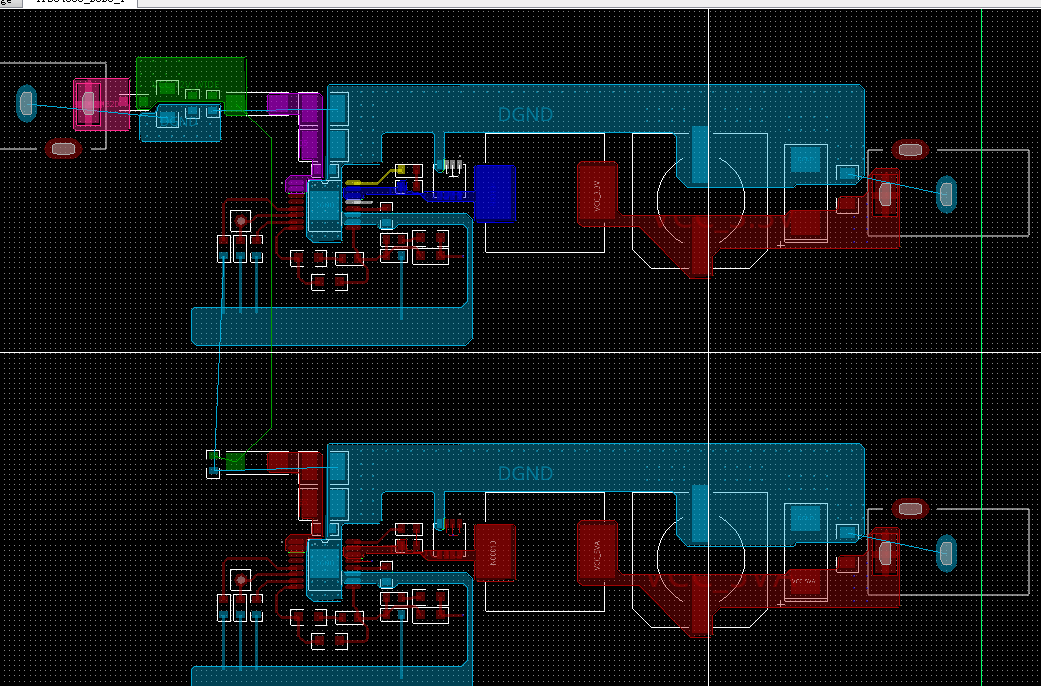

电源跟地都没有处理,还存在飞线,一定需要处理:配置电阻电容可以向上或者向下移动,中间布局优先于电源主干道,重新优化下布局:并且配置电阻电容尽量整体对齐以及紧凑,不要太松散了:一路跟二路的输入电源都没有铺铜连接:输出主干道的铜皮太窄,完全满足

DC/DC模块电源以其体积小巧、性能卓异、使用方便的显著特点,在通信、网络、工控、铁路、军事等领域日益得到广泛的应用。很多系统设计人员已经意识到:正确合理地选用DC/DC模块电源,可以省却电源设计、调试方面的麻烦,将主要精力集中在自己专业的领域,这样不仅可以提高整体系统的可靠性和设计水平,而且更重要

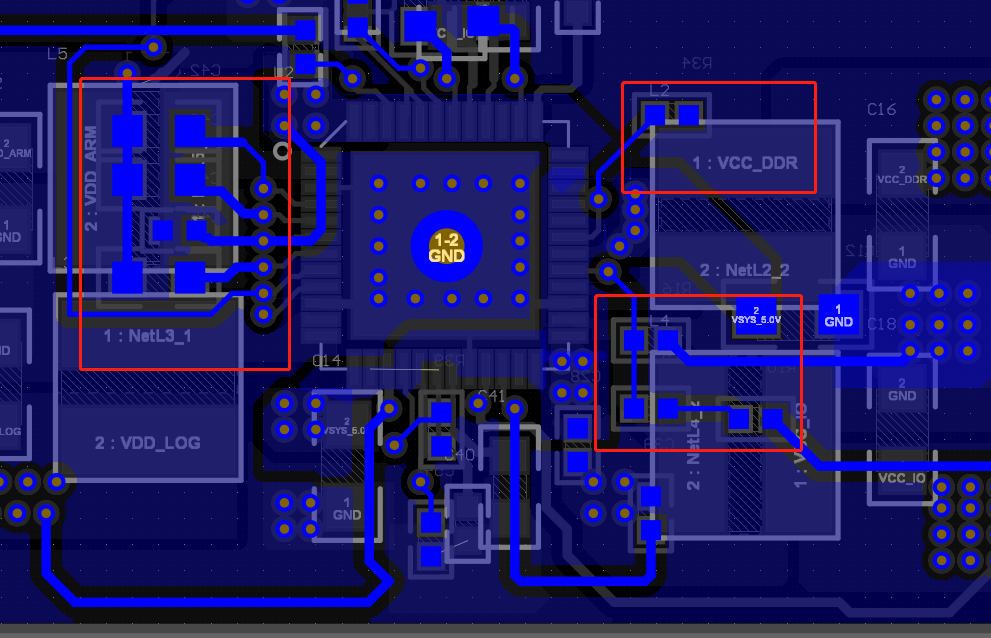

个别器件注意整体对齐:注意等长线之间需要满足3W间距原则:没满足的都自己优化下。数据线组内也需要满足3W:差分对内等长误差为5MIL:其他的没什么问题。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问

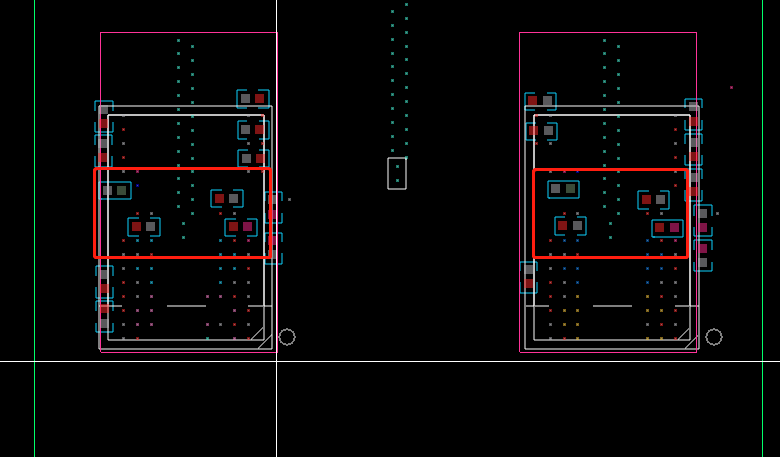

1、模块整体布局时,WIFI模组要尽量远离DDR、HDMI、USB、LCD电路以及喇叭等易干扰模块或连接座;2、晶体电路布局需要优先考虑,布局时应与芯片在同一层并尽量靠近放置以避免打过孔,晶体走线尽可能的短,远离干扰源,尽量天线区域;晶体以

想要做好PCB设计,除了整体的布线布局外,线宽线距的规则也非常重要,因为线宽线距决定着电路板的性能和稳定性。所以本篇以RK3588为例,详细为大家介绍一下PCB线宽线距的通用设计规则。要注意的是,布线之前须把软件默认设置选项设置好,并打开D

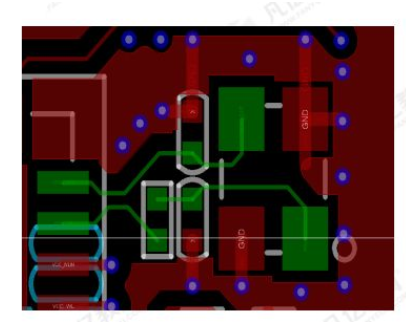

看下此处的扇孔可以再拉出去一点,留出铜皮的宽度出来,满足载流大小:电感内部需要挖空处理:其他的都一样,没处理的自己处理下:器件布局尽量整体中心对齐:并且需要整体中心对齐以及紧凑,不要太松散:走线没有完全连接完,需要中心跟中心连接好:焊盘内走

铜皮全部是直角,尽量全部都修改为钝角的:主干道器件摆放需要整体中心对齐:电感当前层内部需要挖空:焊盘出线需要从两长边拉出:电源输入输出对应的地在中间的IC焊盘上打孔过孔,进行单点接地:地直接优化下铺铜连接进来:其他的没什么问题了。以上评审报

电感底部不能放置器件,以及走线,自己优化吧电感下面的器件塞到芯片底部:布局需要改动。器件并未对齐,并且都干涉了:器件是需要整体的中心对齐放置。上述一致原因的布局问题:布局需要优化,中心对齐好,器件之间不要干涉。DCDC电源主干道的电容是要靠

扫码关注

扫码关注