- 全部

- 默认排序

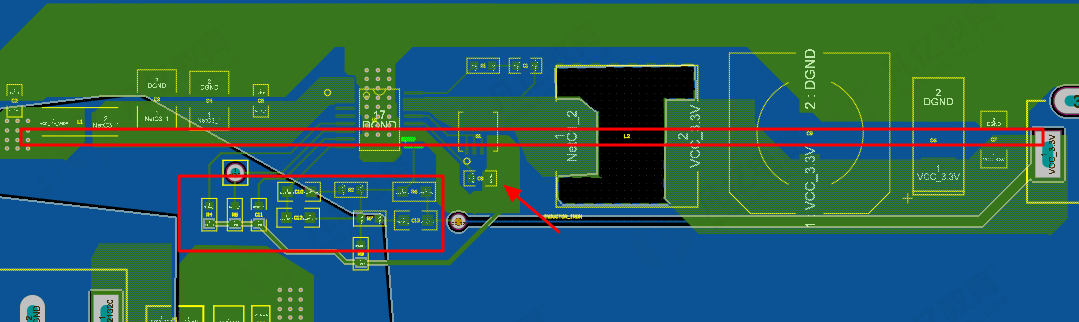

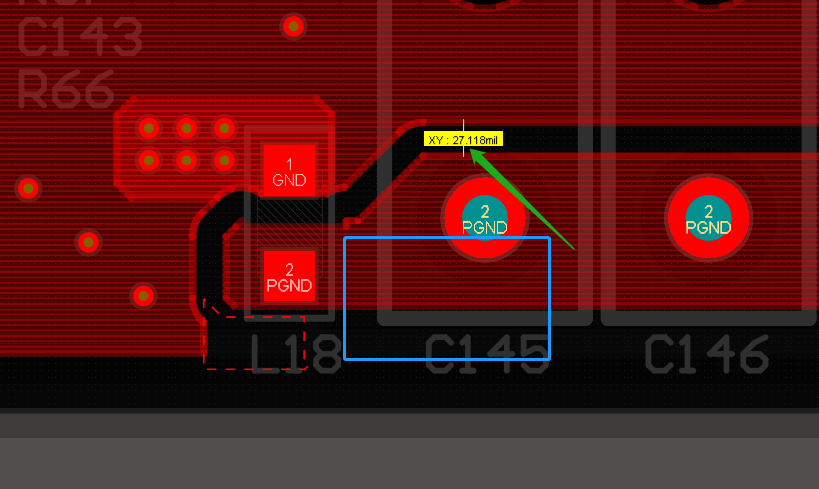

器件尽量中心对齐,相邻器件尽量朝一个方向放置不要任意角度铺铜,铜皮任意角度的斜边全是毛刺铺铜尽量避免直角锐角要求单点接地电容离芯片管脚太远,器件应靠近对应管脚放置,连接线尽量缩短焊盘要从短边出线,避免从焊盘长边出线和四角出线以上评审报告来源

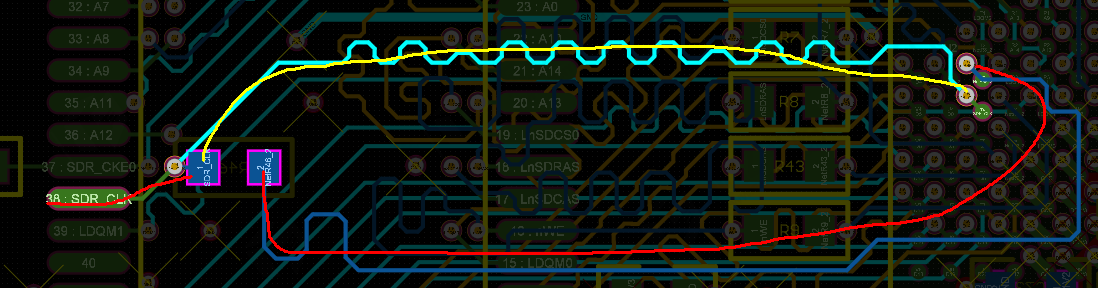

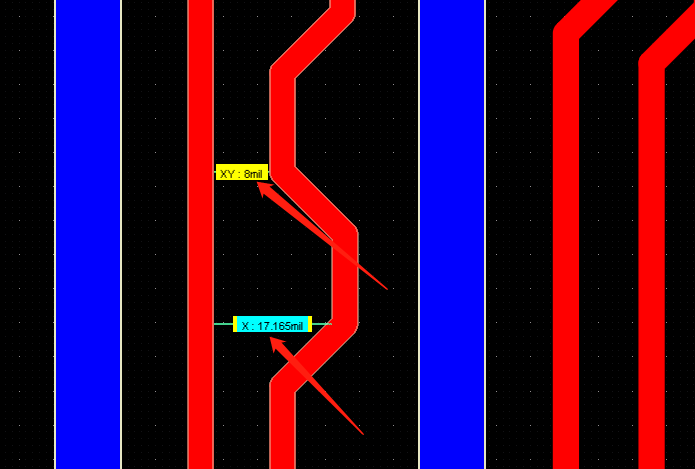

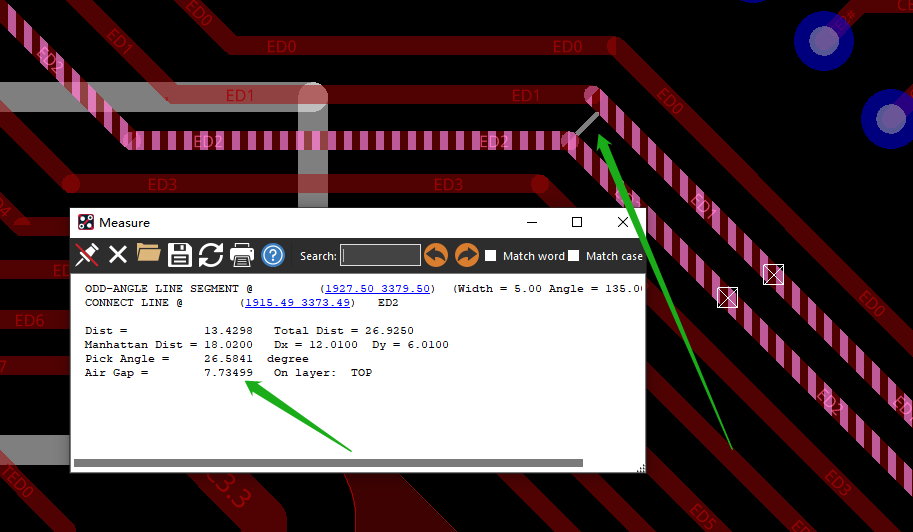

时钟信号等长错误地址线等长组有几个信号等长不到目标长度,电阻到芯片段加入一起等长应避免走线造成信号回路以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.ta

器件遵循先大后小原则摆放,大电容放到前面小电容放大电容后相邻电路电感应朝不同方向垂直放置焊盘出线避免从长边、四角出线,铺铜、走线尽量避免直角锐角器件尽量中心对齐,相邻器件尽量朝一个方向放置以上评审报告来源于凡亿教育90天高速PCB特训班作业

5G技术的出现承诺了闪电般的网速和无缝连接。然而,一些用户报告称,与之前的4G连接相比,信号变弱了。本文旨在深入探讨这一现象背后的原因,并揭示导致5G信号变弱的因素。通过研究和分析,我们将探索5G网络实施过程中出现的技术方面和潜在挑战。为什

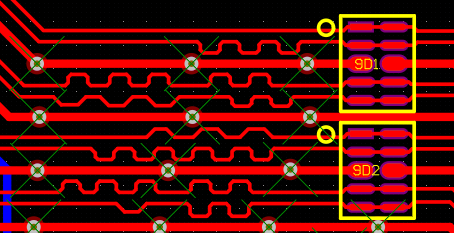

差分线对内等长凸起高度不能超过线距的两倍2.存在开路3.注意差分需要进行对内等长,误差5mil4.注意等长尽量不要直角,建议钝角,后期自己优化一下5.后期自己在地平面和电源平面指定网络进行连接6.差分需要按照阻抗线距走,后期自己注意一下以上

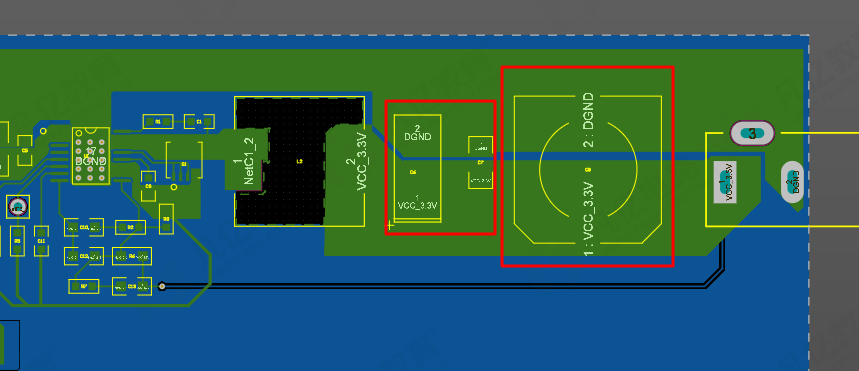

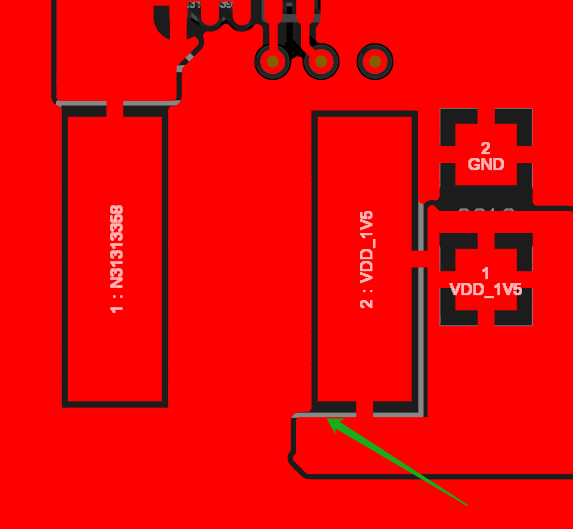

注意数据线之间等长需要满足3W间距,后期自己检查一下其他组是否满足2.注意模拟信号尽量一字型布局3.跨接间距最少要保证1.5mm,一般建议2mm,有器件的地方可以不满足4.电源输出打孔要打在最后一个电容后面5.反馈信号需要走10mil的线进

差分等长不耦合,差分对间等长可以用差分等长命令上面也要包地处理RJ45:提交作业的时候铺一下铜走线不要从电阻中间穿过以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://

跨接器件旁边尽量多打地过孔,间距最少1.5mm,建议2mm,有器件的地方可以不满足2.网口差分需要进行对内等长,误差5mil3.模拟信号需要一字型布局,走线加粗4.注意过孔不要上焊盘5.反馈信号走线需要加粗到10mil6.注意确认一下此处是

DDR3 2片:电感内部挖空处理。注意电源铺铜不要出现这种瓶颈处:等长线注意要保证3W间距,去调整出来:数据线需要满足等长误差,还存在报错:数据线也要满足3W间距自己注意走线跟过孔的间距规则:分割带尽量大于20MIL:以上评审报告来源于凡亿

DD3 四片:注意不要出现这种锐角走线:负片层并未赋予网络:注意设计完了之后检查下走线的连接性:并未保证3W间距原则:差分对内等长注意规范:差分对内等长误差为5MIL:以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特

扫码关注

扫码关注