- 全部

- 默认排序

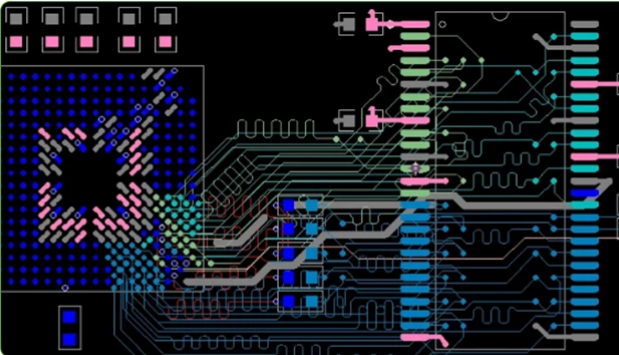

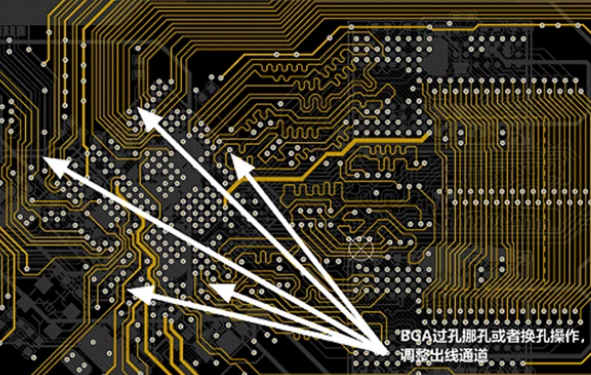

小白在设计印制电路板时常常因为自身基础知识及经验不够,忽略电磁干扰方面的错误,造成电路板结果不如预期,导致费时费力费钱,那小白该如何在PCB设计时如何抑制电磁干扰,提高效率?1、印制电路板的选取印制电路板有单面、双面和多层板之分。单面和双面

在印制电路板(PCB)的布局布线环节,很多小白通常会以为PCB的布局布线无需抑制电磁干扰,导致成品出来后依然存在电磁兼容性问题。那么我们该如何在PCB布局布线中抑制电磁干扰,争取提高设计效率?1、电源线的布置PCB板上的电源供电线由于给板上

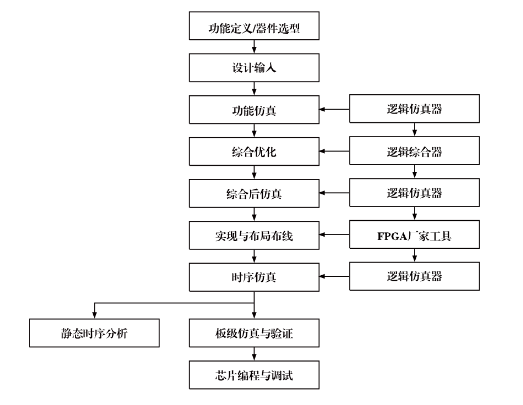

FPGA作为主流的硬件编程语言,问世以来一直备受工程师青睐,但有很多小白不太了解FPGA项目的开发流程及注意事项,导致多走歪路,所以本文将重点分享FPGA的开发流程及注意事项。1、功能定义/器件选型在FPGA 设计项目开始之前,必须有系统功

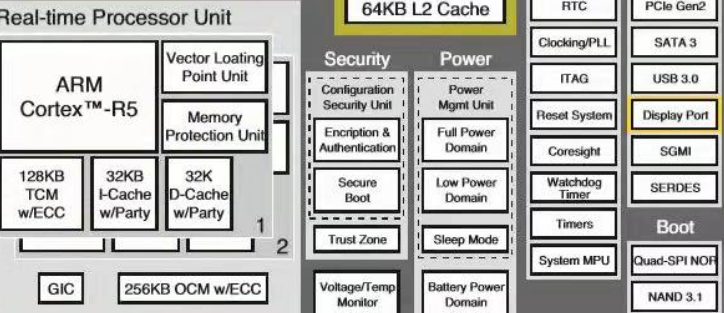

目前微电子技术已发展到SOC阶段,即集成系统阶段,相对于集成电路(IC)的设计思想有着革命性的变化。FPGA自然也不例外,但有很多小白不太清楚基于FPGA芯片的SOC开发流程,所以本文将回答这个问题。1、基于FPGA的SOC设计方法目前,由

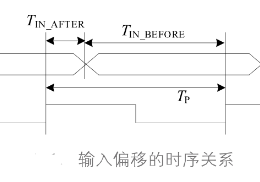

FPGA的时序分析及时序约束一直以来是小白难以搞懂的知识点,经常劝退不少小白,尤其是其中的偏移约束,所以本文将重点谈谈偏移约束。偏移约束属于基本时序约束,规定了外部时钟和数据输入输出引脚之间的相对时序关系,智能用于端口信号,不能应用于内部信

随着微电子技术的发展,电子产品技术更新迭代速度加快,这也促使了大部分的电子产品的电磁干扰基本上是以共模干扰和差模干扰为主,但很多小白学习电磁兼容总会遇到一些问题,所以本文将挑选两个问题进行回答。1、共模干扰电流是什么?一般来说,共模干扰是以

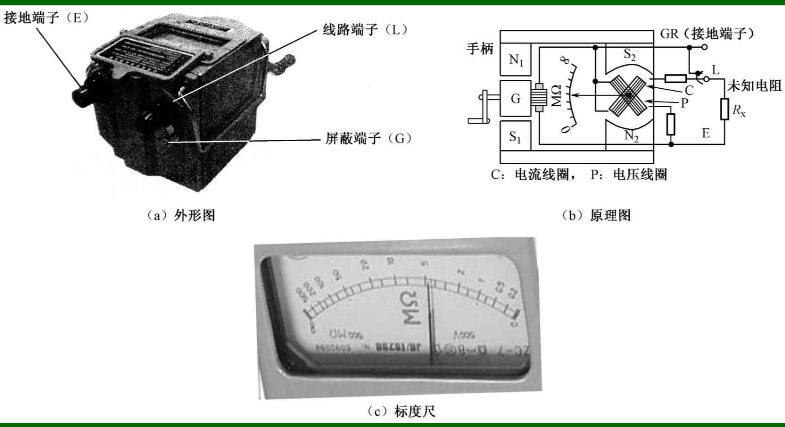

兆欧表的型号及规格详解

兆欧表作为电工常用的测量仪器仪表,涉及多个行业,用途广泛是小白需要重点了解存在的设备,但很多小白面对不同型号不同规格的兆欧表,都很困惑,所以本文将搜集平台内容,归纳总结兆欧表的型号及规格。兆欧表主要用于检查电气设备、家用电器或电气线路对地及

PlanAhead虽然很少被人广为所知,但作为FPGA项目的布局布线常用软件之一,重要性不亚于其它EDA软件,但由于很多小白对它不甚了解,所以本文将搜集平台信息,总结出PlanAhead的功能及使用方法。PlanAhead工具简化了综合与布

在FPGA设计时,我们总会遇到各种各样的设计难题,并发愁如何解决,所以小编将搜集网络上九个小白最头疼的FPGA设计问题,并进行回答,希望对小白有所帮助。1、如何控制XST插入buffer?①用buffer_type约束,具体使用方法在XST

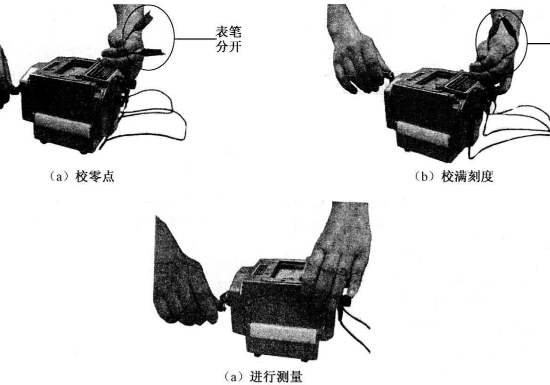

兆欧表作为常见的测试仪器仪表之一,应用广泛,主要分为手摇发电机式兆欧表和电池供电式兆欧表,但有很多小白不清楚它们的使用方法,所以本文将谈谈这两种兆欧表的使用方法及注意事项。1、手摇发电机式兆欧表准备工作及注意事项:①使用时应放在平稳牢固的地

扫码关注

扫码关注