- 全部

- 默认排序

小白初接触FPGA逻辑芯片,可能会困惑EPLD、CPLD、FPGA等这些英文名词,也不知道它们有什么用,所以本文将为小白一一解答这些问题,希望对小伙伴们有所帮助。1、GAL(Generic Array Logic)全称为通用阵列逻辑,是19

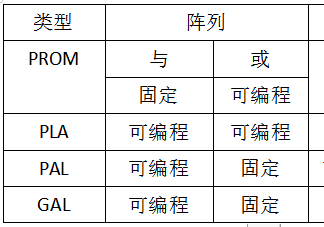

可编程逻辑器件(PDL)是小白初入FPGA等相关领域需要重点了解的基础知识之一,但有很多小白不太清楚简单PLD的基本结构、特点、分类及区别联系,所以本文将搜索平台内容,归纳总结知识,希望对小伙伴们有所帮助。简单PLD包括PROM、PLA、P

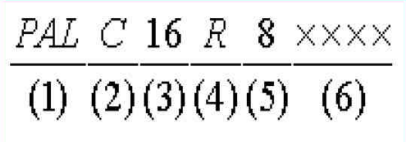

PAL是可编程逻辑器件(PDL)的细分种类之一,不像CPLD、EPLD等,PAL默默无闻但作用巨大,应用广泛。然而很多小白经常跳过PAL来学习其他内容,这是不对的,所以本文将重点谈谈PAL器件的命名方式、阵列结构、输出电路。1、PAL器件的

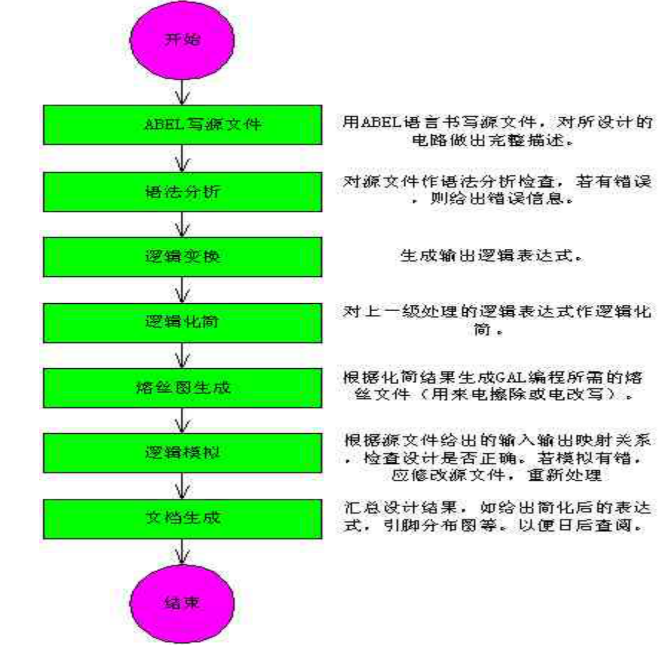

GAL器件是可编程逻辑器件(PDL)器件的分类之一,也属于FPGA/ASIC的基础器件,但对于很多小白来说,是不熟悉的存在,加上关于GAL的相关资料较少。为帮助小白更好地学习,本文将分享GAL器件的特点、开发工具及设计译码器步骤,希望对小伙

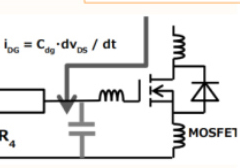

同步电路是数字电路中常见的电路设计方法之一,但部分小白对该类电路不甚了解,甚至遇见该类设计是惘然无措,所以本文将重点分析同步电路的设计准则,并分享电路设计的优点。同步电路是指所有电路在同一个公共时钟的上升沿或下降沿的触发下同步地工作。但在实

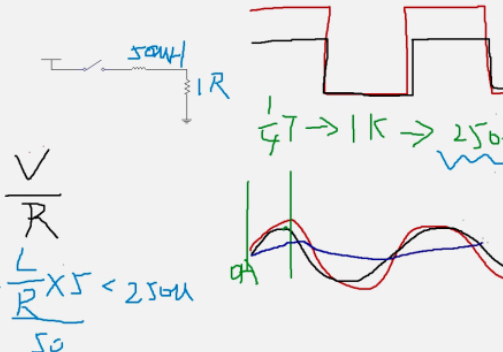

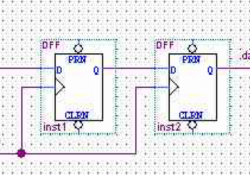

小白在设计数字电路,如同步/异步时序电路时常常会碰到毛刺或者亚稳态的问题,但很多小白对亚稳态问题措手不及,经常搞错电路导致系统崩溃,所以本文将归纳总结,分析数字电路中的亚稳态。在同步电路或异步电路中,如果触发器的setup时间或hold时间

同步时序电路和异步时序电路是数字电路的重要内容,也是小白学习数字电路时重点学习的电路设计课程之一,但如果我们遇见异步时钟域数据同步问题,我们该怎么办?处理跨时钟域问题的核心在于要保证下级时钟对上级数据采样的setup时间或hold时间满足要

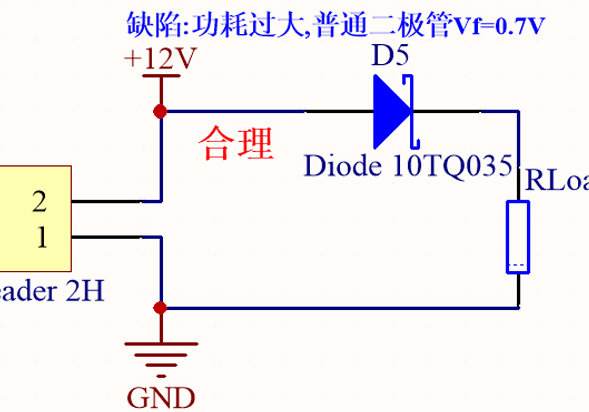

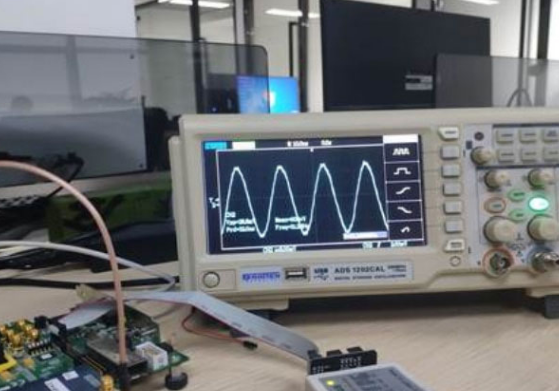

有很多小白想要从事FPGA,选择成为FPGA工程师,但对于FPGA的开发流程及内容不太了解,所以本文将归纳总结FPGA的具体开发流程,希望对小伙伴们有所帮助。HDL(Hardware Design Language)和原理图是两种最常用的数

对于FPGA工程师来说,RTL设计是常见的FPGA必不可少的设计环节,但对于小白来说,很多小白不懂RTL设计,甚至数次在FPGA或RTL设计常走歪路,所以本文将详谈RTL设计。1、使用Verilog进行RTL设计使用Verilog进行RTL

FPGA在逻辑芯片项目工程中是常见的,很多FPGA在项目中基本上都是以HDL代码来设计逻辑电路,但很多小白编写的HDL代码基本上都是不符合需求,费时费力,所以如何快速判断HDL代码是可行的?任何符合HDL语法标准的代码都是对硬件行为的一种描

扫码关注

扫码关注