- 全部

- 默认排序

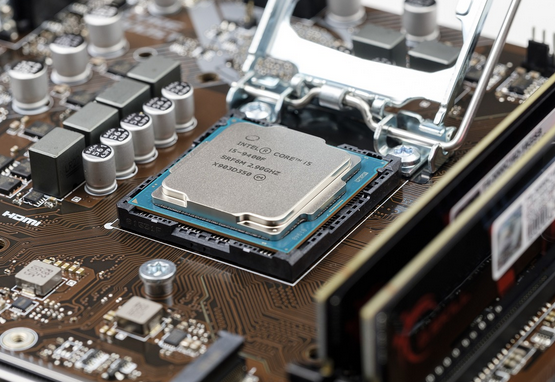

在电子设备的制造与布线过程中,经常会遇见屏蔽层设计问题。问题来了,如果屏蔽层上布有电缆线,如何正确接地,降低电磁影响?下面将详细讨论这些问题。1、单点接地方案单点接地方案是最基础的接地方式,它要求所有的地线都汇聚到一个点上。这种方案在简单电

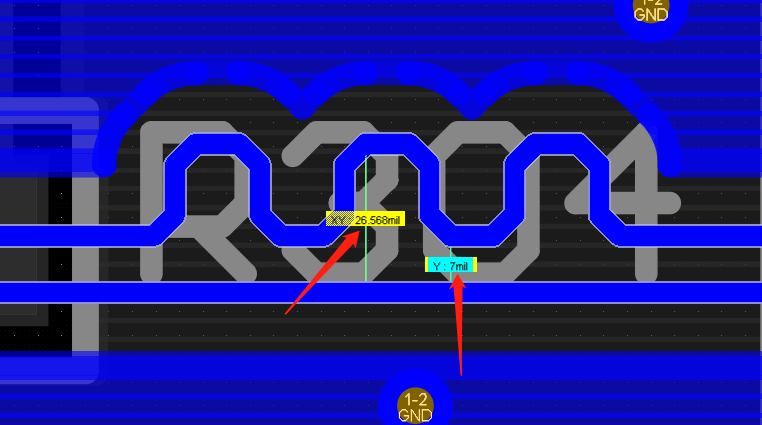

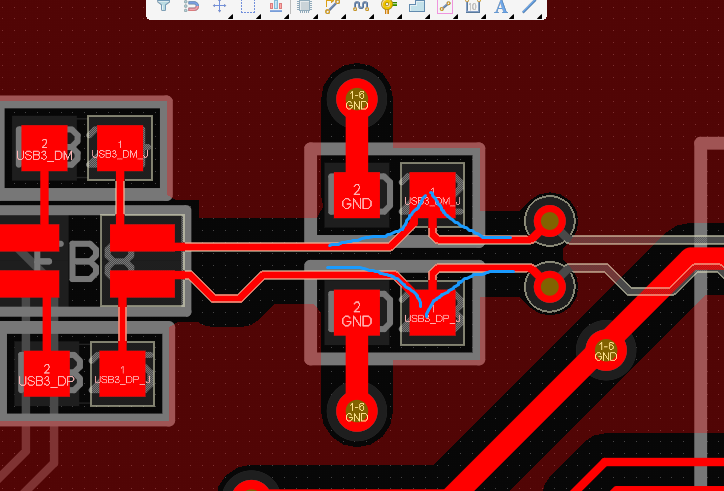

注意差分对内等长凸起高度不能超过线距的两倍差分尽量哪里不耦合就在哪里绕,尽量不要在中间绕蛇形2.差分出线需要耦合,后期自己调整一下3.走线尽量不要有锐角,后期自己优化一下4.时钟信号需要包地处理,并在地线上打孔,建议50-100mil一个以

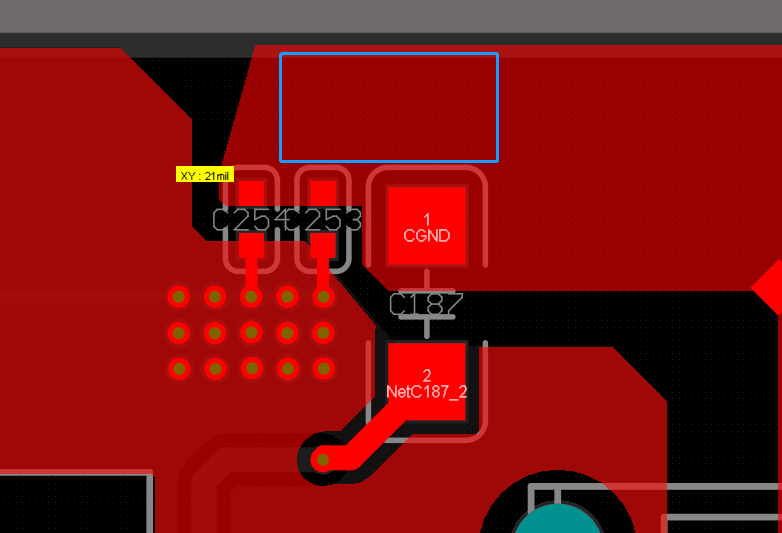

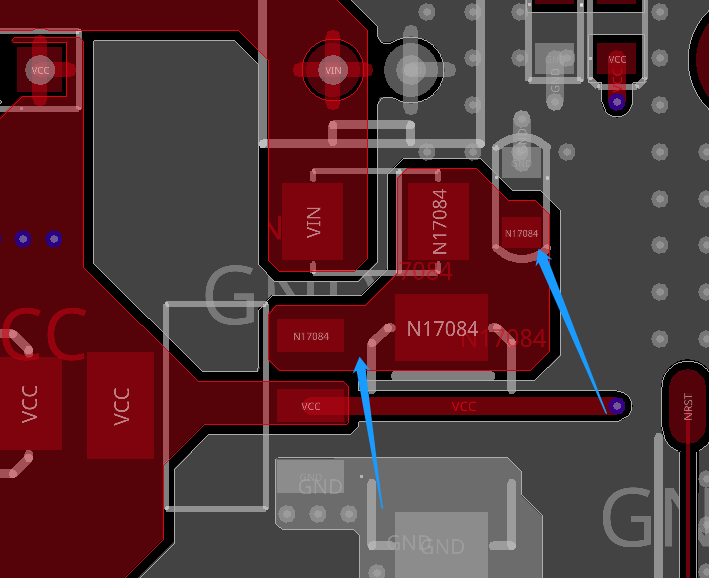

跨接器件旁边尽量多打地过孔2.焊盘出线需要优化一下3.差分走线不满足阻抗线距规则4.晶振下面不要放置器件和走线,包地需要在地线上打过孔5.注意打孔尽量不要打在焊盘中心6.走线一层连通,不用打孔7.走线需要优化一下,尽量45度8.RX等长误差

跨接器件旁边要多打地过孔2.焊盘出线需要优化一下3.晶振需要走类差分4.确认一下此处是否满足载流5.TX和RX中间尽量添加一根地线进行分隔6.焊盘需要开窗处理,后期没法进行上锡焊接以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需

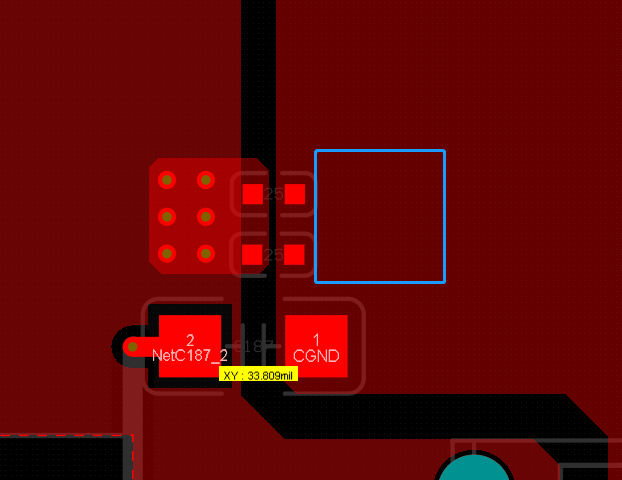

地分割间距要保证2mm,有器件的地方可以不满足2.网口除差分信号外,其他的都需要加粗到20mil3.晶振需要包地处理,并在地线上4.BGA里面的铜皮建议挖空处理5.焊盘到孔的间距过近,建议6mil,后期自己优化一下以上评审报告来源于凡亿教育

注意焊盘出线规范后期自己优化一下2.差分对内等长凸起高度不能超过线距的两倍3.注意差分走线要尽量耦合4.一层连接不用打孔,注意不要出现STUB线头5.CC1和CC2属于重要信号,走线需要加粗6.注意差分信号包地要在地线上打上地过孔7.过孔需

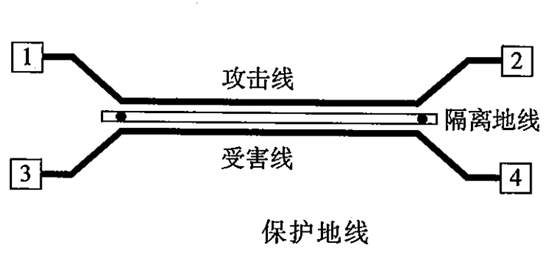

在高频PCB设计中,如何降低串扰问题的影响,是很多电子工程师必须考虑的首要问题,串扰,即信号线之间的互相干扰,可能导致信号失真、误码率上升,从而影响整个电路的性能和稳定性,那么如何从布局布线方面入手?1、利用地线隔离在布线空间允许的条件下,

包地与串扰

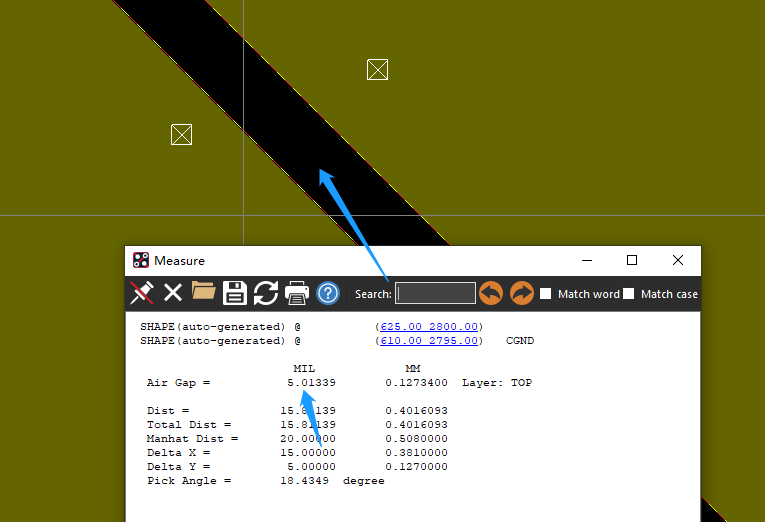

工程界常常使用保护地线进行隔离,来抑制信号间的相互干扰。的确,保护地线有时能够提高信号间的隔离度,但是保护地线并不是总是有效的,有时甚至反而会使干扰更加恶化。使用保护地线必须根据实际情况仔细分析,并认真处理。保护地线是指在两个信号线之间插入一根网络为GND的走线,用于将两个信号隔离开,地线两端打GN

电容按照先大后小摆放2.电源从最后一个电容后面进行输出3.差分信号包地,尽量在地线上打上过孔4.滤波电容靠近管脚均匀摆放5.晶振包地要包全注意过孔不要上焊盘以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以

在电子设计中,经常会遇见两面板设计,这样做的好处是设计简洁且高效,然而很多工程师都在发愁其地线(GND)与电源线(Vcc/Vdd)如何走线,今天针对这个问题,本文将详细分析原因并回答,希望对小伙伴们有所帮助。首先,地线和电源线在电路中很重要

扫码关注

扫码关注