- 全部

- 默认排序

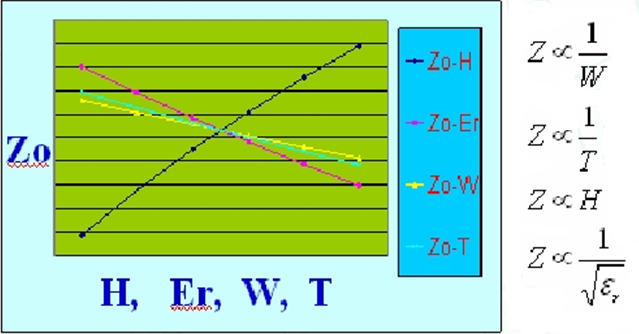

一般来说,影响PCB特性阻抗的因素:介质厚度H、铜的厚度T、走线的宽度W、走线的间距、叠层选取的材质的介电常数Er、阻焊的厚度。一般来说,介质厚度、线距越大阻抗值越大;介电常数、铜厚、线宽、阻焊厚度越大阻抗值越小。这些因素与特性阻抗的关系如图1-20所示。 图1-20 影响PCB特性阻抗分布图第一个:介质厚度,增加介质厚度可以提高阻抗,降低介质厚度可以减小阻抗;不同的半固化片有不同的胶含量与厚度。其压合后的厚度与压机的平整性、压板的程序有关;对所使用的任何一种板材,要取得其可生产的介质

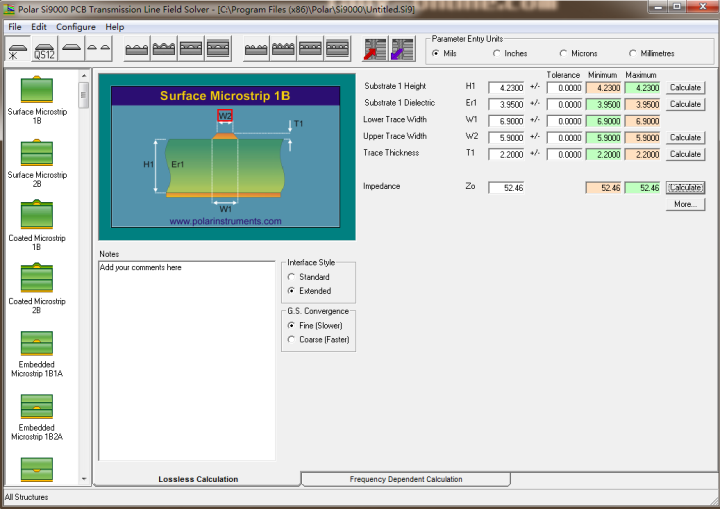

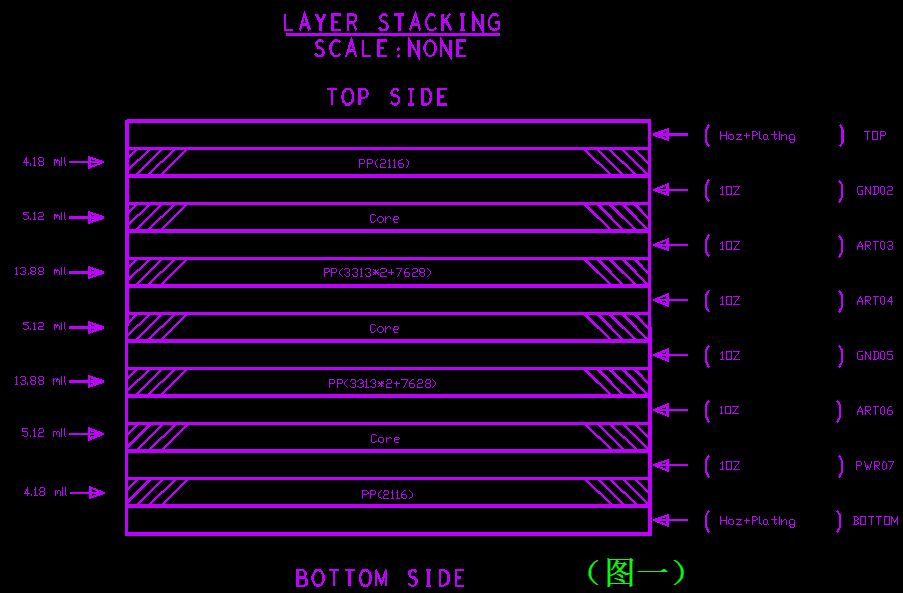

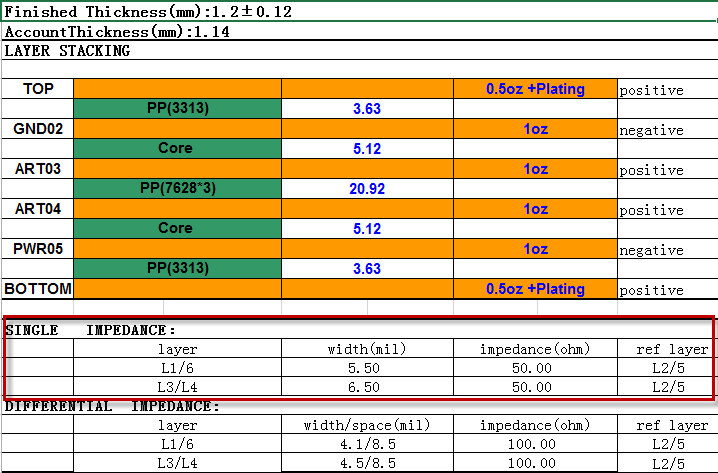

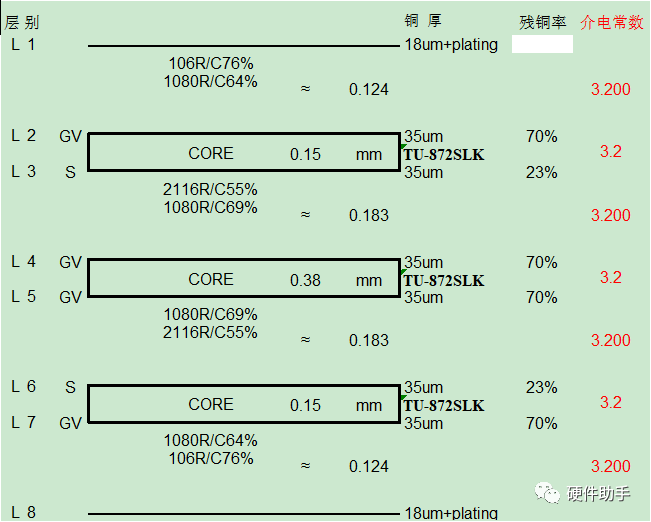

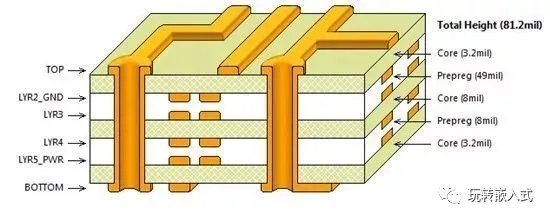

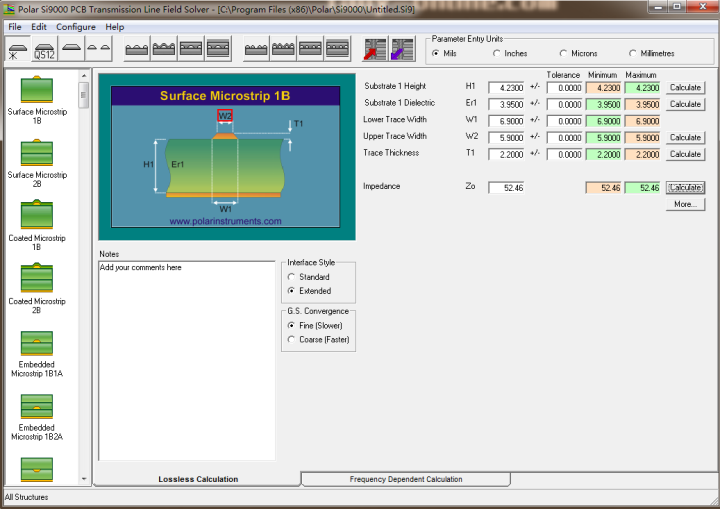

特性阻抗,体现在PCB板上,主要是通过叠层、线宽、线距。在PCB版图布局完成以后,我们要对PCB板进行层叠设计,将PCB板按照一定的厚度叠好以后,根据层叠结构,通过SI9000这个软件来进行阻抗线宽的计算,然后根据计算好的线宽来进行布线,即可达到控制特性阻抗的效果。如图1-21所示,1.6MM的厚度的PCB板的层压结构。TOP0.5oz +PlatingPP(2116)4.23GND021ozCore20.08ART031ozPP(1080*2)4.59PWR041ozCore20.08GND0

常见的一些叠层文件的形式多种多样,给出的方式也多样化,有的通过excel形式给出,有的通过制板说明文件给出,有的直接放在PCB设计文件中,通过Gerber文件给出。不管是哪种方式,其目的都是为了让设计人员有据可依,能设计出满足功能性能要求的PCB,让生产加工人员能制造出满足设计性能的PCB。 下面这种是将所有的信息都直接放在PCB设计中,并且生成Gerber文件一起提交到工厂。

在PCB的EMC设计考虑中,首先涉及的便是层的设置;单板的层数由电源、地的层数和信号层数组成;在产品的EMC设计中,除了元器件的选择和电路设计之外,良好的PCB设计也是一个非常重要的因素。

答:一般来说,影响PCB特性阻抗的因素:介质厚度H、铜的厚度T、走线的宽度W、走线的间距、叠层选取的材质的介电常数Er、阻焊的厚度。一般来说,介质厚度、线距越大阻抗值越大;介电常数、铜厚、线宽、阻焊厚度越大阻抗值越小。这些因素与特性阻抗的关系如图1-20所示。 图1-20 影响PCB特性阻抗分布图第一个:介质厚度,增加介质厚度可以提高阻抗,降低介质厚度可以减小阻抗;不同的半固化片有不同的胶含量与厚度。其压合后的厚度与压机的平整性、压板的程序有关;对所使用的任何一种板材,要取得其可生产的

答:特性阻抗,体现在PCB板上,主要是通过叠层、线宽、线距。在PCB版图布局完成以后,我们要对PCB板进行层叠设计,将PCB板按照一定的厚度叠好以后,根据层叠结构,通过SI9000这个软件来进行阻抗线宽的计算,然后根据计算好的线宽来进行布线,即可达到控制特性阻抗的效果。如图1-21所示,1.6MM的厚度的PCB板的层压结构。TOP0.5oz +PlatingPP(2116)4.23GND021ozCore20.08ART031ozPP(1080*2)4.59PWR041ozCore20.08GN

答:在进行阻抗、层叠设计的时候,主要的依据就是PCB板厚、层数、阻抗值要求、电流的大小、信号完整性、电源完整性等,一般参考的原则如下:l 叠层具有对称性;l 阻抗具有连续性;l 元器件面下面参考层尽量是完整的地或者电源(一般是第二层或者倒数第二层);l 电源平面与地平面紧耦合;l 信号层尽量靠近参考平面层;l 两个相邻的信号层之间尽量拉大间距。走线为正交;l 信号上下两个参考层为地和电源,尽量拉近信号层与地层的距离;l&nbs

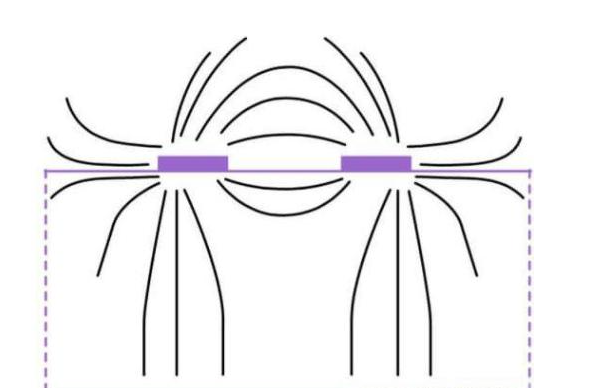

答:降低串扰的方法有如下几种:增加信号路径之间的间距、用平面作为返回路径、使耦合长度尽量短、在带状线层布线、减小信号路径的特性阻抗、使用介电常数较低的叠层、在封装和接插件中不要共用返回引脚、使用两端和整条线上有短路过孔的防护布线,更多关于PCB中降低串扰的处理方法,可以到本书学习论坛“PCB联盟网”免费下载学习。

扫码关注

扫码关注