- 全部

- 默认排序

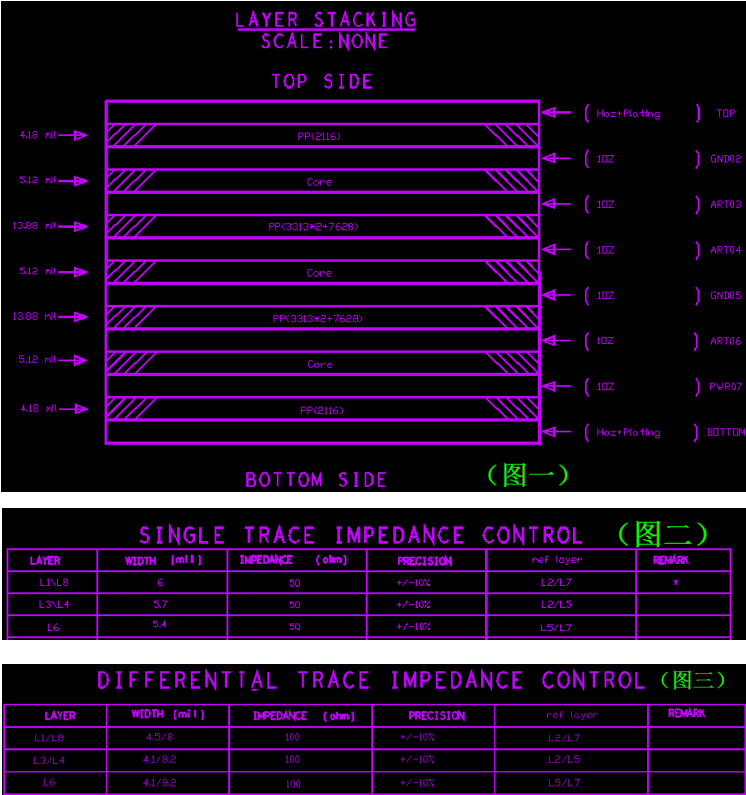

学习目标: 1、掌握常见叠层的阻抗模型 2、掌握如何根据新盘厚度和PP片厚度叠层出要求的厚度板 3、掌握利用SI9000计算阻抗值的方法

随着高速电路的不断涌现,PCB板的复杂度也越来越高,为了避免电气因素的干扰,信号层和电源层必须分离,所以就牵涉到多层PCB的设计。在设计多层PCB电路板之前,设计者需要首先根据电路的规模、电路板的尺寸和电磁兼容(EMC)的要求来确定所采用的电路板结构,也就是决定采用4层,6层,还是更多层数的电路板。这就是设计多层板一个简单概念。 确定层数之后,再确定内电层的放置位置以及如何在这些层上分布不同的信号。这就是多层PCB层叠结构的选择问题。层叠结构是影响PCB板EMC性能的一个重要因素,一个好的叠层设计方案将会

这里软件版本是Altium designer 19 ,主要介绍我们的各个叠层的含义和作用,包括我们的顶层,底层 ,机械层,丝印层,阻焊层,钢网层,钻孔层等层的作用,以及过孔和焊盘的各个层的含义作用,以及我们的开窗处理的层的选择。

本软件采用的软件讲解使用我们的Altium designer 19 ,主要讲解关于四层板常用的叠层,以及我们常用的叠层的设计的要素,设计叠层的一般参考的要点是那些,如何进行一个叠层的选用。

在我们到PCB设计后期,随着我们设计水平越来越高,就会接触到四层,六层或者八层等等的PCB板。那么,就需要我们在内层添加层,就是我们说的叠层的添加,所以这项操作非常重要,我们就以AD19来进行视频讲解。

★掌握PCB设计常用的设计技巧及熟悉PCB设计的整体流程★掌握DDR3设计的知识要点★掌握3W原则的PCB设计★了解T点拓扑结构及设计规则★掌握蛇形等长走线,阻碍线的使用★掌握叠层阻抗计算的方法★了解常见EMC的PCB处理方法

1.多设备学习:手机、平板、电脑,学习更便捷,提升更高效 2.名师讲解:真实(置身课堂的真实感受)、 生动(授课形式更灵活、直观)、高清(悦目的视觉体验 3.全面教学资料:经典案例、常用封装库、设计工具、常见问题集、高手经验、常用规范

什么是阻抗?多层板应该怎么去叠?PCB走线应该走多粗?这些问题是不是很熟悉,这是很多工程师的老大难问题,其实这就是没有搞清楚叠层跟阻抗的问题。我们本次直播全面剖析多层板的叠层控制以及阻抗如何计算,教会大家轻松解决高速PCB设计中的阻抗与叠层。

1、 需要要做阻抗的信号线,应该严格按照叠层计算出来的线宽、线距来设置。比如射频信号(常规50R控制)、重要单端50R、差分90R、差分100R等信号线,通过叠层可计算出具体的线宽线距(下图示)。2、 PCB设计的线宽线距应该考虑所选PCB生产工厂的生产工艺能力,如若设计时设置线宽线距超过合作的PCB生产厂商的制程能力,轻则需要添加不必要的生产成本,重则导致设计无法生产。一般正常情况下线宽线距控制到6/6mil,过孔选择12mil(0.3mm),基本80%以上PCB生产厂商都能生产,生

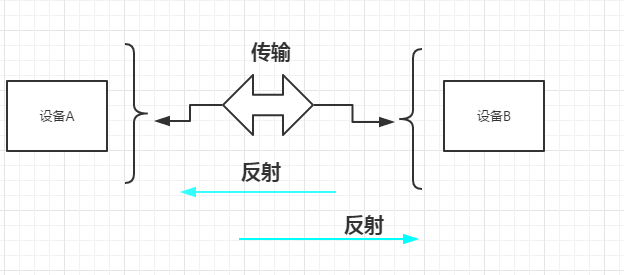

差分走线,信号换层过孔数量,等长长度把控,阻抗控制要求,跨分割的损耗,走线拐角的位置形状,绕线方式对应的插损和回损,布局不妥当造成的一系列串扰和叠层串扰,布局不恰当操作焊盘存在的stub。

扫码关注

扫码关注