- 全部

- 默认排序

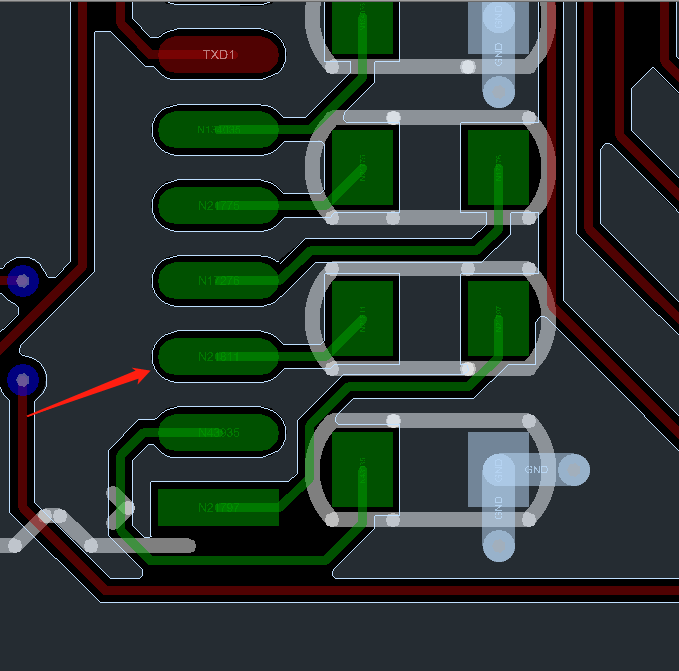

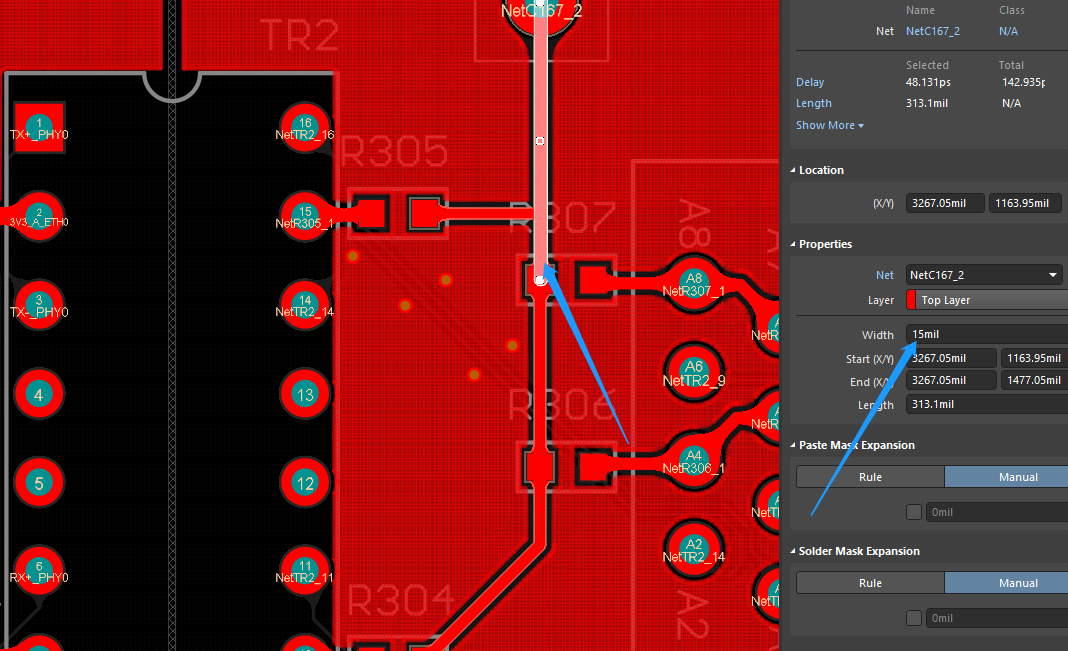

RS232的升压电容走线需要加粗2.电源输出打孔要打在滤波电容后面3.SD需要创建等长组进行等长,误差范围300mil4.以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https

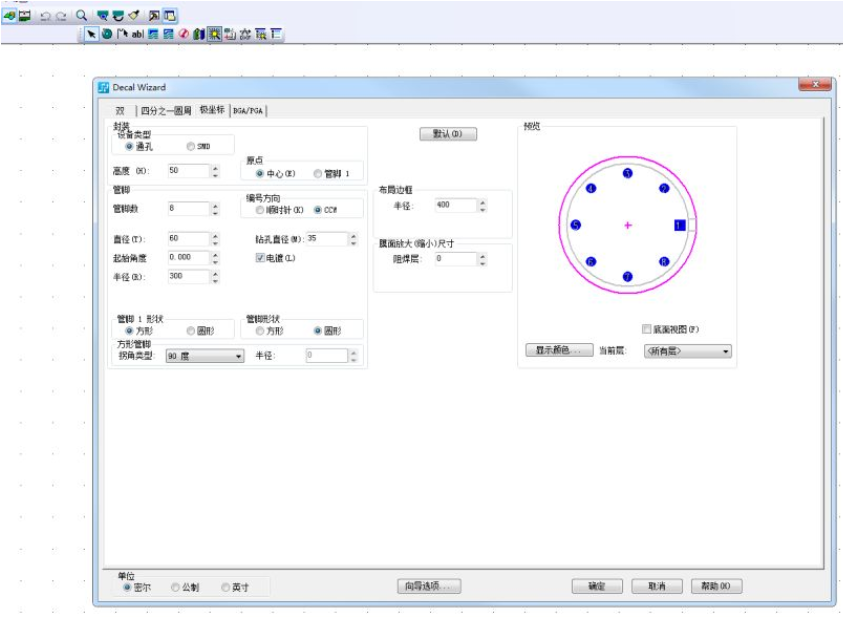

创建BGA IC封装也是可以使用PCB封装向导去进行设置创建。1、点击“绘图工具栏”图标,弹出对应的分列,点击“向导”,弹出“Decal Wizard”对话框,如图1所示。图1“Decal Wizard”对话框2、然后点击左上角的BGA/P

公制亦称“米制”、“米突制”。1858年《中法通商章程》签定后传入中国的一种国际度量衡制度。创始于法国。在PCB中单位为MM(毫米)英制:英国、美国等英语国家使用的一种度量制。长度主单位为英尺,重量主单位为磅,容积主单位为加仑,温度单位为华

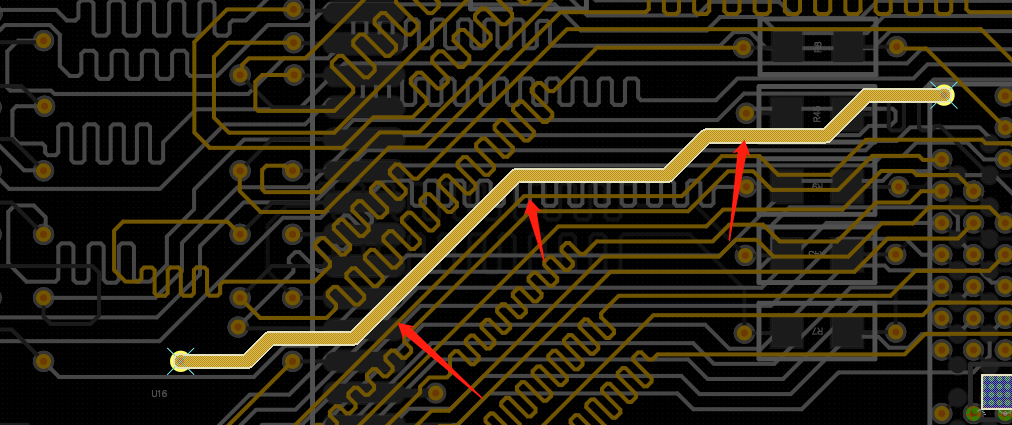

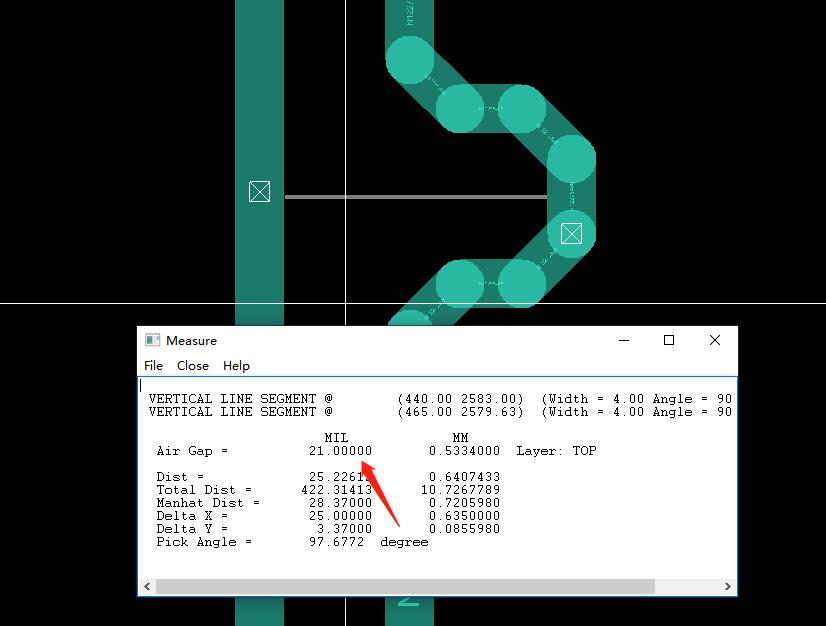

差分走线要尽量耦合2.小电容靠近管脚摆放3.焊盘中心出线至外部才能拐线处理,避免生产出现虚焊4.RX和TX需要创建等长组进行等长,误差100mil,中间用根地线进行分隔5.时钟信号需要包地处理6.焊盘需要添加阻焊进行开窗处理,要不后期不能进

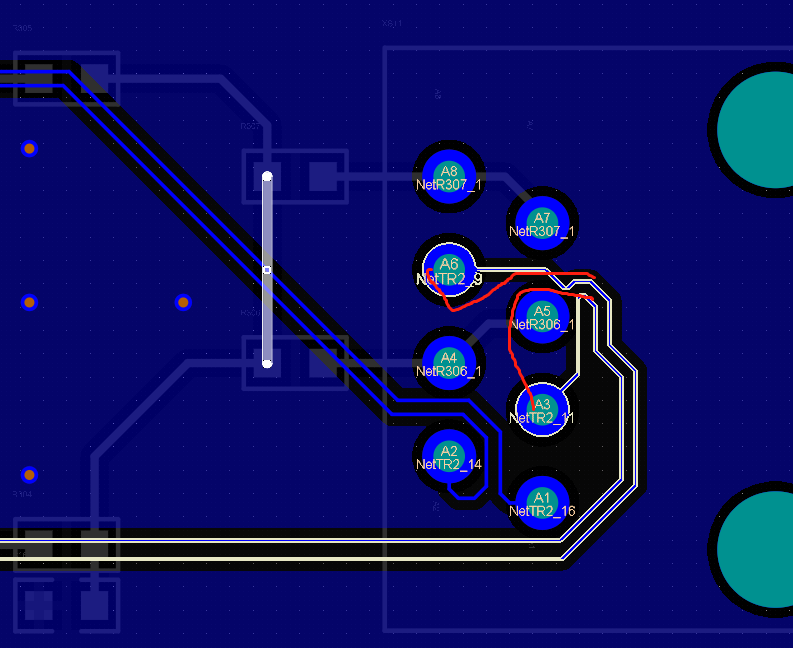

机壳地以及电源地没有正片铺铜处理也没有负片分割处理,注意地是需要处理的:变压器上除了差分信号,其他的加粗20MIL走线:电源层也并未处理电源 :TX RX信号之间用GND走线隔开:RX TX没有创建等长组进行等长:差分对内等长误差为5MIL

网口除差分信号外,其他的都需要加粗到20mil2.差分出线要尽量耦合3.差分需要进行对内等长,误差5mil4.注意RX和TX创建等长组,走线需要满足3W间距5.注意线宽尽量保持一下6.过孔尽量不要打在两个焊盘中间,7.焊盘上存在多余的线头以

在绘制原器件封装的时候,如果对管脚一个一个去进行放置会影响效率,因此可以通过对管脚进行复制来实现快速放置管脚。第一步:在元件界面点击添加端点图标,先进行一个管脚的放置,如图1所示图1 放置管脚示意图第二步:选中放置的管脚进行右键,选择复制选

在绘制原理图元件的时候,有时管脚数量过多,管脚编号会显的特别密。既可以选择隐藏管脚编号,显示主要目的就是分辨出信号管脚。第一步:在创建元件界面,执行菜单命令设置-显示颜色,如图1所示图1 显示颜色选项示意图第二步:在弹出的显示颜色窗口中,然

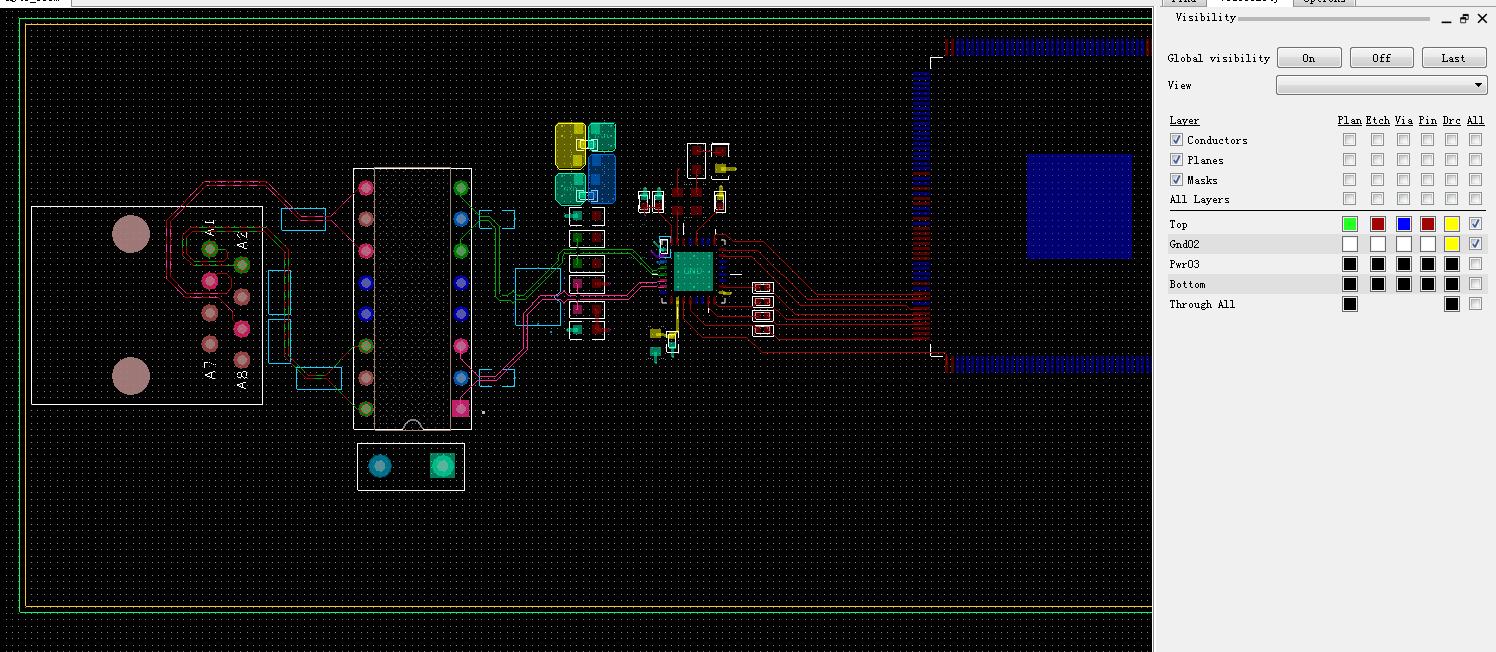

数据线与地址线之间的分割线上需要打地过孔,建议150mil一个第4层数据线和地址线之间也需要添加一根地线分开2.等长存在误差报错3.有器件连接的网络要创建Xsignals进行等长4.注意电源需要再电源层处理一下,铺铜进行连接5.注意器件不要

差分对内等长凸起高度不能超过线距的两倍2.差分出线要尽量耦合3.TX和RX要创建等长组进行等长4.确认一下此处是否满足载流,加粗线宽以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:

扫码关注

扫码关注