- 全部

- 默认排序

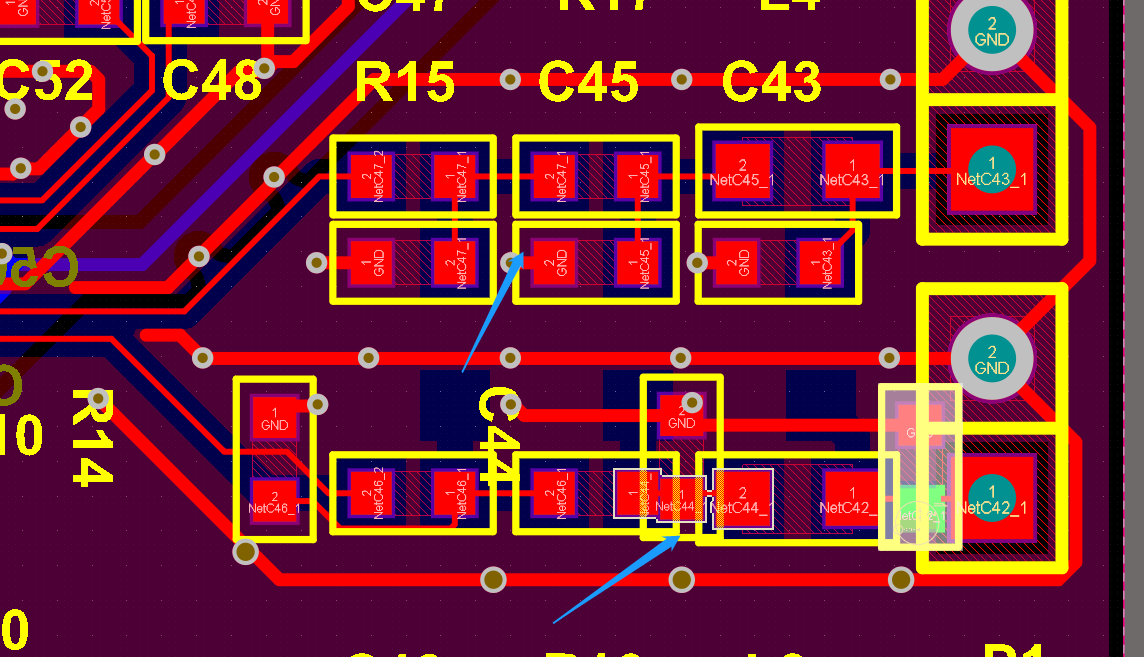

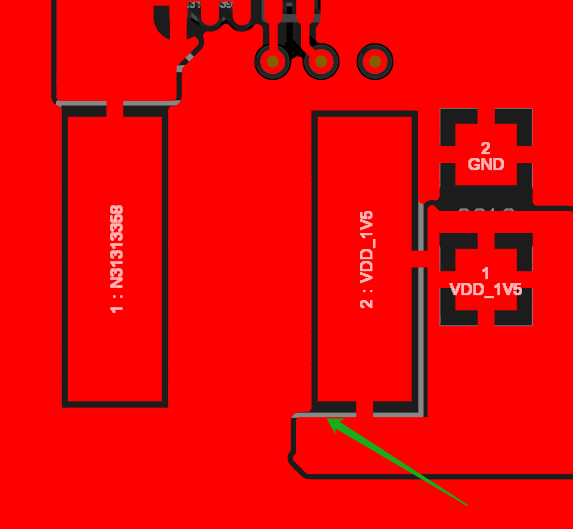

模拟信号要一字型布局,走线加粗处理4层板不用打埋盲孔,直接打通孔即可铜皮和走线选择一种即可,不用重复选择.地分割间距要满足1.5mm,,建议2mm,有器件的地方可以不满足晶振走类差分需要再优化一下变压器需要所有层挖空处理注意存在多处drc错

注意4层板不需要用埋盲孔2.反馈信号需要加粗到10mil,注意焊盘出线规范3.注意变压器负片层挖空处理,地分割注意规范4.注意丝印调整尽量不要干涉器件丝印以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访

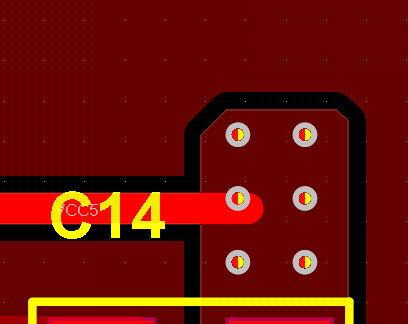

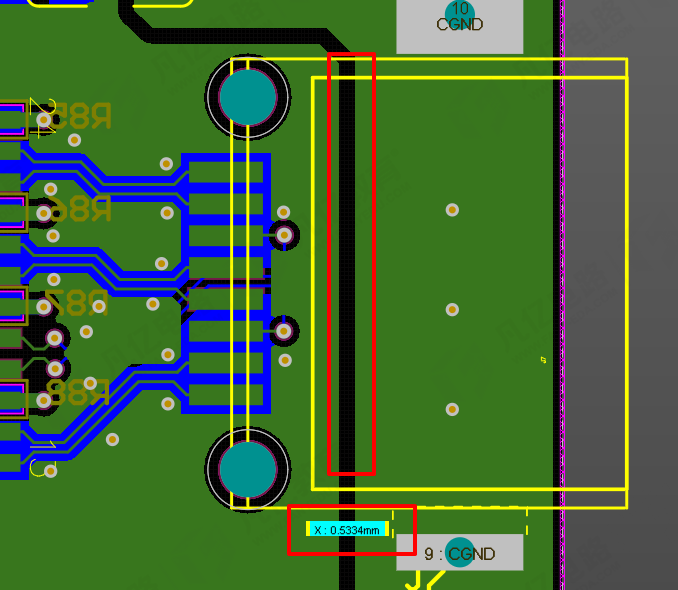

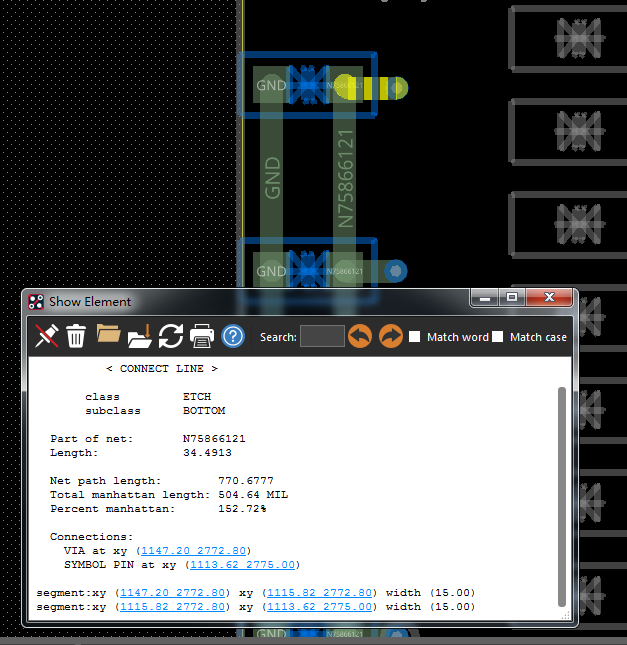

1.外壳地到GND分割要2mm以上距离2.跨接电容这边外壳地附近要和gnd打一样多的过孔3.多处孤岛铜皮和尖岬铜皮4.走线不完全连接,走线要连接到焊盘中间出线5.过孔上焊盘,过孔尽量和附近过孔对齐,走线要从焊盘中心出线6.tx、rx等长组缺

在PCB设计过程中,若是在电源平面或地平面的分割处理不当,很容易导致平面的不完整,信号走线时,其参考平面将出现在一个电源面跨接到另一个电源面,这种现象叫做信号跨分割。跨分割对低速信号影响不大,但在高速数字信号系统重影响很大,所以电子工程师该

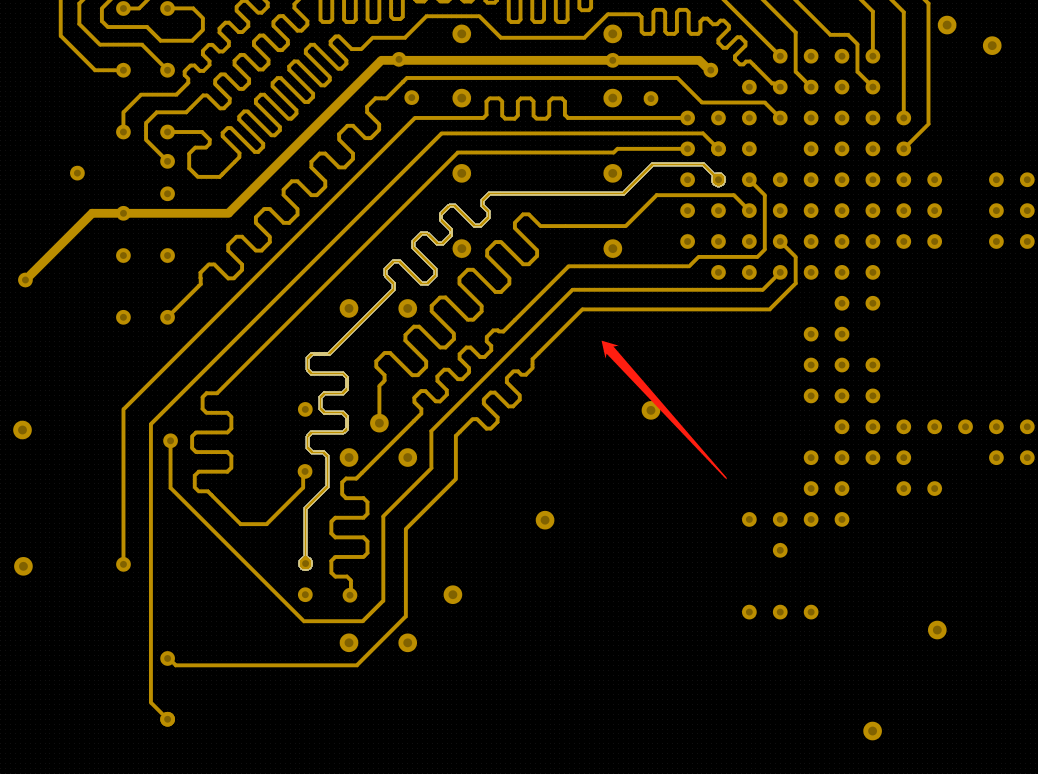

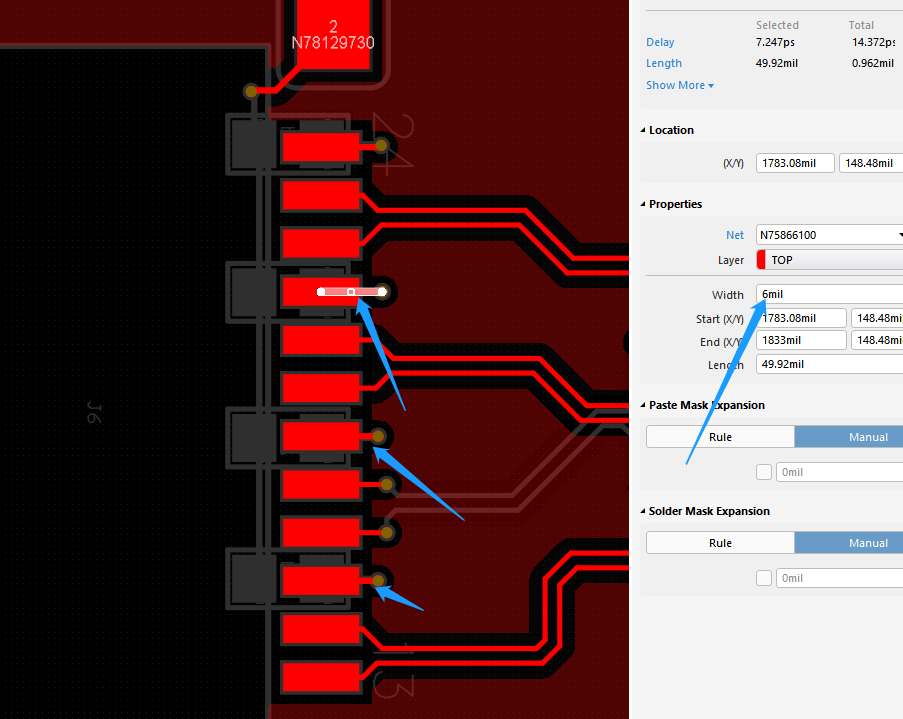

下面这一组数据线尽量还可以稍微紧凑点:等长可以咬合等长,比较节省空间并且也比较美观:平面分割的分割带建议宽度20MIL:其他的没什么问题,等长尽量可以紧凑并且美观点。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训

DDR3 2片:电感内部挖空处理。注意电源铺铜不要出现这种瓶颈处:等长线注意要保证3W间距,去调整出来:数据线需要满足等长误差,还存在报错:数据线也要满足3W间距自己注意走线跟过孔的间距规则:分割带尽量大于20MIL:以上评审报告来源于凡亿

变压器上除了差分信号,其他的加粗20MIL走线:晶振尽量包地处理:RX TX以及差分组内等长没啥问题:建议机壳地与电路地之间分割2MM间距:其他的没什么问题。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可

网口除差分信号外,其他信号都需要加粗到20mil2.注意网口的地分割,跨接器件旁要多打地过孔,分割间距2mm后期自己处理一下3.差分出线需要优化一下,器件可以摆放远一点,包地的线要需要均匀打上过孔4.注意差分信号需要按照阻抗线距进行走线晶振

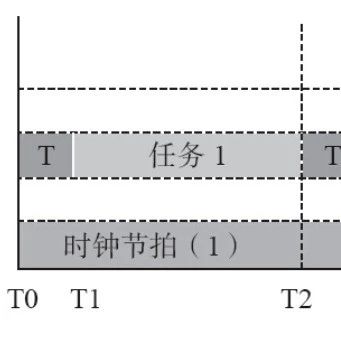

任务A和任务B按照等长时间轮流占用处理器,在单处理器上造成多个任务同时运行的假象。这里先聊一聊多任务系统架构的分割时间段。将处理器运行时间分成小的时间段指明了把处理器时间以多大的频率分割成固定长度的时间片段,也叫做多任务系统架构的时钟节拍。作为多任务系统运行的时间尺度,时钟节拍是通过特定的硬件定时器

元器件能水平以及垂直方向放置,不要45度:不要有这种尖岬铜皮:机壳地与电路地至少满足2MM间距:差分对内等长注意参数长度值,gap需要大于等于3W:跨接器件两端都可多打地过孔:平面分割带建议加粗到20MIL:存在长度误差报错:以上评审报告来

扫码关注

扫码关注