- 全部

- 默认排序

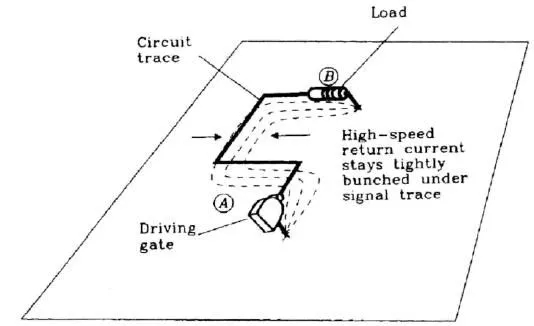

任何注入到系统中的电流最终都要回到源端。因此,信号不仅仅是在信号线上传播,同时也是在参考平面上传播,如下图所示。所以保持参考平面的完整和低阻抗,与保持信号线的完整和低阻抗对系统同样重要。

PCB设计信号等长分析

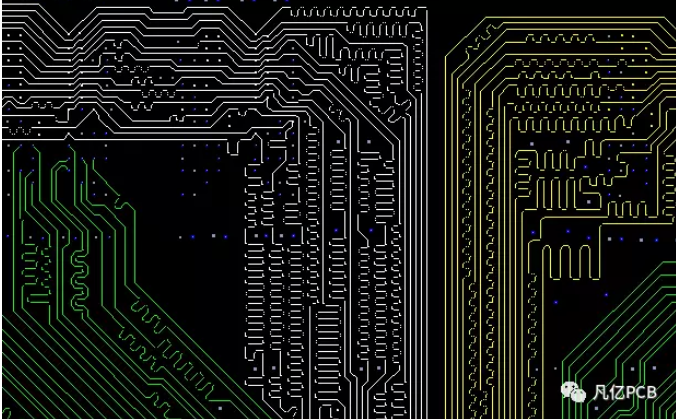

在做PCB设计时,为了满足某一组所有信号线的总长度满足在一个公差范围内,通常要使用蛇形走线将总长度较短的信号线绕到与组内最长的信号线长度公差范围内,这个用蛇形走线绕长信号线的处理过程,就是我们俗称的PCB信号等长处理。

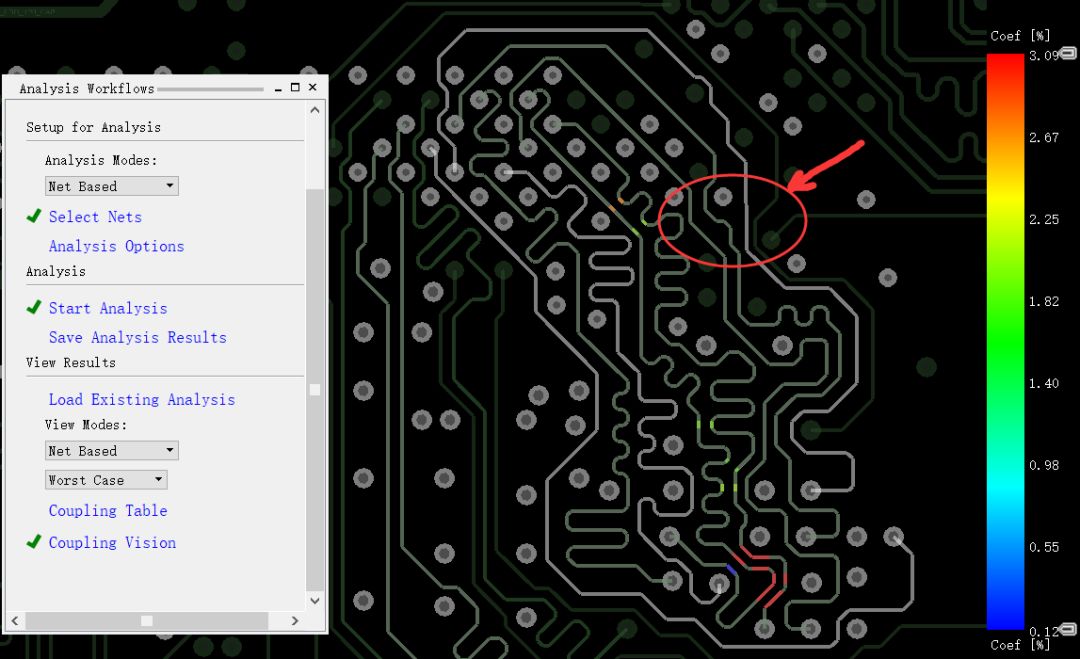

串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。 PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。下面是在SigXplorer里面搭建了一个串扰的仿真链路,黄色部分就是得到的信号之间的串扰分析结果。

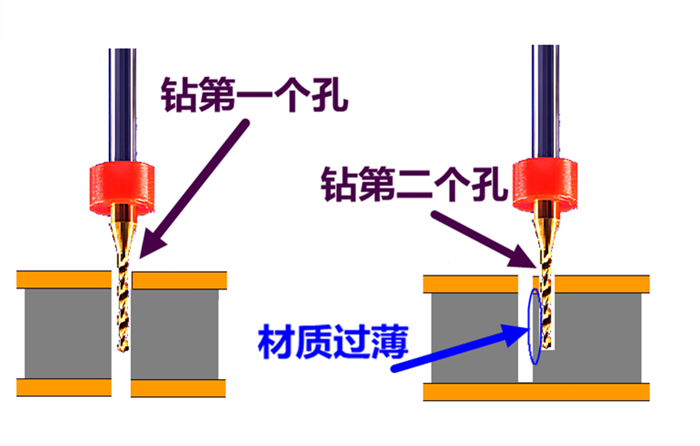

PCB板设计时,我们布线考虑最多的,是如何把各个层同网络信号线用最合理的方式连接,高速PCB板线路越密集过孔(VIA)放置的密度就越大,过孔能起到各层间电气连接的作用。多层线路板PCB打样经常会收到板厂反馈“孔到线过近,超出了制程能力”,那么过孔过近对生产会有什么难点,对产品可靠性又有什么影响呢?

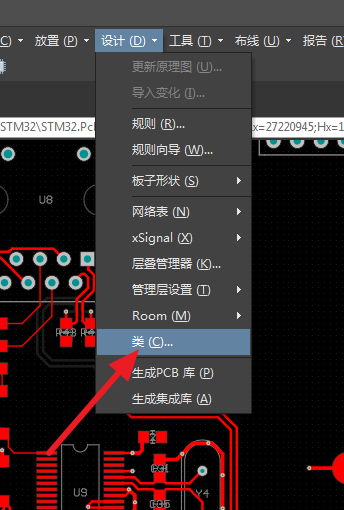

我们在进行PCB设计的时候,一个PCB板上的信号线,电源线,地线等等太多了。那我们给它分成一类一类的,就是我们常说的在Class中创建的类了。

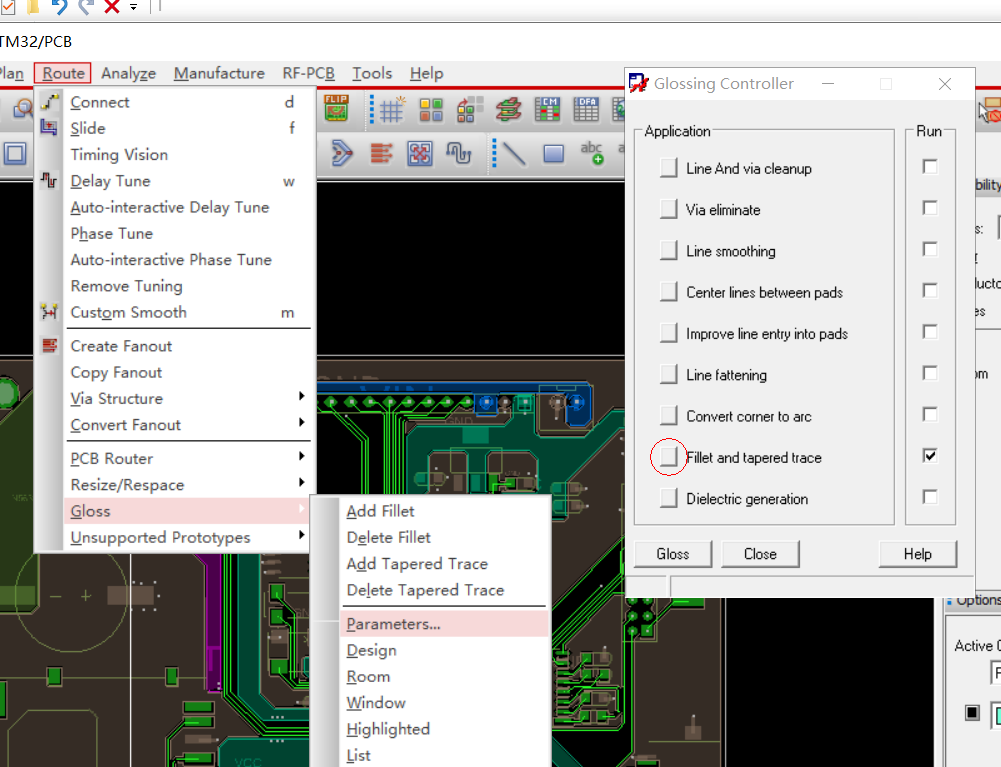

通常添加泪滴的目的是:增加线与过孔和焊盘的连接强度,提高DFM(可制造性);减少引脚、过孔与信号线的宽度变化造成阻抗突变而带来的反射等信号完整性的问题。

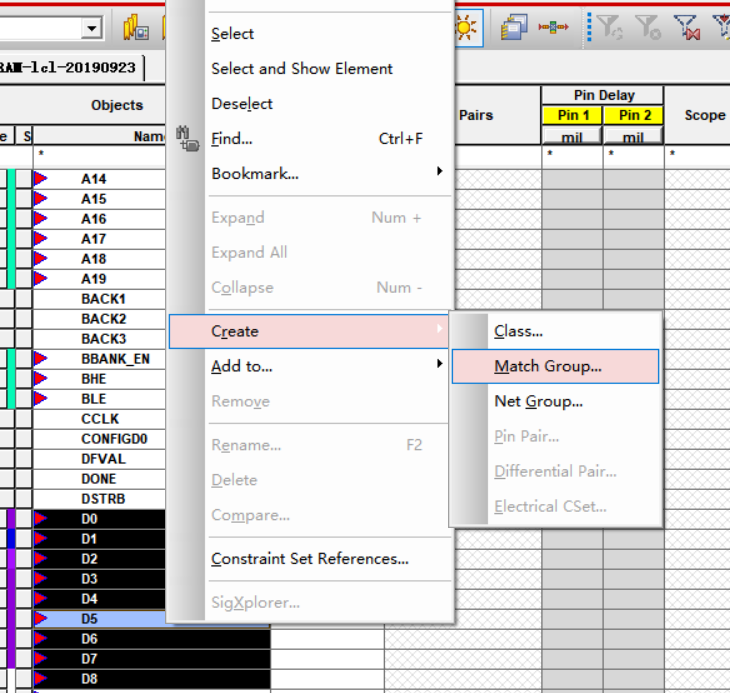

SDRAM信号线等长处理

在布线完成后,这里以SDRAM为例,要对SDRAM信号线进行等长处理,以满足时序要求。SDRAM的信号可分为数据线、地址线、控制线、时钟线,走线时要同组同层,间距满足3W原则,每组数据线的等长误差范围为+-50mil,地址线、控制线、时钟线的等长误差范围为+-100mil。

物理约束规则介绍

物理规则包括设置线宽和指定过孔库等的属性规则,在设置规则之前,需要把层叠等参数设置好。默认的为default规则。Default规则是指铺铜的单线50Ω阻抗的信号线规则

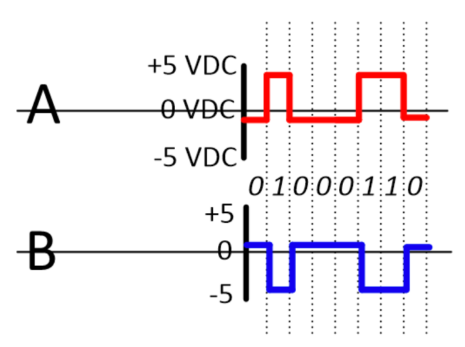

RS485作为常见的总线之一,几乎每个工控设备都在用,我们也对其熟悉不过了。我们都知道RS485双半双工通信,其CPU内部的根源是串口通信,串口通信是区分发送TX和接收RX的,在同一对差分信号线上同时传输TX、RX,就是进行方向的控制,方向的控制时机不对,数据传送是要出问题的。

扫码关注

扫码关注