- 全部

- 默认排序

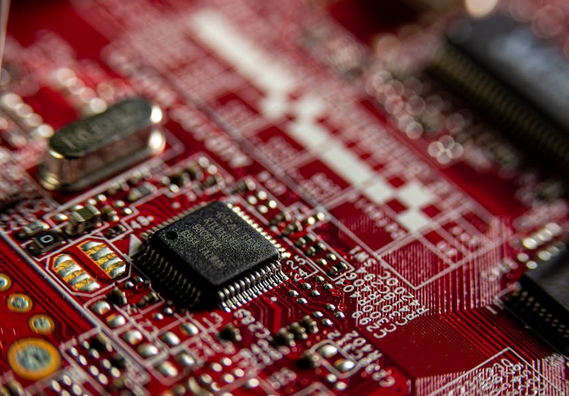

在电磁兼容性设计中,信号反射是电子工程师的重要考虑因素之一,特别是在高速数字系统中,信号反射可导致多种问题,如过冲、下冲和振铃,针对这些问题如何分析,并制作相关的电路设计?首先,这些问题的发生,原因在于是由信号在传输线上传播时遇到阻抗不匹配

在电子工程中,很多电子小白会发现高速电路大都会配备电阻端接技术,以此解决信号反射、振铃等信号失真现象,这是为什么?能不能跳过这个操作?一般来说,高速电路中的信号传输速度非常快,相比其他电路,阻抗不连续性问题更加严重,当信号在传输过程中遇到阻

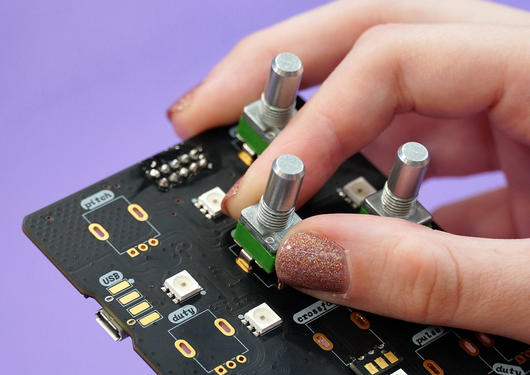

大家如果做过DDR的设计可能会发现在进行多片DDR连线时,通常在信号的末端会放置很多的电阻(如下图所示),那么这些电阻都是起什么作用的呢?通常在DDR末端的电阻是为了防止信号反射的,起阻抗匹配的作用,之前我们介绍过另一种防止信号反射的解决措

在PCB布局布线过程中,工程师经常面临着走线宽度变化的问题,由于布线空间的限制,可能会使用更新或更粗的线条来通过某些区域,但这种变化会导致阻抗不匹配,最终信号反射,对整体电路产生负面影响,因此会有哪些问题?一般来说,走线宽度会导致阻抗不匹配

我们为什么需要电路端接?

在电子电路设计中,端接技术是重要的学习内容,因为电路中的阻抗不连续很容易导致信号反射,进而引发信号失真问题,严重影响通信质量,所以端接技术派上用场了。1、信号反射与阻抗不配在电路设计中,端接技术扮演着至关重要的角色。其根本原因在于,电路中的

在高速PCB设计中,阻抗控制是确保信号完整性和系统性能的关键因素,阻抗不匹配可能导致信号反射、衰减和失真,进而影响系统的稳定性和可靠性。如果关注一些技术参数,可以避免阻抗大小变化!1、线宽(Track Width)线宽是影响阻抗的直接因素。

高频PCB设计概要之二

1、射频电路的布局和连接尽可能地短由于传输线拐角处的阻抗突变会造成信号反射,高频信号将作为电磁场能量辐射到空间中。结果,经“拐角”之后的信号电平值可能下降。因此,在设计高频电路时,必须精心设计RF布局以使得RF走线拐角角度尽可能的小。设计RF电路时,如果板上有足够的空间,则将RF相关元器件布置成尽可

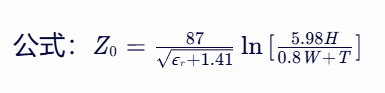

在高速电路设计与射频工程领域,特性阻抗是确保信号完整性和减少信号反射的关键因素,而微带线与带状线作为PCB设计中两种常用的传输线结构,其特性阻抗的计算非常重要,本文将列出这两种传输线的特性阻抗计算公式,希望对小伙伴们有所帮助。1、微带线特性

在高速PCB设计中,确保信号完整性是至关重要,而地过孔的布置,可以减少信号反射、串扰和电磁干扰(EMI),特别是在高速信号孔旁。合理的地过孔数量可显著改善信号质量,那么应该增加几个?1、最少数量对于高速信号(如频率超过1GHz),建议在信号

在高速射频电路设计中,可能会遇见阻抗不连续问题,若是不能及时处理,它可能导致信号反射、损耗增加及整体性能下降,那么如何解决?1、渐变线设计在RF信号线宽度变化处使用渐变线,避免线宽突变。渐变线过渡部分的长度应适中,不宜过长。2、拐角处理对R

扫码关注

扫码关注