- 全部

- 默认排序

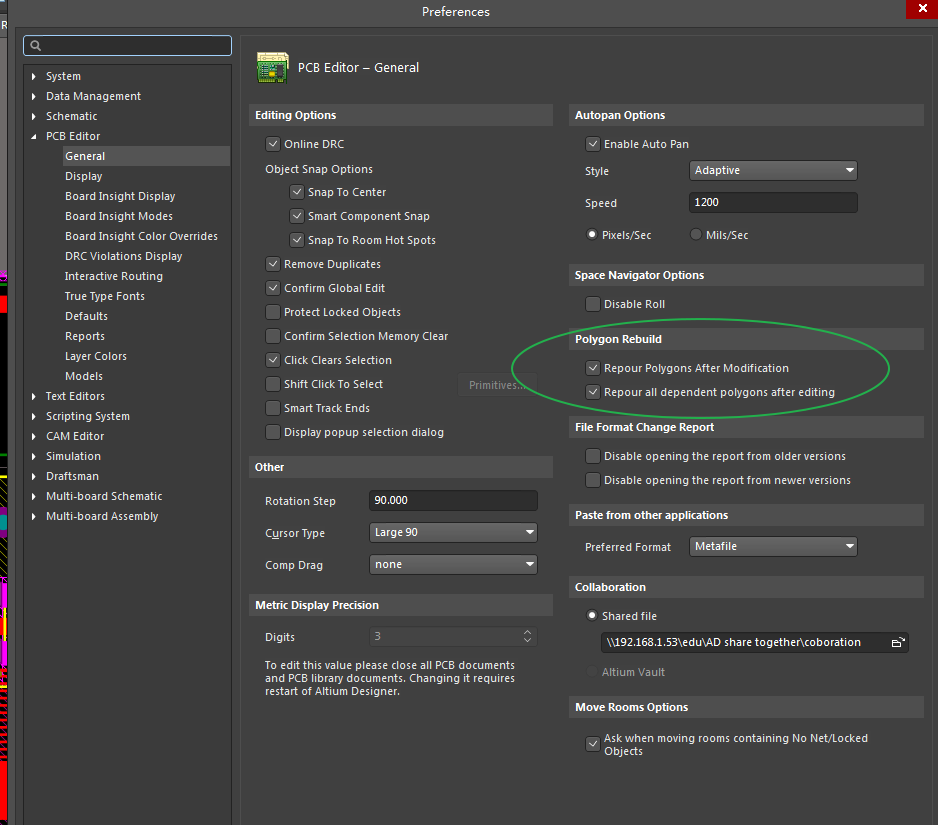

本视频讲解使用Altium designer19 ,主要和大家一起认识铜皮管理器的界面,铜皮灌铜的操作注意事项,实时铜皮的操作的使能的好处和缺点,以及如何来提高我们的灌铜的效率的一个操作演示。

电源设计调试及故障排查

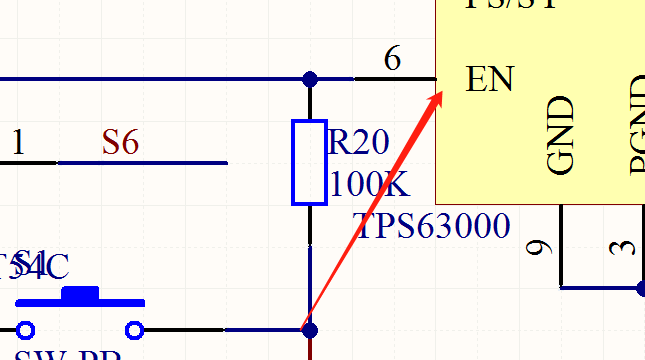

(1)对于采用电池供电的手持设备,系统的电源芯片一般采用效率较高、电压转换灵活的DC-DC(直流-直流)开关电源IC来实现,但是DC-DC开关电源的IC往往存在调试麻烦的问题,这些问题的可以归结为以下几类:1)输出电压基本为0;2)输出电压基本等于输入电压;3)输出电压与设计中预设值偏离较大,这个针对输出可调的DC-DC芯片而言的;4)输出电压正常,但是片子(含除电源外的其他IC)发热严重。输出电压基本为0的时候,首先要检查该电源IC使能脚是否接对是不是高电平,可以用万用表测一下该引脚的电压,若

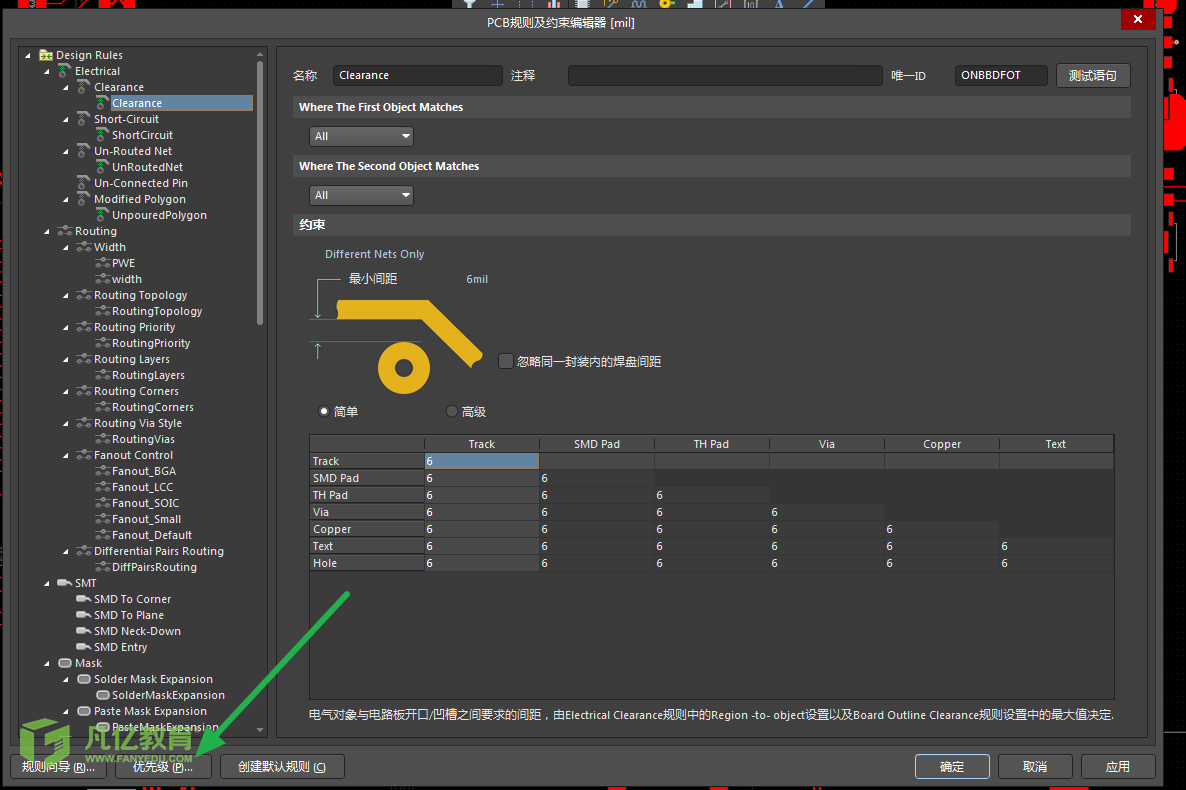

我们平时去设计pcb的时候,布局完就是要进行布线了。那么,布线的前提就是需要去规则编辑器里面去设置对应的走线规则或者是间距规则等等的规则。

高版本中,我们进行动态铜皮的自动更新,那么如何进行设计,如果想实现自动在铜皮里面进行铜皮避让,首先你的电脑必须是高配置,不然有可能就会出现铜皮自动避让,从而出现卡机的现象。

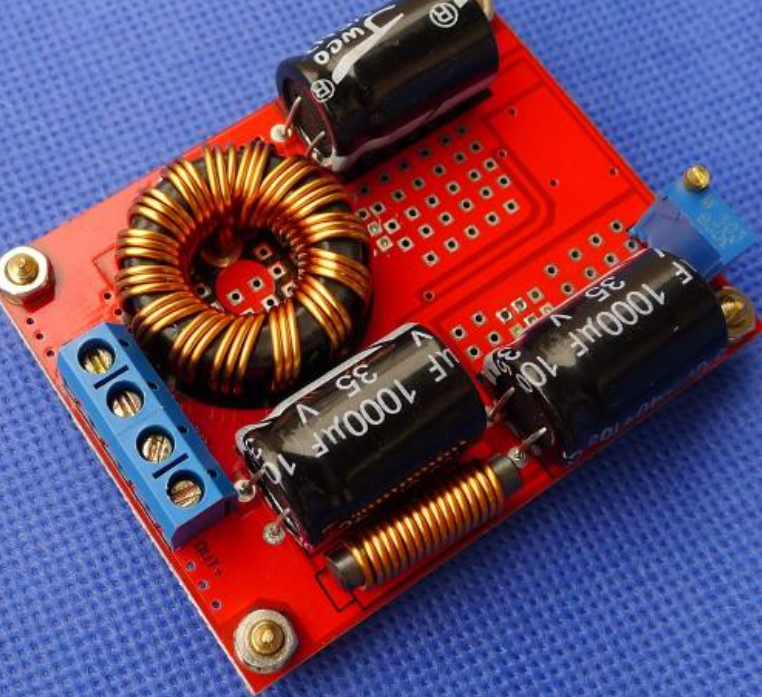

PCB设计教程之电源PCB设计教程的详细资料分析各位电子工程师想必都知道,设计时,PCB设计占据很重要的地位。以电源为例,PCB设计会直接影响电源的EMC性能、输出噪声、抗干扰能力,甚至是基本功能。电源部分的PCB布线与其他硬件稍有不同,该如何设计?本文为你揭秘。对于高电压产品必须要考虑到线间距。能满足相应安规要求的间距当然最好,但很多时候对于不需要认证,或没法满足认证的产品,间距就由经验决定了。多宽的间距合适?必须考虑生产能否保证板面清洁、环境湿度、其他污染等情况如何。对于市电输入,即使能保证

SDRAM芯片引脚介绍

以 Micron公司容量为512Mb(512兆位),规格为8M×16×4的某款 SDRAM为例,介绍 SDRAM的引脚定义。(1) CLK:时钟信号,为输入信号。 SDRAM所有输入信号的逻辑状态都需通过CLK的上升沿采样确定。(2) (2)CKE:时钟使能信号,为输入信号,高电平有效。CKE信号的用途有两个,其是关闭时钟以进入省电模式,其二是进入自刷新( SELF REFRESH)状态。CKE无效时,SDRAM内部所有与输入相关的功能模块停止工作。在电路设计中需注意,应为C

ADM2582E/ADM2587E是具备±15 kV ESD保护功能的完全集成式隔离数据收发器,适合用于多点传输线路上的高速通信应用。其内部集成的RS-485驱动器带有一个高电平有效使能电路。

AP8851 一款宽电压范围降压型DC-DC 电源管理芯片,内部集成使能开关控制、基准电源、误差放大器、过热保护、限流保护、短路保护等功能,非常适合在宽输入电压范围具有优良的负载和线性调整度。AP8851 芯片包含每周期的峰值限流、软启动、

STM32F1系列单片机有多种外设,外设配置方式比较一致,一般是使能外设所在GPIO口时钟、使能外设的时钟,在禁止外设的情况下配置外设的时序以及中断和DMA等。大部分的外设配置相对简单,但是FSMC接口因为配置比较复杂,往往让一些初学者一头雾水。本文记录了本人在STM32F103ZET6的FSMC接

扫码关注

扫码关注