- 全部

- 默认排序

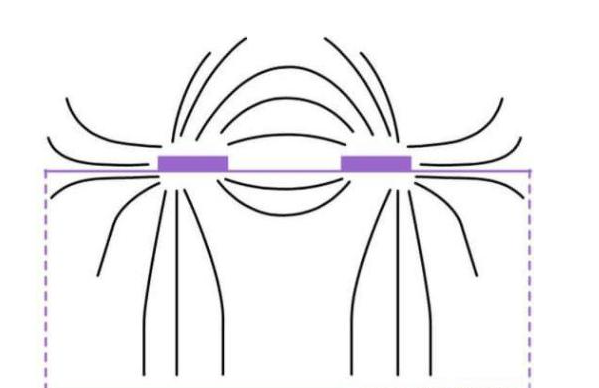

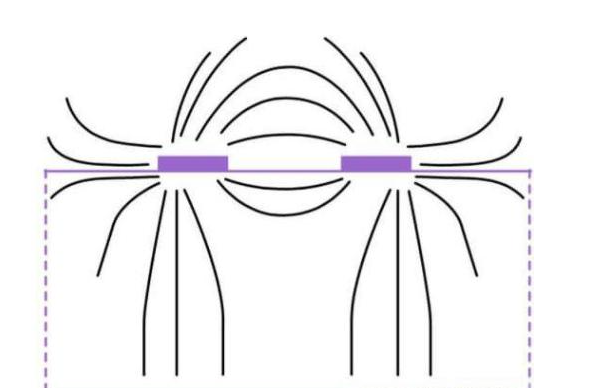

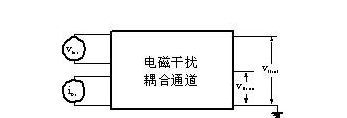

答:串扰,就是指一条线上的能量耦合到其他传输线,它是由不同结构引起的电磁场在同一区域里的相互作用而产生的。串扰在数字电路中非常普遍地存在着,如芯片内部、PCB板、接插件、芯片封装,以及通信电缆等等。 串扰可能是数据进行高速传输中最重要的一个影响因素了。它是一个信号对另外一个信号耦合所产生的一种不受欢迎的能量值。根据麦克斯韦定律,只要有电流的存在,就会有磁场存在,磁场之间的干扰就是串扰的来源。这个感应信号可能会导致数据传输的丢失和传输错误。 所以串扰对

答:降低串扰的方法有如下几种:增加信号路径之间的间距、用平面作为返回路径、使耦合长度尽量短、在带状线层布线、减小信号路径的特性阻抗、使用介电常数较低的叠层、在封装和接插件中不要共用返回引脚、使用两端和整条线上有短路过孔的防护布线,更多关于PCB中降低串扰的处理方法,可以到本书学习论坛“PCB联盟网”免费下载学习。

答:我们PCB中的信号都是阻抗线,是有参考的平面层。但是由于PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样,信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。跨分割的现象如图1-52所示。跨分割,对于低速信号,可能没有什么关系,但是在高速数字信号系统中,高速信号是以参考平面作为返回路径,就是回流路径。当参考平面不完整的时候,会出现如下影响:Ø 会导致走线的的阻抗不连续;Ø 容易使信号之间发生串扰;Ø

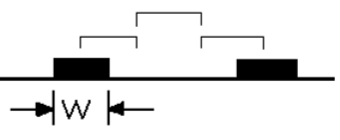

答:为了信号走线的质量,不产生串扰,我们保持信号走线与信号走线之间的间距为3倍线宽,这个间距指的是走线的中心到中心的间距,因为我们的线宽英文是width,所以这个规则我们通常就叫做3W原则。

答:串扰,就是指一条线上的能量耦合到其他传输线,它是由不同结构引起的电磁场在同一区域里的相互作用而产生的。串扰在数字电路中非常普遍地存在着,如芯片内部、PCB板、接插件、芯片封装,以及通信电缆等等。

答:互感是引起串扰的两个重要因素之一,互感系数标志了一根驱动传输线通过磁场对另外一根传输线产生感应电流的程度。

高速信号是否需要包地处理

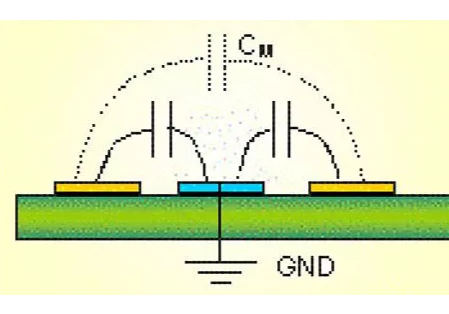

首先,我们要明确为什么要包地?包地的作用是什么?实际上,包地的作用就是为了减小串扰,串扰形成的机理是有害信号从一个线网转移到相邻线网而串扰在PCB上是由不同网络之间因较长的平行布线引起的相互干扰,主要是由于平行线间的分布电容和分布电感的作用

分享一篇不错的文章1、什么是地弹1.1、地弹的概念地弹、振铃、串扰、信号反射······这几个在信号完整性分析总是分析的重点对象。初学者一看:好高深!其实,感觉高深是因为你满天听到“地弹”二字,却到处找不到“地弹的真正原理”。如果你认真读笔

一个layout工程师学习信号完整性之路串扰还是比较复杂的一个东西,在工作中好多人询问串扰仿真怎么分析,其实对于仿真流程相对简单,但是真正利用这个仿真去做优化的相对较少,所以还是要理解其中的原理,在layout中去设计,比如常说的3W等,也

扫码关注

扫码关注