一个layout工程师学习信号完整性之路

串扰还是比较复杂的一个东西,在工作中好多人询问串扰仿真怎么分析,其实对于仿真流程相对简单,但是真正利用这个仿真去做优化的相对较少,所以还是要理解其中的原理,在layout中去设计,比如常说的3W等,也可以通过整体的时域仿真或者眼图来整体分析信号的质量。下面简单整理一下串扰常用的知识:

一、串扰的概念

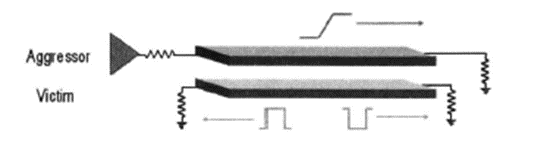

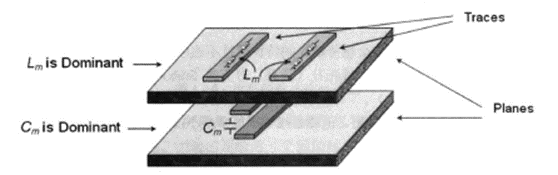

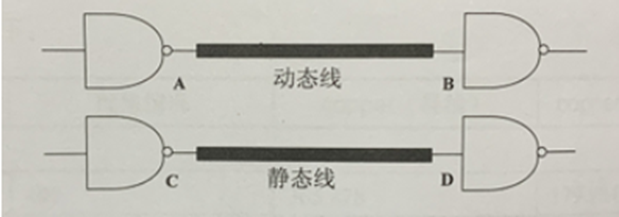

1.串扰是两条信号线之间的耦合、信号之间的互感和互容引起的。当信号在传输线上传播时,相邻信号线之间由于电磁场的相互耦合会产生不期望的噪声电压信号,即能量由一条线耦合到另一条线上。根据耦合的机理不同,可分为电感应(容性)耦合和磁感应(感性)耦合。产生串扰(crosstalk)的信号被称为干扰源(Aggressor)或动态线(active line),而收到干扰的信号被称为被干扰对象(Victim)或静态线(passive line)。通常,一个网络既是干扰源又是被干扰对象。

2.串扰是发生在一个网络的信号路径及返回路径和另一个网络的信号路径及返回路径之间的一种效应。

3.耦合机制:动态线上的电压变化可在周围产生电场,而电场对于处于其中的导体上的电荷流动有一定的影响,因此与静态线相互作用后就会出现容性(电感应)耦合。动态线上的电流变化将会在导体周围产生磁场,而这个磁场会对处于其中的电荷移动产生影响,从而使静态线上出现感性(磁感应)耦合。

4.耦合并不是时时刻刻发生的,本人经过咨询和查找资料,了解如下:

当信号沿着动态线传播时,仅在信号边沿附近的特殊区域,即存在dV/dt或dI/dt的区域,才有耦合电流流到静态线上。导线上除此之外的任何地方,电流和电压都为常数,所以不会出现耦合噪声电流。这个地方还希望各路大神指教!!!

二、近端串扰和远端串扰

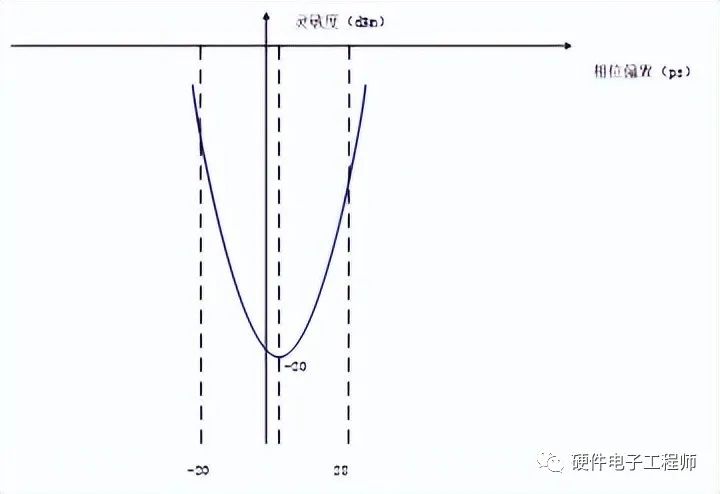

1.对于长线的耦合串扰,在静态线上两端测得噪声电压明显不同,为了区分这两端,把距离干扰源端最近的一端称为近端干扰(信号传输方向的后方),距离干扰源端最远的一端称为远端干扰(信号传输的前方)。大家看到的两种串扰的峰值不一样是因为近端串扰是连续值,远端串扰是叠加值。近端串扰和线间距有关,远端串扰和线间距还有走线的并行长度有关。(互容和间距有关,互感和并行长度有关,)

近端噪声与容性耦合电流和感性耦合电流的总和有关。远端噪声与容性耦合电流和感性耦合电流的差有关。

三、影响串扰的因素

1.线间距:串扰随着间距的增大而降低,粗略估算间距从一倍间距拉远到两倍间距串扰降一半,拉远到三倍串扰再降一半。

2.介电常数:使用低介电常数材料时,为了保证特性阻抗不变而相应采用更小的介质厚度,这样减小了近端串扰和远端串扰。

3.阻抗:当两端都不匹配时,使得两端串扰均反射到另一端,相互干扰。即:干扰波形是串扰和反射的叠加。根据端阻抗与传输线特性阻抗的关系决定反射幅值和极性,多次反射后幅值渐小至稳定。

四、减小串扰的方法:

1.布线时尽可能增加线的间距,减小线的平行长度,从而减小串扰。

2.高速信号线在满足先前条件下,正确的源端端接可以减小或消除反射,从而减小串扰。

3.对于带状线和微带线尽量减小走线到地平面的距离,从而减小串扰。

4.层叠设计时,尽量使用电源平面或地平面来隔离两个信号层,如果两个信号层不得相邻,采用垂直布线。

5.在串扰较严重的两条线之间插入一条地线,可以起到隔离的作用,从而减小串扰。

6.尽量避免电源和地平面的分割。

7.用差分线来传输关键的高速信号。

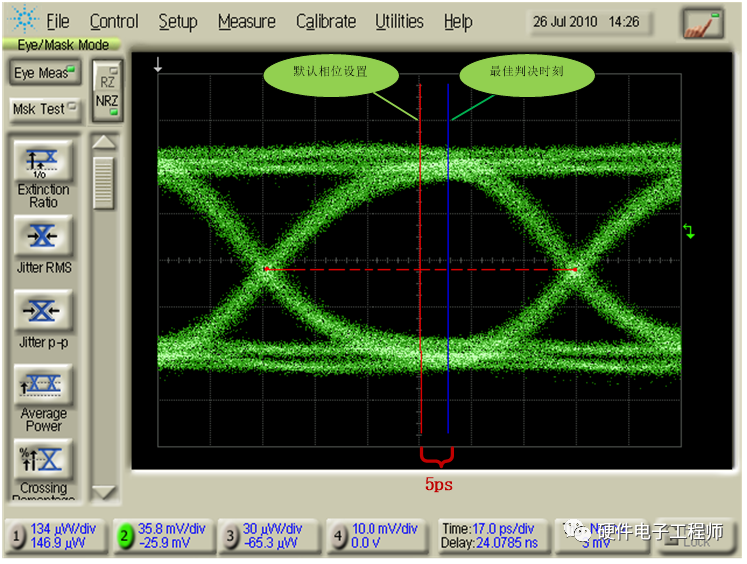

五、仿真数据

下面是本人自己的串扰仿真数据,大家有兴趣的可以看下哈:

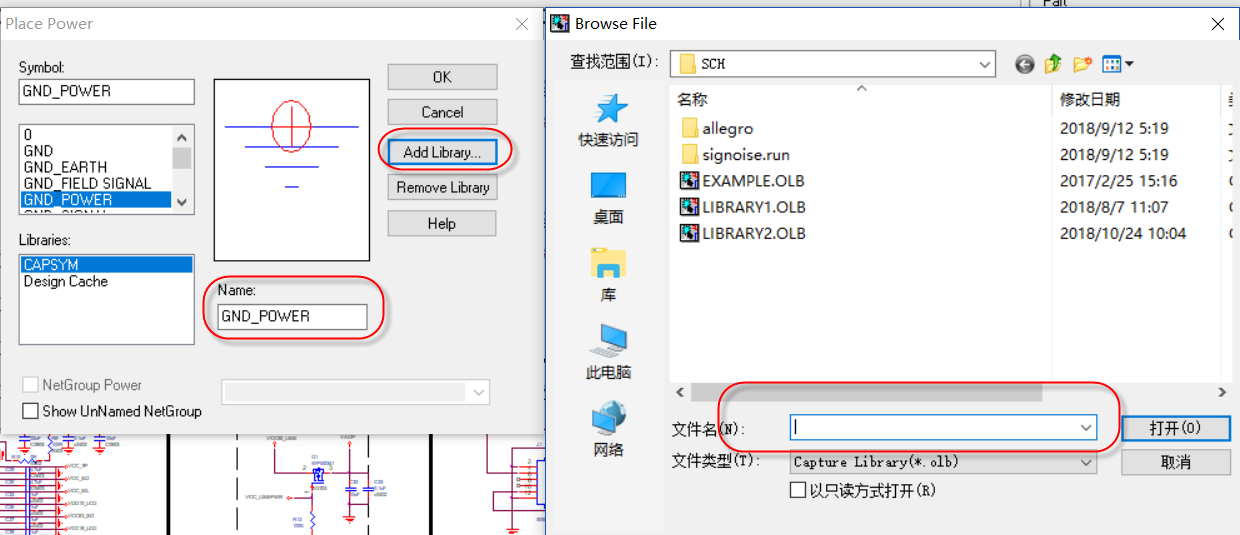

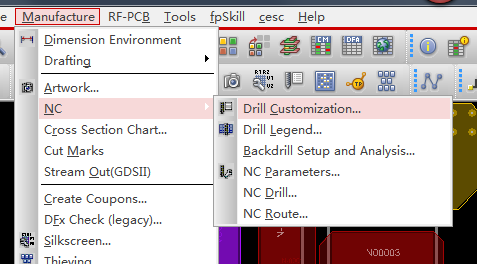

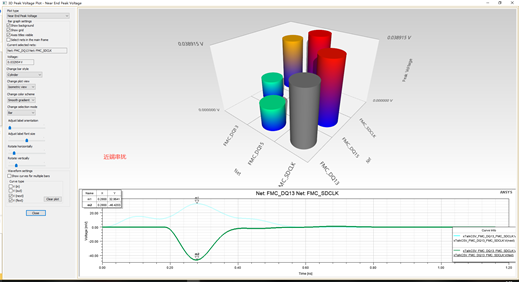

1.Anasys SIwave 仿真的近端串扰与远端串扰:

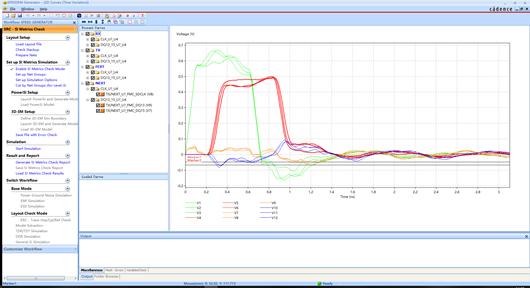

2.Cadence Sigrity SPEED2000 仿真的近端串扰与远端串扰:

以上资料主要参考《Cadence 高速电路设计》、《ANSYS信号完整性分析与仿真实例》

如有雷同或错误,希望各位大神留言指正,感谢!!!

扫码关注

扫码关注