- 全部

- 默认排序

快速边沿脉冲发生器,上升时间快至 350 皮秒。发生器输出信号的峰峰值为15V左右,频率在200kHz左右。绝大多数示波器的采样率在超过 1GHz 带宽时,可测量的电压范围在10V以内,所以当示波器带宽超过 1GHz 时需要配合衰减器使用。

SDRAM芯片引脚介绍

以 Micron公司容量为512Mb(512兆位),规格为8M×16×4的某款 SDRAM为例,介绍 SDRAM的引脚定义。(1) CLK:时钟信号,为输入信号。 SDRAM所有输入信号的逻辑状态都需通过CLK的上升沿采样确定。(2) (2)CKE:时钟使能信号,为输入信号,高电平有效。CKE信号的用途有两个,其是关闭时钟以进入省电模式,其二是进入自刷新( SELF REFRESH)状态。CKE无效时,SDRAM内部所有与输入相关的功能模块停止工作。在电路设计中需注意,应为C

随着信号上升沿时间的减小及信号频率的提高,电子产品的EMI问题越来越受到电子工程师的关注,几乎60%的EMI问题都可以通过高速PCB来解决。以下是九大规则:

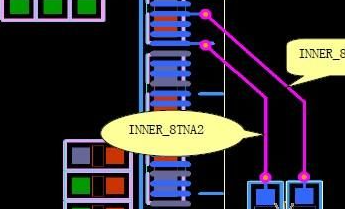

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长走线的目的就是为了尽可能的减少所有相关信号在PCB上的传输延迟的差异。高速信号有效的建立保持窗口比较小,要让数据和控制信号都落在有效窗口内,数据、时钟或数

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。

同步电路是数字电路中常见的电路设计方法之一,但部分小白对该类电路不甚了解,甚至遇见该类设计是惘然无措,所以本文将重点分析同步电路的设计准则,并分享电路设计的优点。同步电路是指所有电路在同一个公共时钟的上升沿或下降沿的触发下同步地工作。但在实

通孔在连接多层PCB的不同层上的走线方面起着导体的作用(印刷电路板)。在低频情况下,过孔不会影响信号传输。但是,随着频率的升高(高于1 GHz)和信号的上升沿变得陡峭(最多1ns),过孔不能简单地视为电连接的函数,而是必须仔细考虑过孔对信号完整性的影响。通孔表现为传输线上阻抗不连续的断点,导致信号反

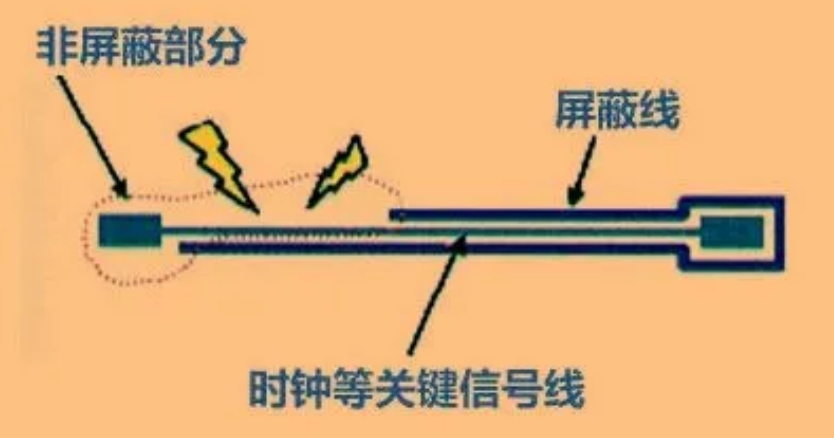

随着信号上升沿时间的减小,信号频率的提高,电子产品的EMI问题,也来越受到电子工程师的重视。高速pcb设计的成功,对EMI的贡献越来越受到重视,几乎60%的EMI问题可以通过高速PCB来控制解决。1高速信号走线屏蔽规则如上图所示:在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果

RGMII接口是MAC和PHY之间常用的千兆网通信接口,采用4bit数据接口,工作时钟为125Mhz,并且上升沿和下降沿同时传输数据,因此传输速率可达1000Mbps。RK3588芯片拥有2个GMAC控制器,提供RMII或RGMII接口连接

关于滤波电容、去耦电容、旁路电容作用及其原理从电路来说,总是存在驱动的源和被驱动的负载。如果负载电容比较大,驱动电路要把电容充电、放电,才能完成信号的跳变,在上升沿比较陡峭的时候,电流比较大,这样驱动的电流就会吸收很大的电源电流,由于电路中的电感,电阻(特别是芯片管脚上的电感,会产生反弹),这种电流

扫码关注

扫码关注