- 全部

- 默认排序

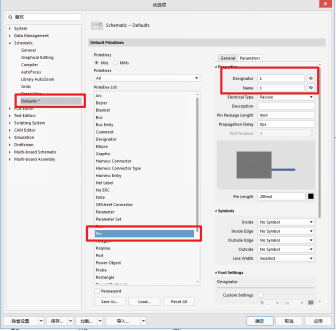

答:这个功能对于很多初学者都不是很清楚,有些同学可能因为之前随意放置过几个PIN管脚,导致后来放置管脚的时候,管脚编号不是从1开始的,这样就会造成很多的疑问。 1)双击管脚,进入属性里面修改管脚编号可以完成编号的更改。但此种方法,治标不治本,下次再放置管教时,还是不会从修改以后的管脚编号开始。

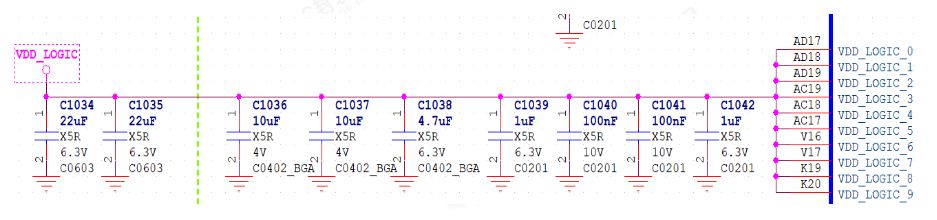

RK3588 VDD_LOGIC电源PCB设计1、VDD_LOGIC的覆铜宽度需满足芯片的电流需求,连接到芯片电源管脚的覆铜足够宽,路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源pin脚路径都足够。2、如图1所示,原理

1、VDD_NPU的覆铜宽度需满足芯片的电流需求,连接到芯片电源管脚的覆铜足够宽,路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源pin脚的路径都足够。2、VDD_NPU的电源在外围换层时,要尽可能的多打电源过孔(7个以

RK3588 VDD_CPU_LIT电源PCB设计1、VDD_CPU_LIT覆铜宽度需满足芯片电流需求,连接到芯片电源管脚的覆铜足够宽,路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源pin脚的路径都足够。2、VDD_C

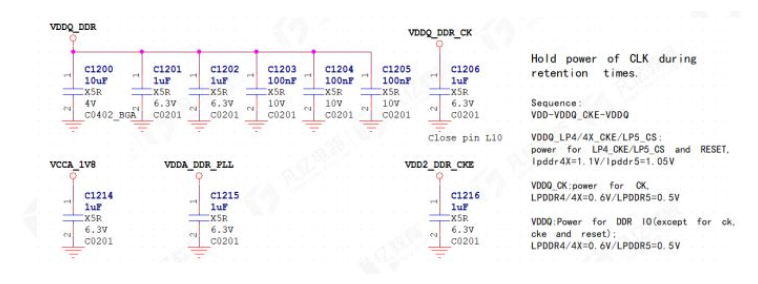

RK3588 VCC_DDR电源PCB设计1、VCC_DDR覆铜宽度需满足芯片的电流需求,连接到芯片电源管脚的覆铜足够宽,路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源pin脚的路径都足够。2、VCC_DDR的电源在外

许多电子工程师会选择Cadence Allegro来设计PCB,在使用时会遇到许多操作,其中之一是在Cadence环境中创建封装库,确保数据的高效与准确,那么在操作Cadence时需要注意什么?1、精确测量与缩放Pad尺寸根据pin脚的精确

有人知道原理图中元件这里pinlock都勾上了,然后在原理图编辑时,选中pin脚还是可以移动的有人知道原理图中元件这里pinlock都勾上了,然后在原理图编辑时,选中pin脚还是可以移动的这是为啥AD17版本

扫码关注

扫码关注