- 全部

- 默认排序

组合逻辑电路设计,在任何特定时间只能在输入的时间取决于输出,电路的原始状态无关。“也就是说,组合逻辑电路输出电路的历史地位并不重要,电路不包括存储单元。组合逻辑表达方法有三种:真值表,逻辑表达式和电路原理图。在VERILOGHDL描述组合逻辑电路中,与真值表对应的是用户自定义原语;而与电路原理图相对应的是门级建模,有个绰号又叫结构化描述;与逻辑表达式相对应的则称为行为描述。

1 FPGA学习重点1. 看代码,建模型只有在脑海中建立了一个个逻辑模型,理解FPGA内部逻辑结构实现的基础,才能明白为什么写VERILOG和写C整体思路是不一样的,才能理解顺序执行语言和并行执行语言的设计方法上的差异。在看到一段简单程序的

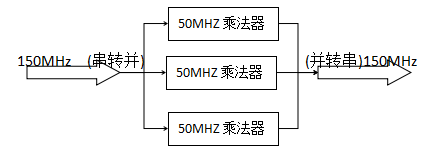

对于FPGA工程师来说,RTL设计是常见的FPGA必不可少的设计环节,但对于小白来说,很多小白不懂RTL设计,甚至数次在FPGA或RTL设计常走歪路,所以本文将详谈RTL设计。1、使用VERILOG进行RTL设计使用VERILOG进行RTL

最近,由美国OpenAI研发的聊天机器人ChatGPT着实火了一把。“会被人工智能替代的行业”、“不是孩子未来的发展方向“等等话题层出不穷,ChatGPT成为新的流量收割机,引发了网友的一系列“花式整活”。那么,当ChatGPT遇到FPGA,会怎样?例如,如何用VERILOG HDL语言写一

一、逻辑设计(1)组合逻辑设计下面是一些用VERILOG进行组合逻辑设计时的一些注意事项:①组合逻辑可以得到两种常用的RTL 级描述方式。第一种是always 模块的触发事件为电平敏感信号列表;第二种就是用assign 关键字描述的数据流赋值语句。②always 模块的敏感表为电平敏感信号的电路可几

一直以来,有很多人询问数字芯片验证行情如何?发展如何,然后也有不少回答,基本上都是正向的:薪资高、机会多、发展好。有位大佬表示:做验证更锻炼整体思维,更能全面的接触到系统设计需求。做验证学习的知识通用性更广,和具体应用领域的知识关联不那么紧

在VERILOG仿真和调试过程中,信息的显示和输出是不可或缺的环节,而$display和$write是两个常用的系统任务,用于在仿真过程中输出信息,尽管它们二者的功能相似,但在实际使用中仍有很大的差别。1、换行行为$display:在输出信

VERILOG,作为底层汇编语言之一,一直以来是许多开发人员的必学编程语言之一,要想硬件设计优秀,做到功能的正确实现,就必须写好高质量的VERILOG代码,那么如何确保自己的VERILOG代码是优秀的?1、标准化设计确保模块设计符合协议标准

扫码关注

扫码关注