- 全部

- 默认排序

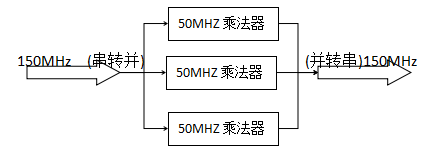

组合逻辑电路设计,在任何特定时间只能在输入的时间取决于输出,电路的原始状态无关。“也就是说,组合逻辑电路输出电路的历史地位并不重要,电路不包括存储单元。组合逻辑表达方法有三种:真值表,逻辑表达式和电路原理图。在VerilogHDL描述组合逻辑电路中,与真值表对应的是用户自定义原语;而与电路原理图相对应的是门级建模,有个绰号又叫结构化描述;与逻辑表达式相对应的则称为行为描述。

一、逻辑设计(1)组合逻辑设计下面是一些用Verilog进行组合逻辑设计时的一些注意事项:①组合逻辑可以得到两种常用的RTL 级描述方式。第一种是always 模块的触发事件为电平敏感信号列表;第二种就是用assign 关键字描述的数据流赋值语句。②always 模块的敏感表为电平敏感信号的电路可几

扫码关注

扫码关注