- 全部

- 默认排序

今天有小伙伴向老wu咨询了个Capture 16.6的启动异常问题,如下图所示这个问题老wu之前也有遇到过,只是当时没有找到造成该异常的真正原因,所以直接使用了重装操作系统大法解决了。今天再次面对这个启动异常的问题,老wu建议其尝试了清空SPb_data目录,卸载VC 2005运行库之后重装Cad

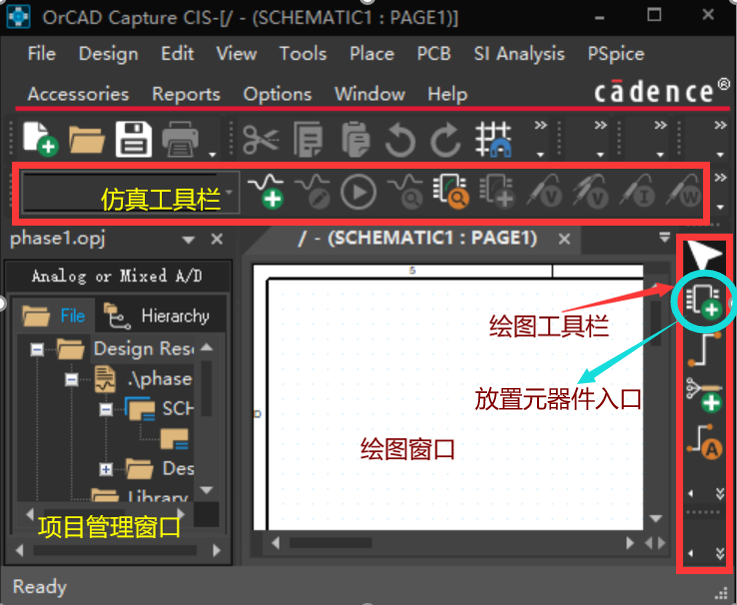

这周让我们从繁杂的模电学习中逃离出来,看看占据中国EDA30%市场份额的巨头公司Cadence带来的原理图仿真工具PSPice的应用。开设新版块的原因 小电最近在给Cadence公司的官方公众号写PCB产品线中原理图仿真部分的教程,感觉不管是针对刚刚开始接触模拟电路的同学,还是已经工作的小

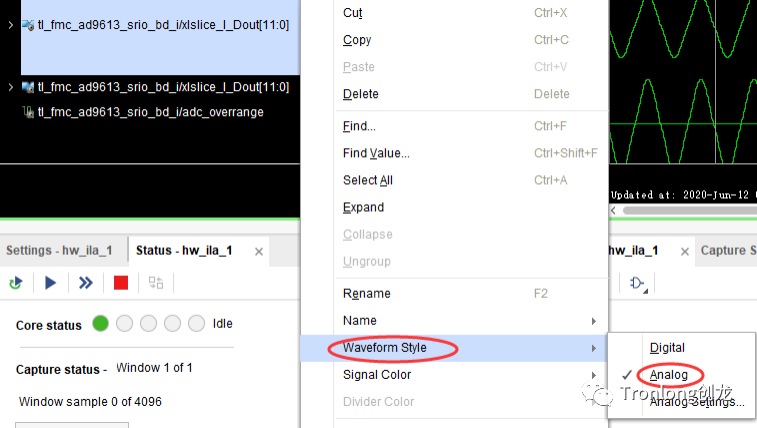

1案例说明1. Kintex-7 FPGA使用SRIO IP核作为Initiator,通过AD9613模块采集AD数据。AD9613采样率为250MSPS,双通道12bit,12bit按照16bit发送,因此数据量为16bit * 2 * 250M = 8Gbps;2. AD数据通过SRIO由Kin

在电子设计领域中,ASIC、FPGA、DSP和MCU是应用最广的常用控制器,它们各具特色,适用于不同场景,扮演着重要角色。本文将简要介绍这四种控制器,希望对小伙伴们有所帮助。1、ASIC(专用集成电路)特点:为特定功能定制,集成度高,成本低

在电子测量领域,许多电子工程师会使用频谱仪来分析信号频率成分,如果想要捕捉微弱信号,必须先确保频谱仪的灵敏度,所以如何做?1、设定中心频率与扫宽根据被测小信号的大致频率范围,精确设置频谱仪的中心频率(CF)和扫描宽度(SPan),确保信号位

在包含DSP(数字信号处理器)和DLP(数字光处理)等精密电子组件的系统中,ESD(静电放电)防护至关重要。以下列出具体的设计策略,旨在有效预防ESD对系统的影响。1、使用专用ESD保护器件在DSP、DLP等敏感组件的输入输出端口,安装专用

AD9280 在时钟(CLK)的驱动下工作,用于控制所有内部转换的周期;AD9280 内置片内采样保持放大器(SHA),同时采用多级差分流水线架构,保证了 32MSPS 的数据转换速率下全温度范围内无失码;AD9280 内部集成了可编程的基准源,根据系统需要也可以选择外部高精度基准满足系统的要求。A

当对allegro软件PCB层叠结构进行设置的时候,某一层可以设置为plane或者conduct,平面层和走线层。但是我发现无论是设置成plane还是conduct,这一层都可以走线,手动铺铜皮,edit-SPlit creat这样去灌铜进行铜皮分割。既然这样,那么设置层的时候,plane和cond

CAP Duplicate Pad Name OnpadSPad Free-1(-53.15mil,0mil) on Multi-Layer And Pad Free-1(-53.15mil,0mil) on Multi-LayerCAP Duplicate Primit

扫码关注

扫码关注