- 全部

- 默认排序

回答网友的问题:逻辑电路设计规则里gate width方向的尺寸一般要求远比feature SIze大,比如28nm的gate width最小也是100nm,间隔也最小80nm,这是出于什么考虑呢?有没有可能跟DRAM工艺那样,也压到fea

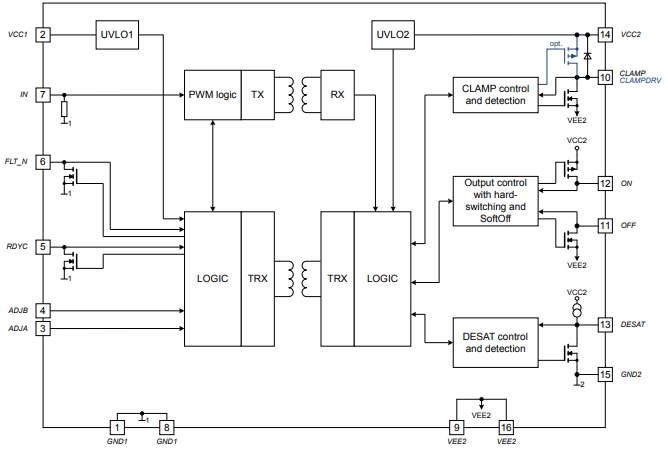

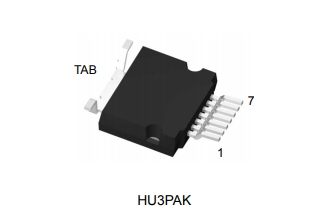

概述EiceDRIVER™增强型X3模拟系列通过外部电阻器(ADJA和ADJB引脚)实现DESAT(可调滤波器时间)和软关闭(可调电流)的配置能力。英飞凌1ED34xx单通道隔离式驱动器具有高达9A输出电流和最大40V输出电源电压,采用节省

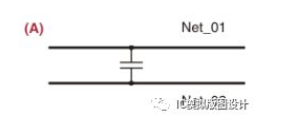

芯片的物理实现过程中不是所有的走线与器件都不是理想的。金属走线与金属走线有重叠有并行。器件也是周围也会有其他器件,或其他走线。最终都会引入额外的电容。就像在电路上额外多出来一些小的电容。无法避免。同样所有导电材料也会有电阻的特性。所以电路中

随着新能源市场的爆发,电动汽车,光伏、储能等下游应用驱动下,碳化硅功率器件迎来了新一轮增长期。特别是电动汽车上SICMOSFET的大规模应用后,在近几年可以看到,国内外各大厂商都密集地加入到SIC的行列中,推出相关产品。国内规模比较大的有华

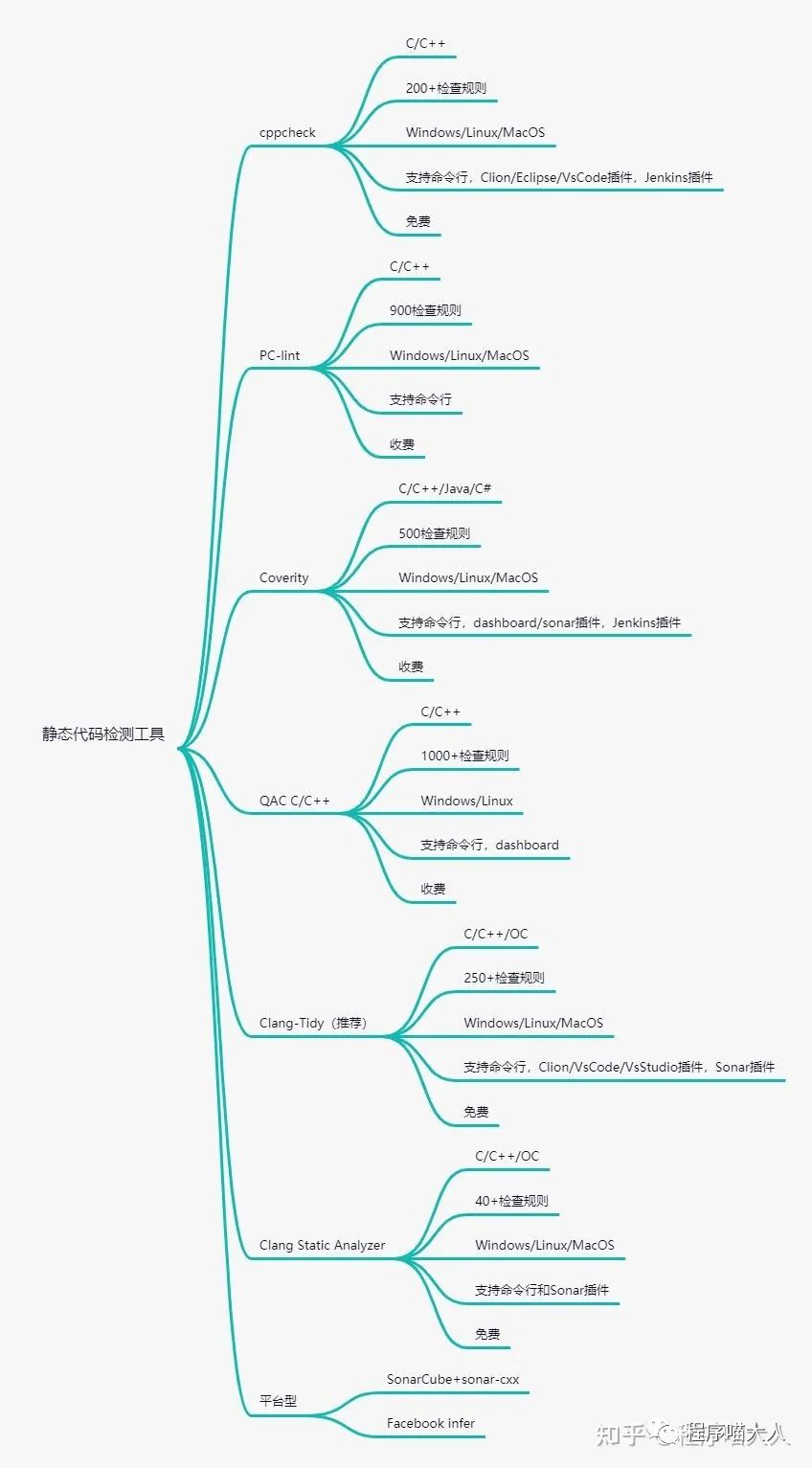

有哪些好用的代码检查工具

CPP静态代码检查工具有很多,具体可以在这个链接中找到:https://link.zhihu.com/?target=https://en.wikipedia.org/wiki/List_of_tools_for_static_code_analySIs#C,_C常用的我都列在了上图,比如cppch

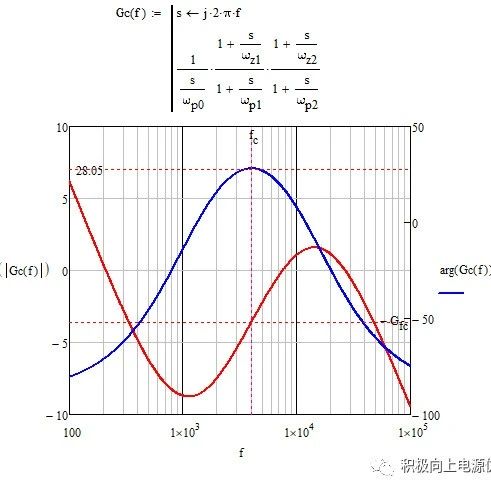

LLC环路设计参考杨波的博士论文《LLC resonant converter》第6章Small SIgnal analySIs of LLC resonant converter。功率级波特图在高于谐振频率时:低于谐振频率时:文章指出,LLC低于谐振频率的小信号特性非常稳定,在该区域有两个极点,因

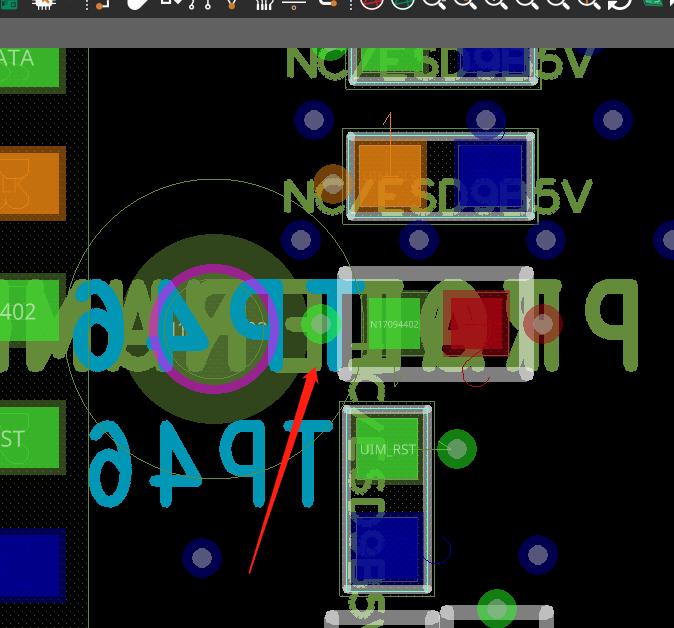

SIM:注意测试点跟器件以及过孔的间距,此处右侧器件可以整体往右边挪动一点:注意铜皮尽量设置动态铜皮,将静态转换下:电感内部挖空掉,在当前层:TF:注意器件之间可以空出点间距留出来扇孔,扇孔不要离焊盘太远:时钟信号包地保全一点,还有 空间可

Altium DeSIgner(AD)作为全球应用最广泛的EDA软件,一直以来是很多电子工程师的PCB设计首选工具,目前随着时代发展已更新到AD 23,下面本文将谈谈AD 23有哪些功能,可以提高PCB设计效率。1、原理图修改图纸大小 双击

1、SCTH100N65G2-7AGSICFET N-CH 650V 95A H2PAK-7这款碳化硅功率MOSFET器件采用先进创新的第二代SIC MOSFET技术开发而成。该器件具有非常低的单位面积导通电阻和非常好的开关性能。开关损耗的

大家过年好,你们的老朋友小Q又回来了,最近一段时间忙于公司项目开发,又加上过年比较忙,所以没能留出时间更新内容,大家是不是有点着急了?公司最近在使用jeeSIte4开发项目,我呢,对这个框架一点也不熟悉,遇到问题都是现查现用。这不,在上传文件与上传图片这直接给卡死了。百度google了好久也没能找到

扫码关注

扫码关注