- 全部

- 默认排序

ESD:Electro-Static discharge的简称,意思是“静电释放”。静电是一种自然现象,通常通过接触、摩擦、电器间感应等方式产生,其特点是长时间积聚、高电压(可以产生几千伏甚至上万伏的静电)、低电量、小电流和作用时间短的特点

EMC:Electro Magnetic Compatibility的简称,也称电磁兼容,各种电气或电子设备在电磁环境复杂的共同空间中,以规定的安全系数满足设计要求的正常工作能力。本章对于 RK3588产品设计中的 ESD/EMI防护设计及

DDR电路简介RK3588 DDR 控制器接口支持 JEDEC SDRAM 标准接口,原理电路16位数据信号如图8-1所示,地址、控制信号如图8-2所示,电源信号如图8-3所示。电路控制器有如下特点:1、兼容 LPDDR4/LPDDR4X/

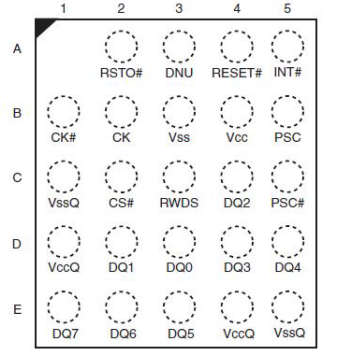

一、HyperFlash NOR 闪存概述S26KS128S(128Mb)HyperFlash™ NOR闪存采用小型 8x6mm 球栅阵列 (BGA) 封装,与 Quad SPI 和双 Quad SPI 部件共享一个共同占位面积,以简化电路

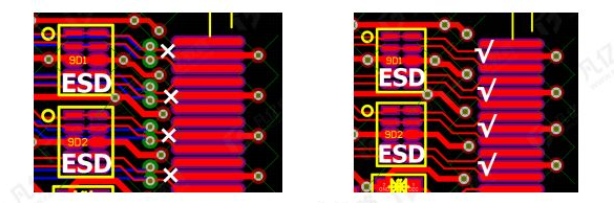

注意器件摆放不要干涉,贴片器件尽量离座子1.5mm2.走线需要优化一下3.差分走线不满足间距要求4.打孔要打在ESD器件前面5.器件摆放尽量中心对齐处理,更美观6.差分锯齿状等长不能超过线距的两倍7.注意差分出线要尽量耦合8.USB差分对内

1.布局应按照先大后小原则布局,大器件打孔连接到小器件再连接到芯片管脚2.有一个数据信号等长不到位3.要保持先后线宽一一致,走线出芯片焊盘后尽快加粗以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接

众所周知,为打压国内半导体行业发展,美国可谓是无所不及,多方位制裁。最近美国在SSD芯片上搞了大举动。近日,美国商务部工业于安全局(BIS)公布法律新规,更新了对三星和SK海力士的一般授权,将这两家公司在华工厂纳入“经验证最终用户(VEUs

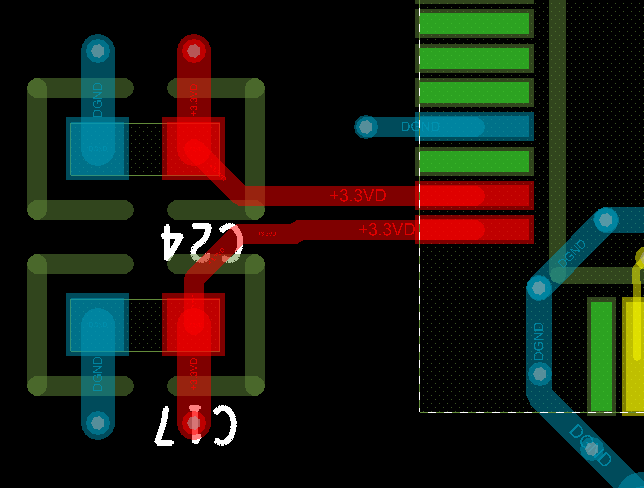

器件尽量整体中心对齐:等长线的gap大于等于3W:地址数据等长误差没什么问题 ,都在误差范围内:其他的基本没什么问题,完成得还可以。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:

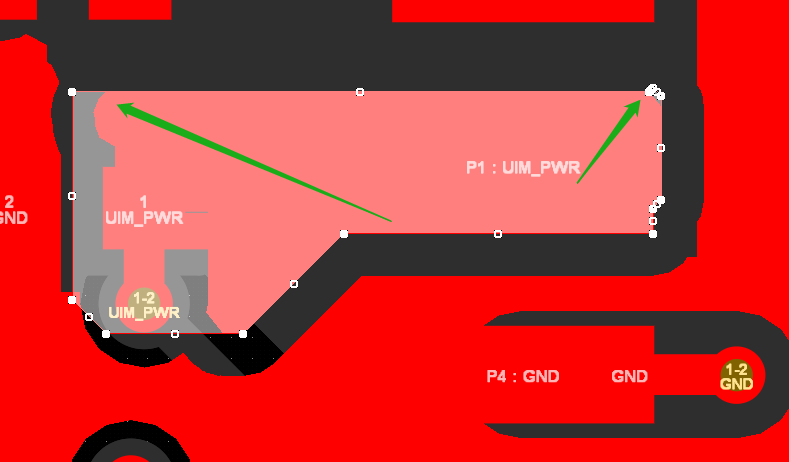

SIM:注意铺铜不要出现直角以及尖角:尽量都钝角铺铜,存在类似情况的自己优化下。此处铺的整板地铜但是并未跟相同网络的地连接:双击铜皮打开属性框,更改连接方式,设置第二项,然后重新灌下铜皮即可连接:多处电源信号并未连接:此处可以直接连接到GN

线宽不一致,导致阻抗不连续走线需要保持3w间距规则地址线分组错误,缺少信号时钟线等长错误电源走线多处没有加粗数据线等长误差控制100mil范围内以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫

扫码关注

扫码关注