- 全部

- 默认排序

提起COB封装,可能很多人不太熟悉,COB封装(Chip-on-Board Package)是一种常用的电子元器件封装技术,功能是将芯片直接安装在PCB上,而并非使用传统的插针、焊脚或表面贴装技术,具有小尺寸、高可靠性和良好的电性能等特点。

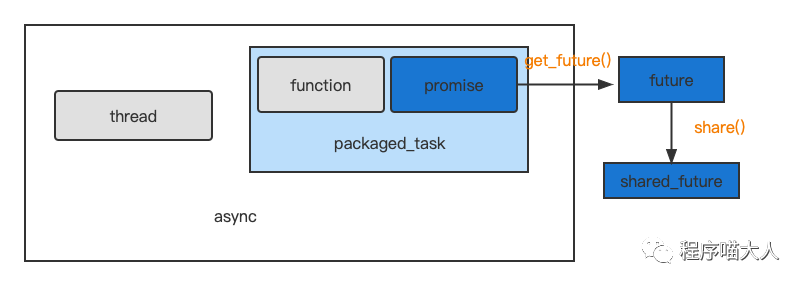

并发编程一般指多线程编程,C 11之后关于多线程编程有几个高级API:std::threadstd::futurestd::shared_futurestd::promisestd::Packaged_taskstd::async可能很多人都搞不清楚它们之前有什么联系,可以直接看这张图:如果连它们

在半导体技术日新月异的今天,封装技术作为链接芯片与外部世界的桥梁,其重要性不言而喻。其中,CSP(Chip Scale Package)封装技术以其极致的小型化特性,成为追求高性能、轻薄化电子产品的首选方案。本文将简短介绍CSP,希望对小伙

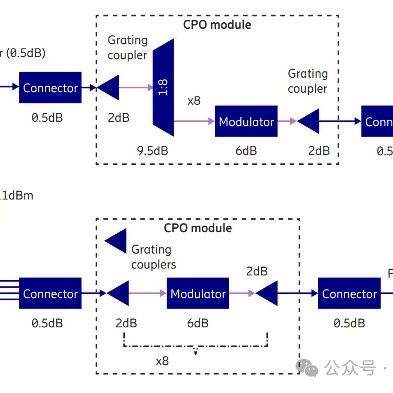

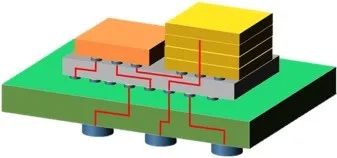

摘要本文回顾了光电共封装(Co-Packaged Optics, CPO)这项新兴技术,以及它在实现高效能、大容量无线接入网络(Radio Access Network, RAN)方面的潜力。CPO 技术可以将光子学和电子学集成在一个组件中,将互连损耗降到最低。在概述 CPO 的关键概念、光学集成方

在今年的 IMAPS(International Microelectronics Assembly and Packaging Society,国际微电子装配与封装学会 )大会上,Cadence 资深半导体封装管理总监 John Park 发表了关于封装组装设计套件(Package Assemb

常见的芯片(IC)封装包括以下几种:Dual In-line Package (DIP):双列直插封装,是最早的IC封装形式之一,引脚呈“直排”式,适用于手工焊接。Quad Flat Package (QFP):四角平封装,引脚呈“平排”式

DIP(Dual Inline Package,双列直插式封装)是一种常见的电子元件封装形式。这种封装技术具有以下特点:封装结构:DIP封装有两个平行的引脚列,通常引脚数量从8到64不等,引脚间距一般为2.54毫米(0.1英寸)。这种设计使

有大神遇到过Package keepin层删不掉的情况吗?file:///一直显示Selected item not valid for current operation, ignored: Rectangle "Package Keepin/All"No valid items selected

17.4和17.2不一样吗?按照视频讲解的去做 按住ctrl 选中的管脚会拖动 而且我进入这个Package里面这个Package properties是无法点击的 也不像视频说的双击左键会出来 属性框

全站最新内容推荐

- 1加码技术,打破困境,PSPice电路仿真助你解锁职场新高度!

- 2简谈稳压二极管和普通二极管的区别

- 3贴片元件如何拆卸及焊接?

- 4盘点电子工程师必须了解的21个电路

- 5英伟达GB300芯片受阻,存在过热问题

- 6WARELEO李增原创H04课程大纲的安排课程中内容及工具及课程的重点学习办法的讲解

- 7WARELEO李增原创H03根据自己的关注知识点和所需要的知识来选择需要的图书包邮递

- 8WARELEO李增原创H02理工男生李老师的介绍从51单片机驱动到FPGA到仿真设计之路

- 9WARELEO李增原创H01信号电源完整性设计与HFSS射频天线设计仿真验证研修课程主题

- 10WARELEO李增:反射仿真的信号观察办法及时域串扰的仿真设置及观察技巧

扫码关注

扫码关注