- 全部

- 默认排序

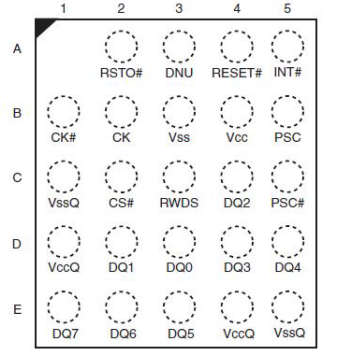

一、HyperFlash NOR 闪存概述S26KS128S(128Mb)HyperFlash™ NOR闪存采用小型 8x6mm 球栅阵列 (BGA) 封装,与 Quad SPI 和双 Quad SPI 部件共享一个共同占位面积,以简化电路

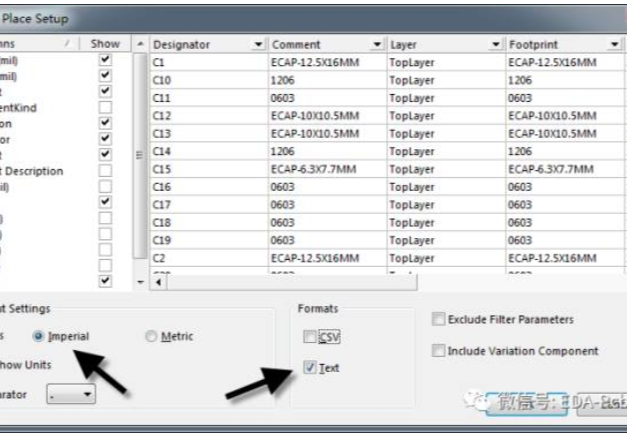

怎么导出坐标和利用坐标快速布局?答:器件的坐标其实在我们处理布局的时候,非常有用,例如A板布局导入B板。1、在A板PCB中执行菜单命令“File-Assembly-Generates PIck and Place File”对器件的坐标进行

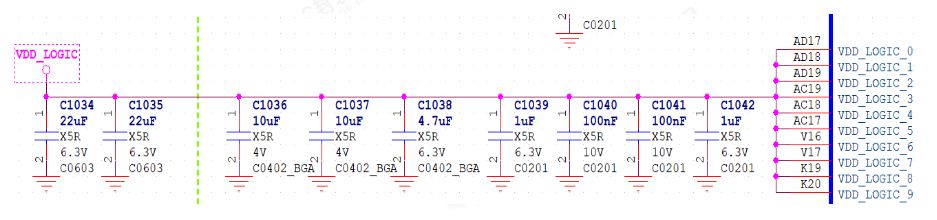

RK3588 VDD_LOGIC电源PCB设计1、VDD_LOGIC的覆铜宽度需满足芯片的电流需求,连接到芯片电源管脚的覆铜足够宽,路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚路径都足够。2、如图1所示,原理

1、VDD_NPU的覆铜宽度需满足芯片的电流需求,连接到芯片电源管脚的覆铜足够宽,路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚的路径都足够。2、VDD_NPU的电源在外围换层时,要尽可能的多打电源过孔(7个以

RK3588 VDD_CPU_LIT电源PCB设计1、VDD_CPU_LIT覆铜宽度需满足芯片电流需求,连接到芯片电源管脚的覆铜足够宽,路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚的路径都足够。2、VDD_C

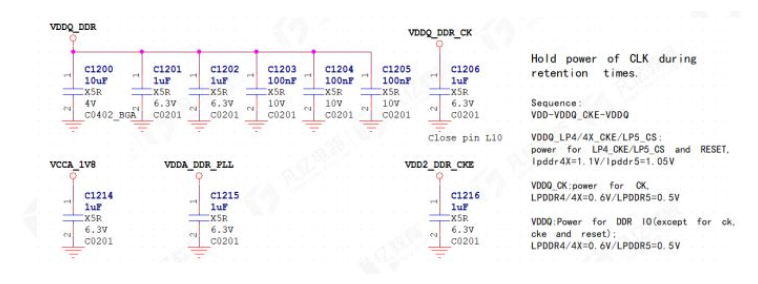

RK3588 VCC_DDR电源PCB设计1、VCC_DDR覆铜宽度需满足芯片的电流需求,连接到芯片电源管脚的覆铜足够宽,路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚的路径都足够。2、VCC_DDR的电源在外

随着电子设备的复杂性和集成度越来越高,PCB多层板应用频率越来越高,是许多电子工程师的关键技能,多层板设计涉及到一系列复杂问题,如SI&PI、电源分布、热设计等。如果新手工程师想学习多层板的堆叠设计该如何做?1、多层板堆叠设计的基础知识①层

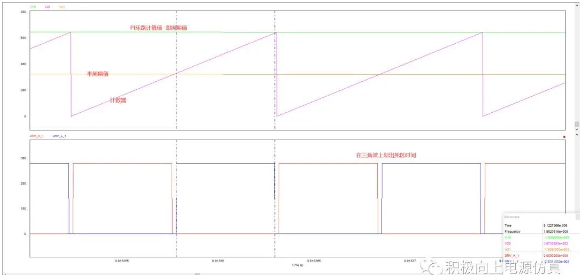

前面介绍过模拟VCO是通过改变电容充放电电流的大小实现调频的,详见LLC闭环仿真之L6599 VCO建模与工作原理分析。那么数字环路该怎么实现呢?今天使用PSIM的C Block分享一下。以前沿调制为例,如下图:每个中断周期内,软件通过环路

ORCAD17.4原理图检查 电气规则检查参数设置ØCheck single node nets:检查设计中的单端网络;ØCheck no driving source and PIn type conflicts:检查器件属性无源管脚与有源管脚的连接是否正确;ØCheck dup

一、W25M02GW1.8V 2G位(2 X 1G位)串行SLC NAND闪存1、简介:W25M02GW(2 X 1G位)串行MCP(多芯片封装)闪存基于W25N串行SLC NAND SPIFlash®系列,将两个单独的W25N01GW芯片

扫码关注

扫码关注