- 全部

- 默认排序

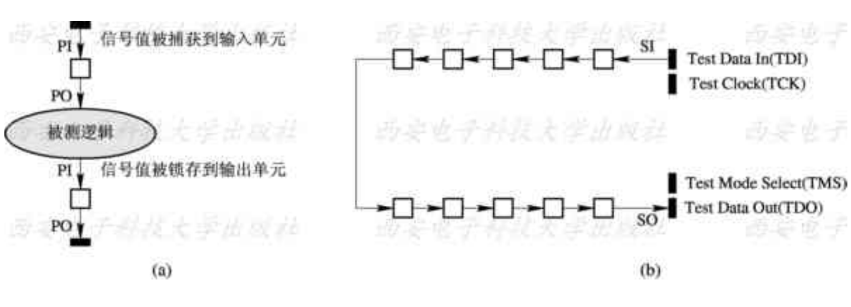

在IC设计阶段,为保证所设计的产品顺利上市,具有更高的竞争力,很多工程师会进行可测性设计确保无误,其中常用的方法莫过于基于JTAG的可测性设计,今天就给小伙伴们科普基于JTAG的可测性设计,希望能帮上忙。JTAG,也叫做边界扫描BSD,最初

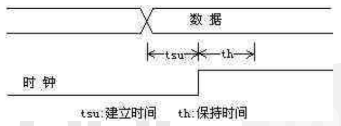

小白初学数字IC设计,经常会碰到建立时间和保持时间两个基本概念,虽然很好理解它们的定义,但在实践操作时很难运用,导致动手操作一团糟,所以今天讲讲建立时间(setuptime)和保持时间(holdtime),以及它们的运用方式。如图所示,一般

在数字IC系统设计时,触发器若是设计不当很容易出现,但很多小白都不知道触发器发生亚稳态后的输出情况,所以今天就讲讲,希望对小伙伴们有所帮助。一般来说,若数字系统只存在逻辑,那么工程师也就不会面临可靠性的问题,然而、实际上,所有逻辑电路处理的

在现代IC设计中,复位电路是至关重要的组成部分,可保证芯片在通电或复位信号到来时,IC系统处于可控状态,从而避免不可预测的行为,按照信号类型,复位电路可分为异步复位和同步复位,下面将介绍它们之间的区别及应用。异步复位是通过一个异步信号来实现

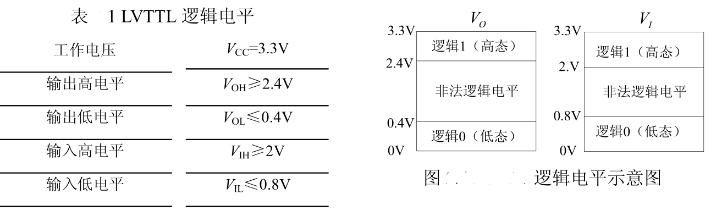

在集成电路(IC)领域里,按照其频率可将IC分为模拟IC和数字IC,尽管这两者都涉及电子元件和电路的设计,但它们在设计方法、工作原理和关键技术等存在很多差别,本文将谈谈它们的区别及注意事项。1、设计方法及工作原理①模拟IC设计模拟电路设计主

采样电路是电子系统中常见的关键组成部分,可用于从连续模拟信号中提取离散样本,在很多电子系统或产品中起到很重要的作用,如数据转换、信号处理和测量等。下面聊聊如何设计出优秀的采样电路。1、采样电路的作用是什么?①信号提取采样电路通过周期性采样,

在IC设计中,如何在合适的流程里使用EDA工具,对电子工程师来说是难题,从前端设计到后端实现,电子工程师需要依赖各种EDA工具来完成不同的任务,那么你知道IC设计每个流程阶段使用哪些工具吗?1、前端设计阶段前端设计阶段主要涉及到芯片的功能定

随着无线通信技术高速发展,现阶段已发展至5G建设初中期,5G网络已在全球多国开始普及推广,业界预测,2030年将迈入6G时代,也将对IC设计提出更高的要求,如何应对未来的IC设计已成为很多工程师发愁的问题。或许是德科技新发布的EDA工具可以

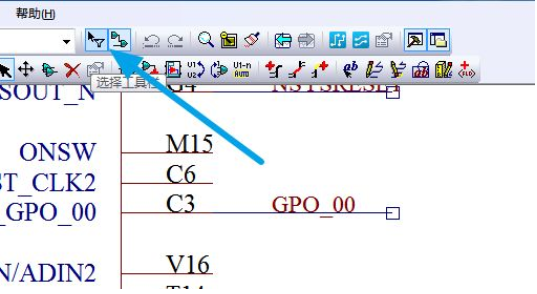

PADS Logic提供类似于Windows的查找功能,可以进行器件的查找。(1)在LogIC设计界面中,将菜单显示中的“选择工具栏”进行打开,如图1所示,会弹出对应的“选择工具栏”的分栏菜单选项,如图2所示。 图 1 “选择工具栏

在电子工程领域内,集成电路(IC)是不可或缺的核心组件,然而由于电子市场竞争激烈,部分厂商为降低成本及缩短开发时间,选择在IC设计及制造过程中采取不当措施,导致IC上市后性能急速下降,存在稳定性问题甚至安全隐患,所以工程师必须学会判断和辨别

扫码关注

扫码关注